集成电路芯片验证方法、装置、电子设备及存储介质与流程

1.本公开涉及人工智能技术领域,特别涉及人工智能芯片以及云计算等领域的集成电路芯片验证方法、装置、电子设备及存储介质。

背景技术:

2.随机化数据激励对于集成电路芯片(ic,integrated circuit)验证来说非常重要,所述芯片可为语音芯片等。

3.目前,主流的ic验证平台通常都是基于system verilog搭建的,system verilog即指sv语言,是一种硬件描述和验证语言,而system verilog平台只提供针对定点(整型)数据的随机化方法,未提供针对浮点数据的随机化方法。

技术实现要素:

4.本公开提供了集成电路芯片验证方法、装置、电子设备及存储介质。

5.一种集成电路芯片验证方法,包括:

6.获取第一参数和第二参数,所述第一参数为要求的浮点数取值上限,所述第二参数为要求的浮点数取值下限;

7.根据所述第一参数和所述第二参数分别生成随机化的浮点数的第一符号位、第一指数位和第一小数位;

8.根据所述第一符号位、所述第一指数位以及所述第一小数位生成所述浮点数;

9.利用所述浮点数进行集成电路芯片验证。

10.一种集成电路芯片验证装置,包括:参数获取模块、第一生成模块、第二生成模块以及验证模块;

11.所述参数获取模块,用于获取第一参数和第二参数,所述第一参数为要求的浮点数取值上限,所述第二参数为要求的浮点数取值下限;

12.所述第一生成模块,用于根据所述第一参数和所述第二参数分别生成随机化的浮点数的第一符号位、第一指数位和第一小数位;

13.所述第二生成模块,用于根据所述第一符号位、所述第一指数位以及所述第一小数位生成所述浮点数;

14.所述验证模块,用于利用所述浮点数进行集成电路芯片验证。

15.一种电子设备,包括:

16.至少一个处理器;以及

17.与所述至少一个处理器通信连接的存储器;其中,

18.所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述至少一个处理器执行,以使所述至少一个处理器能够执行如以上所述的方法。

19.一种存储有计算机指令的非瞬时计算机可读存储介质,所述计算机指令用于使计算机执行如以上所述的方法。

20.一种计算机程序产品,包括计算机程序/指令,所述计算机程序/指令被处理器执行时实现如以上所述的方法。

21.上述公开中的一个实施例具有如下优点或有益效果:可实现浮点数据的随机化,从而为集成电路芯片验证中相关运算单元的验证提供了所需的浮点数据激励,进而提升了验证效果等。

22.应当理解,本部分所描述的内容并非旨在标识本公开的实施例的关键或重要特征,也不用于限制本公开的范围。本公开的其它特征将通过以下的说明书而变得容易理解。

附图说明

23.附图用于更好地理解本方案,不构成对本公开的限定。其中:

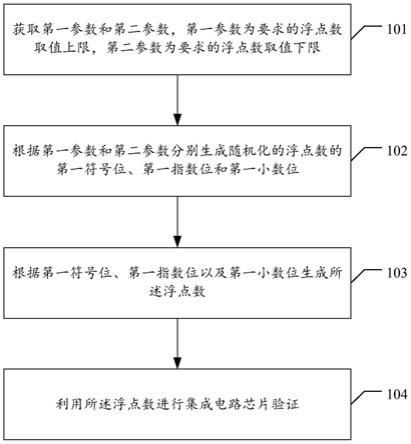

24.图1为本公开所述集成电路芯片验证方法实施例的流程图;

25.图2为本公开所述按照第一生成方式生成第一符号位、第一指数位以及第一小数位的过程示意图;

26.图3为本公开所述按照第二生成方式生成第一符号位、第一指数位以及第一小数位的过程示意图;

27.图4为本公开所述按照第三生成方式生成第一符号位、第一指数位以及第一小数位的过程示意图;

28.图5为本公开所述集成电路芯片验证装置第一实施例500的组成结构示意图;

29.图6为本公开所述集成电路芯片验证装置第二实施例600的组成结构示意图;

30.图7示出了可以用来实施本公开的实施例的电子设备700的示意性框图。

具体实施方式

31.以下结合附图对本公开的示范性实施例做出说明,其中包括本公开实施例的各种细节以助于理解,应当将它们认为仅仅是示范性的。因此,本领域普通技术人员应当认识到,可以对这里描述的实施例做出各种改变和修改,而不会背离本公开的范围和精神。同样,为了清楚和简明,以下的描述中省略了对公知功能和结构的描述。

32.另外,应理解,本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,一般表示前后关联对象是一种“或”的关系。

33.图1为本公开所述集成电路芯片验证方法实施例的流程图。如图1所示,可包括以下具体实现步骤。

34.在步骤101中,获取第一参数和第二参数,第一参数为要求的浮点数取值上限,第二参数为要求的浮点数取值下限。

35.在步骤102中,根据第一参数和第二参数分别生成随机化的浮点数的第一符号位、第一指数位和第一小数位。

36.在步骤103中,根据第一符号位、第一指数位以及第一小数位生成所述浮点数。

37.在步骤104中,利用所述浮点数进行集成电路芯片验证。

38.可以看出,采用上述方法实施例所述方案,可实现浮点数据的随机化,从而为集成电路芯片验证中相关运算单元的验证提供了所需的浮点数据激励,进而提升了验证效果

等。

39.浮点数据可包括浮点数和浮点数矢量。浮点数可由符号位(sign)、指数位(exponent)和小数位(fraction)组成。

40.为与后续出现的其它符号位、指数位和小数位进行区分,将随机化的浮点数的符号位、指数位和小数位分别称为第一符号位、第一指数位和第一小数位,后续类似情况不再赘述。

41.本公开所述方案中,得到的浮点数需要位于约束的数据范围内,即用户可以设置需要约束随机化生成的浮点数的取值范围,最终返回符合约束条件的浮点数。

42.相应地,可设定第一参数和第二参数,其中,第一参数为要求的浮点数取值上限,第二参数为要求的浮点数取值下限。

43.本公开所述方式中,可根据第一参数和第二参数分别生成随机化的浮点数的第一符号位、第一指数位和第一小数位。本公开的一个实施例中,可分别获取第一参数的第二符号位、第二指数位以及第二小数位,并分别获取第二参数的第三符号位、第三指数位以及第三小数位,进而可根据获取到的第二符号位、第二指数位、第二小数位、第三符号位、第三指数位以及第三小数位,生成所述浮点数的第一符号位、第一指数位以及第一小数位。

44.其中,可分别用sign_max、exp_max和frac_max来表示第一参数的第二符号位、第二指数位和第二小数位,分别用sign_min、exp_min和frac_min来表示第二参数的第三符号位、第三指数位和第三小数位,并可用sign_result、exp_result和frac_result来表示所述浮点数的第一符号位、第一指数位以及第一小数位。

45.本公开的一个实施例中,若第二符号位和第三符号位均等于0,可按照第一生成方式生成第一符号位、第一指数位以及第一小数位,若第二符号位等于0,且第三符号位等于1,可按照第二生成方式生成第一符号位、第一指数位以及第一小数位,若第二符号位等于1,且第三符号位等于1,可按照第三生成方式生成第一符号位、第一指数位以及第一小数位。

46.也就是说,可将第二符号位和第三符号位进行比较,根据比较结果的不同,可分别采用对应的生成方式来生成第一符号位、第一指数位以及第一小数位,从而使得所述生成更具针对性,进而提升了生成结果的准确性等。

47.若sign_max==1且sign_min==0时,代表第一参数的符号为负,第二参数的符号为正,这种情况下是无法得到符合约束条件的浮点数的,相应地,可报错退出,若sign_max==0且sign_min==0,可按照第一生成方式生成第一符号位、第一指数位以及第一小数位,若sign_max==0且sign_min==1,可按照第二生成方式生成第一符号位、第一指数位以及第一小数位,若sign_max==1且sign_min==1,可按照第三生成方式生成第一符号位、第一指数位以及第一小数位。

48.以下分别对上述第一生成方式、第二生成方式以及第三生成方式的具体实现进行介绍。

49.1)第一生成方式

50.本公开的一个实施例中,按照第一生成方式生成第一符号位、第一指数位以及第一小数位的方式可包括:若第二指数位等于第三指数位,且第二小数位大于或等于第三小数位,则将0作为第一符号位,将第二指数位或第三指数位作为第一指数位,将位于[第三小

数位:第二小数位]范围内的随机值作为第一小数位。

[0051]

另外,本公开的一个实施例中,按照第一生成方式生成第一符号位、第一指数位以及第一小数位的方式还可包括:若第二指数位大于第三指数位,则生成位于[第三指数位:第二指数位]范围内的随机值,作为第一中间变量;若第一中间变量等于第三指数位,则将0作为第一符号位,将第三指数位作为第一指数位,将位于[第三小数位:第一预定值]范围内的随机值作为第一小数位;若第一中间变量等于第二指数位,则将0作为第一符号位,将第二指数位作为第一指数位,将位于[第二预定值:第二小数位]范围内的随机值作为第一小数位;若第一中间变量既不等于第三指数位,也不等于第二指数位,则将0作为第一符号位,将第一中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0052]

基于上述介绍,图2为本公开所述按照第一生成方式生成第一符号位、第一指数位以及第一小数位的过程示意图。如图2所示,可包括以下具体实现步骤。

[0053]

在步骤201中,将exp_max与exp_min进行比较,若exp_max《exp_min,则执行步骤202,若exp_max==exp_min,则执行步骤203,若exp_max》exp_min,则执行步骤205。

[0054]

在步骤202中,报错退出,之后结束流程。

[0055]

当前sign_max==0且sign_min==0,代表第一参数和第二参数的符号均为正,那么若exp_max《exp_min,则代表第一参数的指数部分小于第二参数的指数部分,这种情况下是无法得到符合约束条件的浮点数的,相应地,可报错退出。

[0056]

在步骤203中,确定是否frac_max《frac_min,若是,则执行步骤202,否则,执行步骤204。

[0057]

当前sign_max==0且sign_min==0,且exp_max==exp_min,若frac_max《frac_min,则代表第一参数和第二参数的符号均为正,且第一参数和第二参数的指数部分相等,但第一参数的小数部分小于第二参数的小数部分,这种情况下是无法得到符合约束条件的浮点数的,相应地,可报错退出。

[0058]

在步骤204中,将0作为sign_result,将exp_max或exp_min作为exp_result,将位于[frac_min:frac_max]范围内的随机值作为frac_result,之后结束流程。

[0059]

即有:sign_result=0;

[0060]

exp_result=exp_max或exp_min;

[0061]

frac_result=random([frac_min:frac_max]);

[0062]

其中,可利用system verilog平台提供的随机化方法,生成位于[frac_min:frac_max]范围内的随机值,作为frac_result。

[0063]

在步骤205中,生成位于[exp_min:exp_max]范围内的随机值,作为第一中间变量tmp1。

[0064]

可利用system verilog平台提供的随机化方法,生成位于[exp_min:exp_max]范围内的随机值,作为第一中间变量tmp1,即tmp1=random([exp_min:exp_max])。

[0065]

在步骤206中,将tmp1与exp_min和exp_max进行比较,若tmp1==exp_min,则执行步骤207,若tmp1==exp_max,则执行步骤208,否则,执行步骤209。

[0066]

在步骤207中,将0作为sign_result,将exp_min作为exp_result,将位于[frac_min:第一预定值]范围内的随机值作为frac_result,之后结束流程。

[0067]

第一预定值的具体取值可根据实际需要而定,比如,可为

‘

h7f_ffff。

[0068]

那么即有:sign_result=0;

[0069]

exp_result=exp_min;

[0070]

frac_result=random([frac_min:

‘

h7f_ffff]);

[0071]

其中,可利用system verilog平台提供的随机化方法,生成位于[frac_min:

‘

h7f_ffff]范围内的随机值,作为frac_result。

[0072]

在步骤208中,将0作为sign_result,将exp_max作为exp_result,将位于[第二预定值:frac_max]范围内的随机值作为frac_result,之后结束流程。

[0073]

第二预定值的具体取值可根据实际需要而定,比如,可为

‘

h0。

[0074]

那么即有:sign_result=0;

[0075]

exp_result=exp_max;

[0076]

frac_result=random([

‘

h0:frac_max]);

[0077]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:frac_max]范围内的随机值,作为frac_result。

[0078]

在步骤209中,将0作为sign_result,将tmp1作为exp_result,将位于[第二预定值:第一预定值]范围内的随机值作为frac_result,之后结束流程。

[0079]

即有:sign_result=0;

[0080]

exp_result=tmp1;

[0081]

frac_result=random([

‘

h0:

‘

h7f_ffff]);

[0082]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:

‘

h7f_ffff]范围内的随机值,作为frac_result。

[0083]

在获取到第一符号位、第一指数位和第一小数位之后,可根据这些信息生成所需的浮点数,即可根据获取到的sign_result、exp_result和frac_result,生成符合约束条件的随机化的浮点数,如何生成为现有技术。

[0084]

2)第二生成方式

[0085]

本公开的一个实施例中,按照第二生成方式生成第一符号位、第一指数位以及第一小数位的方式可包括:生成位于[0:1]范围内的随机值,作为第二中间变量,若第二中间变量等于0,则生成位于[0:第二指数位]范围内的随机值,作为第三中间变量;若第三中间变量等于第二指数位,则将0作为第一符号位,将第二指数位作为第一指数位,将位于[第二预定值:第二小数位]范围内的随机值作为第一小数位;若第三中间变量不等于第二指数位,则将0作为第一符号位,将第三中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0086]

另外,本公开的一个实施例中,按照第二生成方式生成第一符号位、第一指数位以及第一小数位的方式还可包括:若第二中间变量不等于0,则生成位于[0:第三指数位]范围内的随机值,作为第四中间变量;若第四中间变量等于第三指数位,则将1作为第一符号位,将第三指数位作为第一指数位,将位于[第二预定值:第三小数位]范围内的随机值作为第一小数位;若第四中间变量不等于第三指数位,则将1作为第一符号位,将第四中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0087]

基于上述介绍,图3为本公开所述按照第二生成方式生成第一符号位、第一指数位

以及第一小数位的过程示意图。如图3所示,可包括以下具体实现步骤。

[0088]

在步骤301中,生成位于[0:1]范围内的随机值,作为第二中间变量tmp2。

[0089]

当前sign_max==0且sign_min==1,代表第一参数的符号为正,第二参数的符号为负,可首先利用system verilog平台提供的随机化方法,生成位于[0:1]范围内的随机值,作为第二中间变量tmp2,即有:tmp2=random([0:1])。

[0090]

在步骤302中,确定是否tmp2==0,若是,则执行步骤303,否则,执行步骤307。

[0091]

在步骤303中,生成位于[0:exp_max]范围内的随机值,作为第三中间变量tmp3。

[0092]

即有:tmp3=random([0:exp_max]);

[0093]

其中,可利用system verilog平台提供的随机化方法,生成位于[0:exp_max]范围内的随机值。

[0094]

在步骤304中,确定是否tmp3==exp_max,若是,则执行步骤305,否则,执行步骤306。

[0095]

在步骤305中,将0作为sign_result,将exp_max作为exp_result,将位于[第二预定值:frac_max]范围内的随机值作为frac_result,之后结束流程。

[0096]

即有:sign_result=0;

[0097]

exp_result=exp_max;

[0098]

frac_result=random([

‘

h0:frac_max]);

[0099]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:frac_max]范围内的随机值。

[0100]

在步骤306中,将0作为sign_result,将tmp3作为exp_result,将位于[第二预定值:第一预定值]范围内的随机值作为frac_result,之后结束流程。

[0101]

即有:sign_result=0;

[0102]

exp_result=tmp3;

[0103]

frac_result=random([

‘

h0:

‘

h7f_ffff]);

[0104]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:

‘

h7f_ffff]范围内的随机值。

[0105]

在步骤307中,生成位于[0:exp_min]范围内的随机值,作为第四中间变量tmp4。

[0106]

可利用system verilog平台提供的随机化方法,生成位于[0:exp_min]范围内的随机值,即有:exp_tmp=random([0:exp_min])。

[0107]

在步骤308中,确定是否tmp4==exp_min,若是,则执行步骤309,否则,执行步骤310。

[0108]

在步骤309中,将1作为sign_result,将exp_min作为exp_result,将位于[第二预定值:frac_min]范围内的随机值作为frac_result,之后结束流程。

[0109]

即有:sign_result=1;

[0110]

exp_result=exp_min;

[0111]

frac_result=random([

‘

h0:frac_min]);

[0112]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:frac_min]范围内的随机值。

[0113]

在步骤310中,将1作为sign_result,将tmp4作为exp_result,将位于[第二预定

值:第一预定值]范围内的随机值作为frac_result,之后结束流程。

[0114]

即有:sign_result=1;

[0115]

exp_result=tmp4;

[0116]

frac_result=random([

‘

h0:

‘

h7f_ffff]);

[0117]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:

‘

h7f_ffff]范围内的随机值。

[0118]

在获取到第一符号位、第一指数位和第一小数位之后,可根据这些信息生成所需的浮点数,即可根据获取到的sign_result、exp_result和frac_result,生成符合约束条件的随机化的浮点数。

[0119]

3)第三生成方式

[0120]

本公开的一个实施例中,按照第三生成方式生成第一符号位、第一指数位以及第一小数位的方式可包括:若第二指数位等于第三指数位,且第二小数位小于或等于第三小数位,则将1作为第一符号位,将第二指数位或第三指数位作为第一指数位,将位于[第二小数位:第三小数位]范围内的随机值作为第一小数位。

[0121]

另外,本公开的一个实施例中,按照第三生成方式生成第一符号位、第一指数位以及第一小数位的方式还可包括:若第二指数位大于第三指数位,则生成位于[第二指数位:第三指数位]范围内的随机值,作为第五中间变量;若第五中间变量等于第三指数位,则将1作为第一符号位,将第三指数位作为第一指数位,将位于[第二预定值:第三小数位]范围内的随机值作为第一小数位;若第五中间变量等于第二指数位,则将1作为第一符号位,将第二指数位作为第一指数位,将位于[第二小数位:第一预定值]范围内的随机值作为第一小数位;若第五中间变量既不等于第三指数位,也不等于第二指数位,则将1作为第一符号位,将第五中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0122]

基于上述介绍,图4为本公开所述按照第三生成方式生成第一符号位、第一指数位以及第一小数位的过程示意图。如图4所示,可包括以下具体实现步骤。

[0123]

在步骤401中,将exp_max与exp_min进行比较,若exp_max》exp_min,则执行步骤402,若exp_max==exp_min,则执行步骤403,若exp_max《exp_min,则执行步骤405。

[0124]

在步骤402中,报错退出,之后结束流程。

[0125]

当前sign_max==1且sign_min==1,代表第一参数和第二参数的符号均为负,那么若exp_max》exp_min,则代表第一参数的指数部分大于第二参数的指数部分,这种情况下是无法得到符合约束条件的浮点数的,相应地,可报错退出。

[0126]

在步骤403中,确定是否frac_max》frac_min,若是,则执行步骤402,否则,执行步骤404。

[0127]

当前sign_max==1且sign_min==1,且exp_max==exp_min,若frac_max》frac_min,则代表第一参数和第二参数的符号均为负,且第一参数和第二参数的指数部分相等,但第一参数的小数部分大于第二参数的小数部分,这种情况下是无法得到符合约束条件的浮点数的,相应地,可报错退出。

[0128]

在步骤404中,将1作为sign_result,将exp_max或exp_min作为exp_result,将位于[frac_max:frac_min]范围内的随机值作为frac_result,之后结束流程。

[0129]

即有:sign_result=1;

[0130]

exp_result=exp_max或exp_min;

[0131]

frac_result=random([frac_max:frac_min]);

[0132]

其中,可利用system verilog平台提供的随机化方法,生成位于[frac_max:frac_min]范围内的随机值。

[0133]

在步骤405中,生成位于[exp_max:exp_min]范围内的随机值,作为第五中间变量tmp5。

[0134]

可利用system verilog平台提供的随机化方法,生成位于[exp_max:exp_min]范围内的随机值,作为第五中间变量tmp5,即有:tmp5=random([exp_max:exp_min])。

[0135]

在步骤406中,将tmp5与exp_min和exp_max进行比较,若tmp5==exp_min,则执行步骤407,若tmp5==exp_max,则执行步骤408,否则,执行步骤409。

[0136]

在步骤407中,将1作为sign_result,将exp_min作为exp_result,将位于[第二预定值:frac_min]范围内的随机值作为frac_result,之后结束流程。

[0137]

即有:sign_result=1;

[0138]

exp_result=exp_min;

[0139]

frac_result=random([

‘

h0:frac_min]);

[0140]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:frac_min]范围内的随机值。

[0141]

在步骤408中,将1作为sign_result,将exp_max作为exp_result,将位于[frac_max:第一预定值]范围内的随机值作为frac_result,之后结束流程。

[0142]

即有:sign_result=1;

[0143]

exp_result=exp_max;

[0144]

frac_result=random([frac_max:

‘

h7f_ffff]);

[0145]

其中,可利用system verilog平台提供的随机化方法,生成位于[frac_max:

‘

h7f_ffff]范围内的随机值。

[0146]

在步骤409中,将1作为sign_result,将tmp5作为exp_result,将位于[第二预定值:第一预定值]范围内的随机值作为frac_result,之后结束流程。

[0147]

即有:sign_result=1;

[0148]

exp_result=tmp5;

[0149]

frac_result=random([

‘

h0:

‘

h7f_ffff]);

[0150]

其中,可利用system verilog平台提供的随机化方法,生成位于[

‘

h0:

‘

h7f_ffff]范围内的随机值,作为frac_result。

[0151]

在获取到第一符号位、第一指数位和第一小数位之后,可根据这些信息生成所需的浮点数,即可根据获取到的sign_result、exp_result和frac_result,生成符合约束条件的随机化的浮点数。

[0152]

无论通过上述哪种方式,均可实现浮点数据的随机化,从而为相关运算单元的验证提供了所需的浮点数据激励,进而提升了验证效果等。

[0153]

本公开所述方案中,除了可生成浮点数外,还可生成浮点数矢量,相应地,还可利用浮点数矢量进行集成电路芯片验证。本公开的一个实施例中,可根据所述浮点数生成指

定长度的随机化的浮点数矢量,从而丰富了所生成的浮点数据类型,进而进一步提升了验证效果等。

[0154]

用户可设置约束随机化生成的浮点数矢量的长度,另外,还可指定随机化约束的线性运算类型,所述线性运算必须是system verilog平台支持的对数组元素的运算操作,而且,浮点数矢量中的数据单元经过所述线性运算之后,运算结果需要位于指定的数据范围内,即运算结果需要位于指定的上限和下限之间,最终返回的是符合约束条件的浮点数矢量,其中的数据单元个数为len,len表示所述指定长度。

[0155]

可首先按照本公开所述方式生成一个随机化的浮点数,其中的符号位、指数位和小数位分别称为第一符号位、第一指数位和第一小数位,之后,可根据所述浮点数生成随机化的浮点数矢量。

[0156]

本公开的一个实施例中,根据所述浮点数生成随机化的浮点数矢量的方式可包括:若第一指数位等于0,则获取所述浮点数与预定的第一因子的乘积,得到第六中间变量;获取随机化的整型数据的第一数组,第一数组的长度等于所述指定长度,且对第一数组进行预定的线性运算后得到的结果为第六中间变量;将第一因子平均分配到第一数组中的各元素中,并结合线性运算的类型确定出浮点数矢量。

[0157]

本公开的一个实施例中,若线性运算为加法运算,可将第一数组中的各元素分别除以第一因子,得到浮点数矢量,若线性运算为乘法运算,可从第一数组中随机选取m个元素,并可将选取出的各元素分别除以2,利用除以2后的m个元素组成第二数组,进而可将第二数组中的各元素分别除以2的n次方,得到浮点数矢量,其中,n为用第三预定值除以所述指定长度后得到的商,m为用第三预定值除以所述指定长度后得到的余数。

[0158]

本公开的一个实施例中,第一因子可为2的149次方,第三预定值可为149。

[0159]

即有:第一因子factor 1=(2^126)*(2^23)=2^149;

[0160]

tmp6=f_tmp*factor1;

[0161]

其中,f_tmp表示所述浮点数,tmp6表示第六中间变量;

[0162]

那么则有:-(2^23)《tmp6《(2^23),且tmp6数据小数位为全0。

[0163]

之后可利用system verilog数组随机化方法得到一个整型数据的第一数组int_v,使得:randomize(int_v)with{length(int_v)==len;f(int_v)==tmp6},即第一数组的长度等于指定长度len,且对第一数组进行预定的线性运算f()后得到的结果为第六中间变量tmp6。

[0164]

进一步地,根据线性运算的具体操作过程,可将factor1平均分配到第一数组中的各元素中,若线性运算为加法运算,可将第一数组中的各元素分别除以factor1,从而得到所需的浮点数矢量,若线性运算为乘法运算,可从第一数组中随机选取m个元素,并可将选取出的各元素分别除以2,利用除以2后的m个元素组成第二数组,进而可将第二数组中的各元素分别除以2的n次方,从而得到所需的浮点数矢量。

[0165]

所述线性运算通常为加法运算或乘法运算,乘法运算通常是指数乘。

[0166]

当线性运算为加法运算时,可有:

[0167]

f_v=int_v/factor1;

[0168]

其中,f_v即表示得到的浮点数矢量。

[0169]

当线性运算为乘法运算时,可首先用149除以len,得到商n和余数m,即:149=

(len*n)+m,之后可利用system verilog平台提供的随机化方法,在第一数组中随机选取m个元素,并将每个元素分别除以2,从而得到第二数组f_v_pre,之后可将f_v_pre中的每个元素分别除以2^n,从而得到所需的浮点数矢量,即有:f_v=f_v_pre/2^n。

[0170]

本公开的一个实施例中,根据所述浮点数生成随机化的浮点数矢量的方式还可包括:若第一指数位不等于0,则根据第一指数位确定出第二因子,并获取所述浮点数与第二因子的乘积,得到第七中间变量;获取随机化的整型数据的第三数组,第三数组的长度等于所述指定长度,且对第三数组进行预定的线性运算后得到的结果为第七中间变量;将第二因子平均分配到第三数组中的各元素中,并结合线性运算的类型确定出浮点数矢量。

[0171]

本公开的一个实施例中,若线性运算为加法运算,可将第三数组中的各元素分别除以第二因子,得到浮点数矢量,若线性运算为乘法运算,可从第三数组中随机选取m’个元素,并可将选取出的各元素分别除以2,利用除以2后的m’个元素组成第四数组,进而可将第四数组中的各元素分别除以2的n’次方,得到浮点数矢量,其中,n’为用第四预定值除以指定长度后得到的商,m’为用第四预定值除以指定长度后得到的余数。

[0172]

本公开的一个实施例中,第二因子可为2的p次方,p为第四预定值,且为149与第一指数位的差。

[0173]

即有:第二因子factor 2=(2^(127-exp_tmp))*(2^23)=2^(149

–

exp_tmp);

[0174]

tmp 7=f_tmp*factor2;

[0175]

其中,f_tmp表示所述浮点数,tmp7表示第七中间变量;

[0176]

那么则有:-(2^24)《int_tmp《(2^24),且tmp7数据小数位为全0。

[0177]

之后可利用system verilog数组随机化方法得到一个整型数据的第三数组int_v’,使得:randomize(int_v’)with{length(int_v’)==len;f(int_v’)==tmp7},即第三数组的长度等于指定长度len,且对第三数组进行预定的线性运算f()后得到的结果为第七中间变量tmp7。

[0178]

进一步地,根据线性运算的具体操作过程,可将factor2平均分配到第三数组中的各元素中,若线性运算为加法运算,可将第三数组中的各元素分别除以factor2,从而得到所需的浮点数矢量,若线性运算为乘法运算,可从第三数组中随机选取m’个元素,并可将选取出的各元素分别除以2,利用除以2后的m’个元素组成第四数组,进而可将第四数组中的各元素分别除以2的n’次方,从而得到所需的浮点数矢量。

[0179]

当线性运算为加法运算时,可有:

[0180]

f_v=int_v’/factor2;

[0181]

其中,f_v即表示得到的浮点数矢量。

[0182]

当线性运算为乘法运算时,可首先用(149-第一指数位)除以len,得到商n’和余数m’,即:(149-第一指数位)=(len*n’)+m’,之后可利用system verilog平台提供的随机化方法,在第三数组中随机选取m’个元素,并可将每个元素分别除以2,从而得到第四数组f_v_pre’,之后可将f_v_pre’中的每个元素分别除以2^n’,从而得到所需的浮点数矢量,即有:f_v=f_v_pre’/2^n’。

[0183]

需要说明的是,对于前述的各方法实施例,为了简单描述,将其都表述为一系列的动作组合,但是本领域技术人员应该知悉,本公开并不受所描述的动作顺序的限制,因为依据本公开,某些步骤可以采用其它顺序或者同时进行。其次,本领域技术人员也应该知悉,

说明书中所描述的实施例均属于优选实施例,所涉及的动作和模块并不一定是本公开所必须的。另外,某个实施例中没有详述的部分,可以参见其它实施例中的相关说明。

[0184]

总之,采用本公开方法实施例所述方案,可得到随机化的浮点数和浮点数矢量,从而弥补了目前system verilog平台只提供针对定点数据的随机化的不足,而且,对于用户来说,其只需进行一些简单的设置即可,如进行一些约束条件的设置,其它处理均可自动完成,从而简化了用户操作,另外,利用得到的浮点数和浮点数矢量,可进行集成电路芯片验证中相关运算单元的验证,如进行浮点运算单元和浮点矢量运算单元的验证,并可加速所述相关运算单元的验证收敛过程等。

[0185]

以上是关于方法实施例的介绍,以下通过装置实施例,对本公开所述方案进行进一步说明。

[0186]

图5为本公开所述集成电路芯片验证装置第一实施例500的组成结构示意图;参数获取模块501、第一生成模块502、第二生成模块503以及验证模块504。

[0187]

参数获取模块501,用于获取第一参数和第二参数,第一参数为要求的浮点数取值上限,第二参数为要求的浮点数取值下限。

[0188]

第一生成模块502,用于根据第一参数和第二参数分别生成随机化的浮点数的第一符号位、第一指数位和第一小数位。

[0189]

第二生成模块503,用于根据第一符号位、第一指数位以及第一小数位生成所述浮点数。

[0190]

验证模块504,用于利用所述浮点数进行集成电路芯片验证。

[0191]

采用上述装置实施例所述方案,可实现浮点数据的随机化,从而为集成电路芯片验证中相关运算单元的验证提供了所需的浮点数据激励,进而提升了验证效果等。

[0192]

浮点数据可包括浮点数和浮点数矢量。浮点数可由符号位、指数位和小数位组成。

[0193]

本公开的一个实施例中,第一生成模块502可分别获取第一参数的第二符号位、第二指数位以及第二小数位,并可分别获取第二参数的第三符号位、第三指数位以及第三小数位,进而可根据获取到的第二符号位、第二指数位、第二小数位、第三符号位、第三指数位以及第三小数位,生成所述浮点数的第一符号位、第一指数位以及第一小数位。

[0194]

本公开的一个实施例中,第一生成模块502可在第二符号位和第三符号位均等于0时,按照第一生成方式生成第一符号位、第一指数位以及第一小数位,在第二符号位等于0,且第三符号位等于1时,按照第二生成方式生成第一符号位、第一指数位以及第一小数位,在第二符号位等于1,且第三符号位等于1时,按照第三生成方式生成第一符号位、第一指数位以及第一小数位。

[0195]

本公开的一个实施例中,第一生成模块502按照第一生成方式生成第一符号位、第一指数位以及第一小数位的方式可包括:若第二指数位等于第三指数位,且第二小数位大于或等于第三小数位,则将0作为第一符号位,将第二指数位或第三指数位作为第一指数位,将位于[第三小数位:第二小数位]范围内的随机值作为第一小数位。

[0196]

本公开的一个实施例中,第一生成模块502按照第一生成方式生成第一符号位、第一指数位以及第一小数位的方式还可包括:若第二指数位大于第三指数位,则生成位于[第三指数位:第二指数位]范围内的随机值,作为第一中间变量;若第一中间变量等于第三指数位,则将0作为第一符号位,将第三指数位作为第一指数位,将位于[第三小数位:第一预

定值]范围内的随机值作为第一小数位;若第一中间变量等于第二指数位,则将0作为第一符号位,将第二指数位作为第一指数位,将位于[第二预定值:第二小数位]范围内的随机值作为第一小数位;若第一中间变量既不等于第三指数位,也不等于第二指数位,则将0作为第一符号位,将第一中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0197]

本公开的一个实施例中,第一生成模块502按照第二生成方式生成第一符号位、第一指数位以及第一小数位的方式可包括:生成位于[0:1]范围内的随机值,作为第二中间变量;若第二中间变量等于0,则生成位于[0:第二指数位]范围内的随机值,作为第三中间变量;若第三中间变量等于第二指数位,则将0作为第一符号位,将第二指数位作为第一指数位,将位于[第二预定值:第二小数位]范围内的随机值作为第一小数位;若第三中间变量不等于第二指数位,则将0作为第一符号位,将第三中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0198]

本公开的一个实施例中,第一生成模块502按照第二生成方式生成第一符号位、第一指数位以及第一小数位的方式还可包括:若第二中间变量不等于0,则生成位于[0:第三指数位]范围内的随机值,作为第四中间变量;若第四中间变量等于第三指数位,则将1作为第一符号位,将第三指数位作为第一指数位,将位于[第二预定值:第三小数位]范围内的随机值作为第一小数位;若第四中间变量不等于第三指数位,则将1作为第一符号位,将第四中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0199]

本公开的一个实施例中,第一生成模块502按照第三生成方式生成第一符号位、第一指数位以及第一小数位的方式可包括:若第二指数位等于第三指数位,且第二小数位小于或等于第三小数位,则将1作为第一符号位,将第二指数位或第三指数位作为第一指数位,将位于[第二小数位:第三小数位]范围内的随机值作为第一小数位。

[0200]

本公开的一个实施例中,第一生成模块502按照第三生成方式生成第一符号位、第一指数位以及第一小数位的方式还可包括:若第二指数位大于第三指数位,则生成位于[第二指数位:第三指数位]范围内的随机值,作为第五中间变量;若第五中间变量等于第三指数位,则将1作为所述第一符号位,将第三指数位作为第一指数位,将位于[第二预定值:第三小数位]范围内的随机值作为第一小数位;若第五中间变量等于第二指数位,则将1作为第一符号位,将第二指数位作为第一指数位,将位于[第二小数位:第一预定值]范围内的随机值作为第一小数位;若第五中间变量既不等于第三指数位,也不等于第二指数位,则将1作为第一符号位,将第五中间变量作为第一指数位,将位于[第二预定值:第一预定值]范围内的随机值作为第一小数位。

[0201]

图6为本公开所述集成电路芯片验证装置第二实施例600的组成结构示意图。如图6所示,包括:参数获取模块501、第一生成模块502、第二生成模块503、验证模块504以及第三生成模块505。

[0202]

其中,参数获取模块501、第一生成模块502以及第二生成模块503与图5所示实施例中相同,不再赘述。

[0203]

第三生成模块505,用于根据所述浮点数生成指定长度的随机化的浮点数矢量。相应地,验证模块504可进一步用于,利用所述浮点数矢量进行集成电路芯片验证。

[0204]

本公开的一个实施例中,第三生成模块505可在第一指数位等于0时,获取浮点数与预定的第一因子的乘积,得到第六中间变量,获取随机化的整型数据的第一数组,第一数组的长度等于指定长度,且对第一数组进行预定的线性运算后得到的结果为第六中间变量,将第一因子平均分配到第一数组中的各元素中,并结合线性运算的类型确定出浮点数矢量。

[0205]

本公开的一个实施例中,第三生成模块505可在线性运算为加法运算时,将第一数组中的各元素分别除以第一因子,得到浮点数矢量,在线性运算为乘法运算时,从第一数组中随机选取m个元素,并将选取出的各元素分别除以2,利用除以2后的m个元素组成第二数组,将第二数组中的各元素分别除以2的n次方,得到浮点数矢量,其中,n为用第三预定值除以指定长度后得到的商,m为用第三预定值除以指定长度后得到的余数。

[0206]

本公开的一个实施例中,第一因子可为2的149次方,第三预定值可为149。

[0207]

本公开的一个实施例中,第三生成模块505可在第一指数位不等于0时,根据第一指数位确定出第二因子,并获取浮点数与第二因子的乘积,得到第七中间变量,获取随机化的整型数据的第三数组,第三数组的长度等于指定长度,且对第三数组进行预定的线性运算后得到的结果为第七中间变量,将第二因子平均分配到第三数组中的各元素中,并结合线性运算的类型确定出浮点数矢量。

[0208]

本公开的一个实施例中,第三生成模块505可在线性运算为加法运算时,将第三数组中的各元素分别除以第二因子,得到浮点数矢量,在线性运算为乘法运算时,从第三数组中随机选取m’个元素,并将选取出的各元素分别除以2,利用除以2后的m’个元素组成第四数组,将第四数组中的各元素分别除以2的n’次方,得到浮点数矢量,其中,n’为用第四预定值除以指定长度后得到的商,m’为用第四预定值除以指定长度后得到的余数。

[0209]

本公开的一个实施例中,第二因子可为2的p次方,p为第四预定值,且为149与第一指数位的差。

[0210]

图5和图6所示装置实施例的具体工作流程可参照前述方法实施例中的相关说明。

[0211]

总之,采用本公开装置实施例所述方案,可得到随机化的浮点数和浮点数矢量,从而弥补了目前system verilog平台只提供针对定点数据的随机化的不足,而且,对于用户来说,其只需进行一些简单的设置即可,如进行一些约束条件的设置,其它处理均可自动完成,从而简化了用户操作,另外,利用得到的浮点数和浮点数矢量,可进行集成电路芯片验证中相关运算单元的验证,如进行浮点运算单元和浮点矢量运算单元的验证,并可加速所述相关运算单元的验证收敛过程等。

[0212]

本公开所述方案可应用于人工智能领域,特别涉及人工智能芯片以及云计算等领域。人工智能是研究使计算机来模拟人的某些思维过程和智能行为(如学习、推理、思考、规划等)的学科,既有硬件层面的技术也有软件层面的技术,人工智能硬件技术一般包括如传感器、专用人工智能芯片、云计算、分布式存储、大数据处理等技术,人工智能软件技术主要包括计算机视觉技术、语音识别技术、自然语言处理技术以及机器学习/深度学习、大数据处理技术、知识图谱技术等几大方向。

[0213]

另外,本公开的技术方案中,所涉及的用户个人信息的收集、存储、使用、加工、传输、提供和公开等处理,均符合相关法律法规的规定,且不违背公序良俗。

[0214]

根据本公开的实施例,本公开还提供了一种电子设备、一种可读存储介质和一种

计算机程序产品。

[0215]

图7示出了可以用来实施本公开的实施例的电子设备700的示意性框图。电子设备旨在表示各种形式的数字计算机,诸如,膝上型计算机、台式计算机、工作台、服务器、刀片式服务器、大型计算机、和其它适合的计算机。电子设备还可以表示各种形式的移动装置,诸如,个人数字助理、蜂窝电话、智能电话、可穿戴设备和其它类似的计算装置。本文所示的部件、它们的连接和关系、以及它们的功能仅仅作为示例,并且不意在限制本文中描述的和/或者要求的本公开的实现。

[0216]

如图7所示,设备700包括计算单元701,其可以根据存储在只读存储器(rom)702中的计算机程序或者从存储单元708加载到随机访问存储器(ram)703中的计算机程序,来执行各种适当的动作和处理。在ram 703中,还可存储设备700操作所需的各种程序和数据。计算单元701、rom 702以及ram 703通过总线704彼此相连。输入/输出(i/o)接口705也连接至总线704。

[0217]

设备700中的多个部件连接至i/o接口705,包括:输入单元706,例如键盘、鼠标等;输出单元707,例如各种类型的显示器、扬声器等;存储单元708,例如磁盘、光盘等;以及通信单元709,例如网卡、调制解调器、无线通信收发机等。通信单元709允许设备700通过诸如因特网的计算机网络和/或各种电信网络与其他设备交换信息/数据。

[0218]

计算单元701可以是各种具有处理和计算能力的通用和/或专用处理组件。计算单元701的一些示例包括但不限于中央处理单元(cpu)、图形处理单元(gpu)、各种专用的人工智能(ai)计算芯片、各种运行机器学习模型算法的计算单元、数字信号处理器(dsp)、以及任何适当的处理器、控制器、微控制器等。计算单元701执行上文所描述的各个方法和处理,例如本公开所述的方法。例如,在一些实施例中,本公开所述的方法可被实现为计算机软件程序,其被有形地包含于机器可读介质,例如存储单元708。在一些实施例中,计算机程序的部分或者全部可以经由rom 702和/或通信单元709而被载入和/或安装到设备700上。当计算机程序加载到ram 703并由计算单元701执行时,可以执行本公开所述的方法的一个或多个步骤。备选地,在其他实施例中,计算单元701可以通过其他任何适当的方式(例如,借助于固件)而被配置为执行本公开所述的方法。

[0219]

本文中以上描述的系统和技术的各种实施方式可以在数字电子电路系统、集成电路系统、场可编程门阵列(fpga)、专用集成电路(asic)、专用标准产品(assp)、芯片上系统的系统(soc)、复杂可编程逻辑设备(cpld)、计算机硬件、固件、软件、和/或它们的组合中实现。这些各种实施方式可以包括:实施在一个或者多个计算机程序中,该一个或者多个计算机程序可在包括至少一个可编程处理器的可编程系统上执行和/或解释,该可编程处理器可以是专用或者通用可编程处理器,可以从存储系统、至少一个输入装置、和至少一个输出装置接收数据和指令,并且将数据和指令传输至该存储系统、该至少一个输入装置、和该至少一个输出装置。

[0220]

用于实施本公开的方法的程序代码可以采用一个或多个编程语言的任何组合来编写。这些程序代码可以提供给通用计算机、专用计算机或其他可编程数据处理装置的处理器或控制器,使得程序代码当由处理器或控制器执行时使流程图和/或框图中所规定的功能/操作被实施。程序代码可以完全在机器上执行、部分地在机器上执行,作为独立软件包部分地在机器上执行且部分地在远程机器上执行或完全在远程机器或服务器上执行。

[0221]

在本公开的上下文中,机器可读介质可以是有形的介质,其可以包含或存储以供指令执行系统、装置或设备使用或与指令执行系统、装置或设备结合地使用的程序。机器可读介质可以是机器可读信号介质或机器可读储存介质。机器可读介质可以包括但不限于电子的、磁性的、光学的、电磁的、红外的、或半导体系统、装置或设备,或者上述内容的任何合适组合。机器可读存储介质的更具体示例会包括基于一个或多个线的电气连接、便携式计算机盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦除可编程只读存储器(eprom或快闪存储器)、光纤、便捷式紧凑盘只读存储器(cd-rom)、光学储存设备、磁储存设备、或上述内容的任何合适组合。

[0222]

为了提供与用户的交互,可以在计算机上实施此处描述的系统和技术,该计算机具有:用于向用户显示信息的显示装置(例如,crt(阴极射线管)或者lcd(液晶显示器)监视器);以及键盘和指向装置(例如,鼠标或者轨迹球),用户可以通过该键盘和该指向装置来将输入提供给计算机。其它种类的装置还可以用于提供与用户的交互;例如,提供给用户的反馈可以是任何形式的传感反馈(例如,视觉反馈、听觉反馈、或者触觉反馈);并且可以用任何形式(包括声输入、语音输入或者、触觉输入)来接收来自用户的输入。

[0223]

可以将此处描述的系统和技术实施在包括后台部件的计算系统(例如,作为数据服务器)、或者包括中间件部件的计算系统(例如,应用服务器)、或者包括前端部件的计算系统(例如,具有图形用户界面或者网络浏览器的用户计算机,用户可以通过该图形用户界面或者该网络浏览器来与此处描述的系统和技术的实施方式交互)、或者包括这种后台部件、中间件部件、或者前端部件的任何组合的计算系统中。可以通过任何形式或者介质的数字数据通信(例如,通信网络)来将系统的部件相互连接。通信网络的示例包括:局域网(lan)、广域网(wan)和互联网。

[0224]

计算机系统可以包括客户端和服务器。客户端和服务器一般远离彼此并且通常通过通信网络进行交互。通过在相应的计算机上运行并且彼此具有客户端-服务器关系的计算机程序来产生客户端和服务器的关系。服务器可以是云服务器,也可以为分布式系统的服务器,或者是结合了区块链的服务器。

[0225]

应该理解,可以使用上面所示的各种形式的流程,重新排序、增加或删除步骤。例如,本发公开中记载的各步骤可以并行地执行也可以顺序地执行也可以不同的次序执行,只要能够实现本公开公开的技术方案所期望的结果,本文在此不进行限制。

[0226]

上述具体实施方式,并不构成对本公开保护范围的限制。本领域技术人员应该明白的是,根据设计要求和其他因素,可以进行各种修改、组合、子组合和替代。任何在本公开的精神和原则之内所作的修改、等同替换和改进等,均应包含在本公开保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1