存储器、存储器芯片以及存储器数据存取方法与流程

[0001]

本发明大体上涉及存储器数据存取技术,特定而言,涉及一种存储器、存储器芯片以及存储器数据存取方法。

[0002]

相关申请的交叉参考

[0003]

本申请案主张2019年8月15日申请的美国临时申请案序列号62/886,973的优先权益。以上所提及的专利申请案的全部内容特此以引用的方式并入本文中,且成为本说明书的一部分。

背景技术:

[0004]

在一般存储器架构中,存储器的多个存储器芯片中的每一个仅包含具有多个存储体的一个存储体组,其中存储器芯片中的每一个还包含一个读取放大器及一个写入放大器。也就是说,存储器芯片中的每一个必须在不同时间分别执行读取操作及写入操作。换言之,若存储器芯片中的一个在相同时间具有读取需求及写入需求,则存储器芯片中的一个必须执行读取操作及写入操作中的一个,且随后在完成前一操作之后执行读取操作及写入操作中的另一个。因此,一般存储器架构的存储器的存储器数据存取效率较低,且易于发生存储器数据存取冲突。因此,关于如何使存储器达到良好数据存取效率以及减少存储器数据存取冲突,下文提供若干实施例的解决方案。

技术实现要素:

[0005]

本发明针对一种存储器、存储器芯片以及存储器数据存取方法,且能够提供较佳存储器数据存取效率。

[0006]

本发明的存储器包含多个存储器芯片。多个存储器芯片中的每一个包含第一体组、第二体组以及读取放大器及写入放大器。第一体组包含多个第一存储体(bank)。第二体组包含多个第二存储体。读取放大器及写入放大器分别耦接至第一体组及第二体组,且经配置以独立地存取不同体组。

[0007]

在本发明的一实施例中,各多个存储器芯片的读取放大器经由第一子输入/输出总线耦接至第一输入/输出总线。第一输入/输出总线的频宽大于第一子输入/输出总线的频宽,以使得多个存储器芯片的读取放大器的至少部分同时经由第一输入/输出总线传输数据。

[0008]

在本发明的一实施例中,第一输入/输出总线的频宽等于耦接多个存储器芯片的读取放大器的第一子输入/输出总线的频宽的总和。

[0009]

在本发明的一实施例中,各多个存储器芯片的写入放大器经由第二子输入/输出总线耦接至第二输入/输出总线。第二输入/输出总线的频宽大于第二子输入/输出总线的频宽,以使得多个存储器芯片的写入放大器的至少部分同时经由第二输入/输出总线接收数据。

[0010]

在本发明的一实施例中,第二输入/输出总线的频宽等于耦接多个存储器芯片的

写入放大器的第二子输入/输出总线的频宽的总和。

[0011]

在本发明的一实施例中,存储器芯片中的一个接收读取开始命令以开始读取操作,且存储器芯片中的一个的读取放大器在读取操作的读取时段期间自第一体组及第二体组中的一个读取第一数据。存储器芯片中的一个在读取时段期间连续接收写入开始命令以开始写入操作,且存储器芯片中的一个的写入放大器在写入操作的写入时段期间将第二数据写入至第一体组及第二体组中的一个中,其中读取时段与写入时段部分交叠。

[0012]

在本发明的一实施例中,多个第一存储体及多个第二存储体中的每一个为存储器阵列。存储器阵列包含多个子存储器阵列。多个子存储器阵列经由全局数据线耦接至读取放大器及写入放大器。当读取放大器在读取时段期间根据读取开始命令自全局数据线读取多个子存储器阵列中的一个的第一数据时,写入放大器预先接收第二数据以开始写入时段。在读取放大器完成在读取时段期间自全局数据线接收第一数据之后,写入放大器将第二数据连续传输至全局数据线以用于在写入时段期间写入至相同或不同子存储器阵列中。

[0013]

在本发明的一实施例中,多个存储器芯片中的每一个包含选择器。选择器经由第一内部输入/输出总线耦接至读取放大器,经由第二内部输入/输出总线耦接至写入放大器,且经由子共享输入/输出总线耦接至共享输入/输出总线。选择器经配置以选择以经由读取放大器及写入放大器来存取第一体组或第二体组。

[0014]

在本发明的一实施例中,子共享输入/输出总线的频宽大于或等于第一内部输入/输出总线及第二内部输入/输出总线的频宽的总和,以使得读取放大器及写入放大器同时存取不同存储体。

[0015]

在本发明的一实施例中,共享输入/输出总线的频宽等于两个子共享输入/输出总线的频宽的总和。

[0016]

本发明的存储器芯片包含第一体组、第二体组以及读取放大器及写入放大器。第一体组包含多个第一存储体。第二体组包含多个第二存储体。读取放大器及写入放大器分别耦接至第一体组及第二体组,且经配置以独立地存取不同体组。

[0017]

存储器数据存取方法适用于本发明的存储器芯片。存储器芯片包含第一体组、第二体组、读取放大器以及写入放大器。读取放大器及写入放大器经配置以独立地存取不同体组。数据存取方法包含以下步骤。由存储器芯片接收读取开始命令以开始读取操作。由读取放大器在读取操作的读取时段期间自第一体组及第二体组中的一个读取第一数据。在读取时段期间,由存储器芯片连续接收写入开始命令以开始写入操作。由写入放大器在写入操作的写入时段期间将第二数据写入至第一体组及第二体组中的一个中,其中读取时段与写入时段部分交叠。

[0018]

基于上文,根据本发明的存储器、存储器芯片以及存储器数据存取方法,存储器的存储器芯片能够同时对不同存储体组执行读取操作及写入操作,因此存储器芯片及存储器能够提供较佳存储器数据存取效率。

[0019]

为使本发明的前述特征及优点更容易理解,下文详细描述附有随附图式的实施例。

附图说明

[0020]

包含附图以提供本发明的进一步理解,且附图并入于本说明书中并构成本说明书

的一部分。图式说明本发明的例示性实施例,且与本说明书一起用以解释本发明的原理。

[0021]

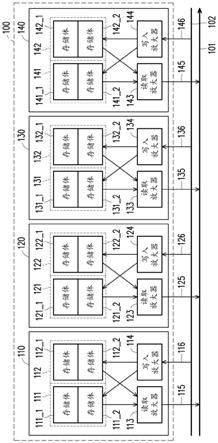

图1为根据本发明的一实施例的存储器的示意性架构图。

[0022]

图2为根据本发明的一实施例的存储器芯片的示意性架构图。

[0023]

图3为根据本发明的一实施例的存取相同存储体组的操作时序图。

[0024]

图4为根据本发明的另一实施例的存取相同存储体组的操作时序图。

[0025]

图5为根据本发明的一实施例的存取不同存储体组的操作时序图。

[0026]

图6为根据本发明的另一实施例的存取不同存储体组的操作时序图。

[0027]

图7为根据本发明的另一实施例的存储器的示意性架构图。

[0028]

图8为根据本发明的一实施例的存储器数据存取方法的流程图。

具体实施方式

[0029]

为使本发明的内容更易于理解,列出以下实施例作为本发明的实例,所述实例可完全相应地实施。另外,若可能,则在图式中以相同标识数字标记的元件/组件/步骤及实施方案模式表示相同或类似部分。

[0030]

图1为根据本发明的一实施例的存储器的示意性架构图。参考图1,存储器100包含存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140,且多个存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140经由两个输入/输出总线101及输入/输出总线102耦接至存储器100外部的其他电路或模块,诸如中央处理器单元(center processor unit;cpu)、图像信号处理器(image signal processor;isp)核心、数字信号处理器(digital signal processor;dsp)核心、图形处理单元(graphics processing unit;gpu)核心、卷积神经网络(convolutional neural network;cnn)加速器或具有大量数据的存储器存取需求的其他模块。在本发明的实施例中,存储器100可为动态随机存取存储器(dynamic random-access memory;dram),但本发明不限于此。在本发明的实施例中,存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140包含第一存储体组111、第一存储体组121、第一存储体组131以及第一存储体组141以及第二存储体组112、第二存储体组122、第二存储体组132以及第二存储体组142,其中存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的每一个包含一个第一存储体组及一个第二存储体组。换言之,存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的每一个的一个存储器阵列可经划分以形成两个不同存储体组,且两个不同存储体组中的每一个还包含一个或多个存储体。

[0031]

在本发明的实施例中,第一存储体组111、第一存储体组121、第一存储体组131以及第一存储体组141以及第二存储体组112、第二存储体组122、第二存储体组132以及第二存储体组142包含第一存储体111_1、第一存储体112_1、第一存储体121_1、第一存储体122_1、第一存储体131_1、第一存储体132_1、第一存储体141_1以及第一存储体142_1以及第二存储体111_2、第二存储体112_2、第二存储体121_2、第二存储体122_2、第二存储体131_2、第二存储体132_2、第二存储体141_2以及第二存储体142_2,其中一个存储体组包含一个第一存储体及一个第二存储体。举例而言,存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的每一个的存储能力为1十亿字节(gigabyte;gb),其中一个存储体的存储宽度为128千字节(kilobyte;kb),且一个存储体的存储深度为2千字节。在本发明的实

施例中,存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140还包含读取放大器113、读取放大器123、读取放大器133以及读取放大器143以及写入放大器114、写入放大器124、写入放大器134以及写入放大器144,其中存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的每一个包含一个读取放大器及一个写入放大器。读取放大器113、读取放大器123、读取放大器133以及读取放大器143中的每一个耦接至存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的每一个中的各别两个存储体组,且写入放大器114、写入放大器124、写入放大器134以及写入放大器144中的每一个也耦接至存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的每一个中的各别两个存储体组。读取放大器113、读取放大器123、读取放大器133以及读取放大器143分别经由子输入/输出总线115、子输入/输出总线125、子输入/输出总线135以及子输入/输出总线145耦接至输入/输出总线101。写入放大器114、写入放大器124、写入放大器134以及写入放大器144分别经由子输入/输出总线116、子输入/输出总线126、子输入/输出总线136以及子输入/输出总线146耦接至输入/输出总线102。然而,本发明的存储器100的存储器芯片的数目及存储体的数目不限于此。

[0032]

在本发明的实施例中,输入/输出总线101的频宽可大于或等于子输入/输出总线115、子输入/输出总线125、子输入/输出总线135以及子输入/输出总线145的频宽的总和。举例而言,输入/输出总线101的频宽可为2千字节,且子输入/输出总线115、子输入/输出总线125、子输入/输出总线135以及子输入/输出总线145的频宽中的每一个可为512字节。因此,存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140共享输入/输出总线101,以使得存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140的至少部分的读取操作可同时独立地执行,其中存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140的至少部分可同时经由输入/输出总线101的子输入/输出总线115、子输入/输出总线125、子输入/输出总线135以及子输入/输出总线145传输数据。在本发明的实施例中,输入/输出总线102的频宽可大于或等于子输入/输出总线116、子输入/输出总线126、子输入/输出总线136以及子输入/输出总线146的频宽的总和。举例而言,输入/输出总线102的频宽可为2千字节,且子输入/输出总线116、子输入/输出总线126、子输入/输出总线136以及子输入/输出总线146的频宽中的每一个可为512字节。因此,存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140共享输入/输出总线102,以使得存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140的至少部分的写入操作可同时独立地执行,其中存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140可同时经由输入/输出总线102的子输入/输出总线116、子输入/输出总线126、子输入/输出总线136以及子输入/输出总线146接收数据。

[0033]

在本发明的实施例中,采用存储器芯片110作为一实例,由于读取放大器113及写入放大器114分别耦接至体组111及体组112,因而读取放大器113及写入放大器114能够独立地存取不同体组111及体组112。也就是说,读取放大器113可自体组111及体组112中的一个读取数据,且写入放大器114可同时将数据写入至体组111及体组112中的另一个中。换言之,存储器100的存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140能够同时对不同体组执行读取操作及写入操作中的至少一个。存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140无需等待彼此的存取操作,从而节省等待存取的时间。

因此,本发明的存储器100能够提供快速且高效的存储器数据存取效率以满足大量数据的存储器存取需求。

[0034]

图2为根据本发明的一实施例的存储器芯片的示意性架构图。参考图2,存储器芯片200可应用于本发明的各实施例的存储器芯片。存储器芯片200包含多个子存储器阵列210_1至子存储器阵列210_n,其中n为大于1的正整数,且子存储器阵列210_1至子存储器阵列210_n属于一个存储体组。此外,子存储器阵列210_1至子存储器阵列210_n可分别对应于两个存储体,诸如以上第一存储体及以上第二存储体。存储器芯片200还包含对应于子存储器阵列210_1至子存储器阵列210_n的多个感测放大器220_1至感测放大器220_n。在的本发明的实施例中,存储器芯片200的读取放大器207及写入放大器208分别经由全局数据线放大器205及全局数据线放大器206分别耦接至全局数据线203,且全局数据线203进一步耦接至感测放大器220_1至感测放大器220_n。读取放大器207及写入放大器208为先入先出(first input first output;fifo)信道。感测放大器220_1至感测放大器220_n分别存取子存储器阵列210_1至子存储器阵列210_n,且经由多个局部数据线204_1至局部数据线204_n将数据传输至全局数据线203。在本发明的实施例中,读取放大器207进一步耦接至输入/输出总线201以将由子存储器阵列210_1至子存储器阵列210_n中的任一个读取的数据传输至外部,且写入放大器208进一步耦接至输入/输出总线202以自外部接收数据以用于写入至子存储器阵列210_1至子存储器阵列210_n中的任一个中。

[0035]

图3为根据本发明的一实施例的存取相同存储体组的操作时序图。参考图2及图3,图3的操作时序图可应用于存储器芯片200,且此实施例采用存取子存储器阵列210_1(相同存储体组)作为一实例。在本发明的实施例中,如由图3中的时间顺序cmd所示,存储器芯片200在时段311期间接收读取开始命令(rd)以开始读取操作,且随后存储器芯片200在时段321期间接收写入开始命令(wr)以开始写入操作,其中读取操作的读取时段与写入操作的写入时段部分交叠。读取时段在时间点t10至时间点t12之间。写入时段在时间点t11至时间点t13之间。在本发明的实施例中,在存储器芯片200在时段311期间接收读取开始命令(rd)且开始读取操作之后,如由图3中的时间顺序sa所示,感测放大器220_1在时段312期间自子存储器阵列210_1读取数据(q)。随后,如由图3中的时间顺序ld所示,在时段313期间由局部数据线204_1传输数据(q)。随后同样,如由图3中的时间顺序gd所示,在时段314期间由全局数据线203传输数据(q)。最终,如由图3中的时间顺序i/o所示,全局数据线放大器205及读取放大器207自全局数据线203接收数据(q),且将数据(q)提供至输入/输出总线201。

[0036]

在本发明的实施例中,存储器芯片200可在时段321期间(在读取开始命令(rd)之后)接收写入开始命令(wr)。举例而言,当感测放大器220_1自子存储器阵列210_1读取数据(q)时,存储器芯片200接收写入开始命令(wr)。因此,如由图3中的时间顺序i/o所示,全局数据线放大器206及写入放大器208在时段322期间自输入/输出总线202接收数据(d),且将数据(d)提供至全局数据线203。随后,如由图3中的时间顺序gd所示,在时段323期间由全局数据线203传输数据(d)。应注意,如由图3中的时间顺序gd所示,由于全局数据线203首先输出数据(d)且随后输入数据(q),因而全局数据线203不具有存储器数据存取冲突。随后同样,如由图3中的时间顺序ld所示,在时段324期间由局部数据线204_1传输数据(d)。最终,如由图3中的时间顺序sa所示,感测放大器220_1在时段325期间经由子存储器阵列210_1将数据(d)写入至子存储器阵列210_1中。因此,在局部数据线204_1及感测放大器220_1中也

不存在存储器数据存取冲突。此外,由于读取操作的读取时段与写入操作的写入时段部分交叠,因而存储器芯片200能够提供快速且高效的数据存取效率。另外,在本发明的其他实施例中,图3的操作时序图也可应用于对存储器芯片200的相同存储体组中的不同子存储器阵列执行读取操作及写入操作的另一存取情况。

[0037]

图4为根据本发明的另一实施例的存取相同存储体组的操作时序图。图4为根据本发明的一实施例的存取相同存储体组的操作时序图。参考图2及图4,图4的操作时序图可应用于存储器芯片200,且此实施例采用存取子存储器阵列210_1(相同存储体组)作为一实例。在本发明的实施例中,如由图4中的时间顺序cmd所示,存储器芯片200在时段411期间接收写入开始命令(wr)以开始写入操作,且随后存储器芯片200在时段421期间接收读取开始命令(rd)以开始读取操作,其中读取操作的读取时段与写入操作的写入时段不交叠。写入时段在时间点t20至时间点t21之间。读取时段在时间点t22至时间点t23之间。在本发明的实施例中,在存储器芯片200在时段411期间接收写入开始命令(wr)且开始写入操作之后,如由图4中的时间顺序i/o所示,全局数据线放大器206及写入放大器208在时段412期间自输入/输出总线202接收数据(d)且将数据(d)提供至全局数据线203。随后,如由图4中的时间顺序gd所示,在时段413期间由全局数据线203传输数据(d)。随后同样,如由图4中的时间顺序ld所示,在时段414期间由局部数据线204_1传输数据(d)。最终,如由图4中的时间顺序sa所示,感测放大器220_1在时段415期间将数据(d)写入至子存储器阵列210_1中。

[0038]

在本发明的实施例中,为避免感测放大器220_1、局部数据线204_1以及全局数据线放大器205发生数据存取冲突,若在读取操作之前执行写入操作,则读取操作应在执行之前等待读取操作完成。因此,如由图4中的时间顺序sa所示,感测放大器220_1在时段422期间经由子存储器阵列210_1自子存储器阵列210_1读取数据(q)。随后,如由图4中的时间顺序ld所示,在时段423期间由局部数据线204_1传输数据(q)。随后同样,如由图4中的时间顺序gd所示,在时段424期间由全局数据线203传输数据(q)。最终,如由图4中的时间顺序i/o所示,全局数据线放大器205及读取放大器207在时段425期间自全局数据线203接收数据(q),且将数据(q)提供至输入/输出总线201。另外,在本发明的其他实施例中,图4的操作时序图也可应用于对存储器芯片200的相同存储体组中的不同子存储器阵列执行读取操作及写入操作的另一存取情况。

[0039]

图5为根据本发明的一实施例的存取不同存储体组的操作时序图。参考图2及图5,图5的操作时序图可应用于存储器芯片200,且此实施例采用存取不同存储体组的不同子存储器阵列作为一实例。在本发明的实施例中,图2的存储器芯片200可还包含另一存储体组(未展示),且读取放大器207及写入放大器208可另外耦接至另一存储体组的另一子存储器阵列。

[0040]

在本发明的实施例中,存储器芯片200存取子存储器阵列210_1及属于不同存储体组的另一子存储器阵列。因此,如由图5中的时间顺序cmd所示,存储器芯片200在时段511期间接收读取开始命令(rd0)以开始读取操作,且随后存储器芯片200在时段521期间接收写入开始命令(wr1)以开始写入操作,其中读取操作的读取时段与写入操作的写入时段部分交叠。读取时段在时间点t30至时间点t32之间。写入时段在时间点t31至时间点t33之间。在本发明的实施例中,在存储器芯片200在时段511期间接收读取开始命令(rd)且开始读取操作之后,如由图5中的时间顺序sa0所示,感测放大器220_1在时段512期间经由子存储器阵

列210_1自子存储器阵列210_1读取数据(q0)。随后,如由图5中的时间顺序ld0所示,在时段513期间由局部数据线204_1传输数据(q0)。随后同样,如由图5中的时间顺序gd0所示,在时段514期间由全局数据线203传输数据(q0)。最终,如由图5中的时间顺序out所示,全局数据线放大器205及读取放大器207自全局数据线203接收数据(q0),且将数据(q0)提供至输入/输出总线201。

[0041]

在本发明的实施例中,存储器芯片200可在时段521期间(在读取开始命令(rd0)之后)接收写入开始命令(wr1)。举例而言,当感测放大器220_1自子存储器阵列210_1读取数据(q0)时,存储器芯片200接收写入开始命令(wr1)。因此,如由图5中的时间顺序in所示,另一全局数据线放大器及写入放大器208在时段522期间自输入/输出总线202接收数据(d1)且将数据(d1)提供至另一全局数据线(未展示)。随后,如由图5中的时间顺序gd1所示,在时段523期间由另一全局数据线传输数据(d1)。随后同样,如由图5中的时间顺序ld1所示,在时段524期间由另一局部数据线(未展示)传输数据(d1)。最终,如由图5中的时间顺序sa1所示,另一感测放大器(未展示)在时段325期间将数据(d1)写入至属于不同存储体组的另一子存储器阵列中。应注意,由于读取放大器207及写入放大器208经配置以藉由不同全局数据线放大器、不同全局数据线、不同局部数据线以及不同感测放大器来存取属于两个不同存储体组的两个不同子存储器阵列,因而存储器芯片200在实施例的此数据存取情况下不具有存储器数据存取冲突,且能够提供快速且高效的数据存取效率。

[0042]

图6为根据本发明的另一实施例的存取不同存储体组的操作时序图。参考图2及图6,图6的操作时序图可应用于存储器芯片200,且此实施例采用存取不同存储体组的不同子存储器阵列作为一实例。在本发明的实施例中,图2的存储器芯片200可还包含另一存储体组(未展示),且读取放大器207及写入放大器208可另外耦接至另一存储体组的另一子存储器阵列。

[0043]

在本发明的实施例中,存储器芯片200存取子存储器阵列210_1及属于不同存储体组的另一子存储器阵列。因此,如由图6中的时间顺序cmd所示,存储器芯片200在时段611期间接收写入开始命令(wr0)以开始写入操作,且随后存储器芯片200在时段621期间接收读取开始命令(rd1)以开始读取操作,其中读取操作的读取时段与写入操作的写入时段部分交叠。写入时段在时间点t40至时间点t42之间。读取时段在时间点t41至时间点t43之间。在本发明的实施例中,在存储器芯片200在时段611期间接收写入开始命令(wr0)且开始写入操作之后,如由图6中的时间顺序in所示,全局数据线放大器206及写入放大器208在时段612期间自输入/输出总线202接收数据(d0)且将数据(d0)提供至全局数据线203。随后,如由图6中的时间顺序gd0所示,在时段613期间由全局数据线203传输数据(d0)。随后同样,如由图6中的时间顺序ld0所示,在时段614期间由局部数据线204_1传输数据(d0)。最终,如由图6中的时间顺序sa0所示,感测放大器220_1在时段615期间经由子存储器阵列210_1将数据(d0)写入至子存储器阵列210_1中。

[0044]

在本发明的实施例中,存储器芯片200可在时段621期间(在写入开始命令(wr0)之后)接收读取开始命令(rd1)。举例而言,当全局数据线放大器206及写入放大器208自输入/输出总线202接收数据(d0)时,存储器芯片200接收读取开始命令(rd1)。因此,如由图6中的时间顺序sa1所示,另一感测放大器(未展示)在时段622期间自属于不同存储体组的另一子存储器阵列读取数据(q1)。随后,如由图6中的时间顺序ld1所示,在时段623期间由另一局

部数据线(未展示)传输数据(q1)。随后同样,如由图6中的时间顺序gd1所示,在时段624期间由另一全局数据线(未展示)传输数据(q1)。最终,如由图6中的时间顺序out所示,另一全局数据线放大器及读取放大器207在时段625期间自另一全局数据线接收数据(q1),且将数据(q1)提供至输入/输出总线201。应注意,由于读取放大器207及写入放大器208经配置以藉由不同全局数据线放大器、不同全局数据线、不同局部数据线以及不同感测放大器来存取属于两个不同存储体组的两个不同子存储器阵列,因而存储器芯片200在实施例的此数据存取情况下不具有存储器数据存取冲突,且能够提供快速且高效的数据存取效率。

[0045]

图7为根据本发明的另一实施例的存储器的示意性架构图。存储器700包含存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740,且多个存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740耦接至存储器700外部的其他电路或模块。在本发明的实施例中,存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740包含第一存储体组711、第一存储体组721、第一存储体组731以及第一存储体组741以及第二存储体组712、第二存储体组722、第二存储体组732以及第二存储体组742,其中存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740中的每一个包含一个第一存储体组及一个第二存储体组。在本发明的实施例中,第一存储体组711、第一存储体组721、第一存储体组731以及第一存储体组741以及第二存储体组712、第二存储体组722、第二存储体组732以及第二存储体组742包含第一存储体711_1、第一存储体712_1、第一存储体721_1、第一存储体722_1、第一存储体731_1、第一存储体732_1、第一存储体741_1以及第一存储体742_1以及第二存储体711_2、第二存储体712_2、第二存储体721_2、第二存储体722_2、第二存储体731_2、第二存储体732_2、第二存储体741_2以及第二存储体742_2,其中一个存储体组包含一个第一存储体及一个第二存储体。存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740还包含读取放大器713、读取放大器723、读取放大器733以及读取放大器743以及写入放大器714、写入放大器724、写入放大器734以及写入放大器744,其中存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740中的每一个包含一个读取放大器及一个写入放大器。与图1的以上实施例相比,存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740还包含选择器717、选择器727、选择器737以及选择器747,其中存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740中的每一个包含一个选择器。在本发明的实施例中,读取放大器713、读取放大器723、读取放大器733以及读取放大器743中的每一个耦接至存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740中的每一个中的各别两个存储体组,且写入放大器714、写入放大器724、写入放大器734以及写入放大器744中的每一个也耦接至存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740中的每一个中的各别两个存储体组。

[0046]

在本发明的实施例中,读取放大器713、读取放大器723、读取放大器733以及读取放大器743分别经由内部输入/输出总线715、内部输入/输出总线725、内部输入/输出总线735以及内部输入/输出总线745耦接至选择器717、选择器727、选择器737以及选择器747。写入放大器714、写入放大器724、写入放大器734以及写入放大器744分别经由内部输入/输出总线716、内部输入/输出总线726、内部输入/输出总线736以及内部输入/输出总线746耦接至选择器717、选择器727、选择器737以及选择器747。选择器717、选择器727、选择器737以及选择器747经由子共享输入/输出总线718、子共享输入/输出总线728、子共享输入/输

出总线738以及子共享输入/输出总线748耦接至共享输入/输出总线701。在本发明的实施例中,选择器717、选择器727、选择器737以及选择器747经配置以分别选择以经由各别读取放大器或及各别写入放大器根据各别存储器地址来存取各别第一体组或各别第二体组。然而,本发明的存储器的存储器芯片的数目及存储体的数目不限于此。

[0047]

在本发明的实施例中,共享输入/输出总线701的频宽可大于或等于子共享输入/输出总线718、子共享输入/输出总线728、子共享输入/输出总线738以及子共享输入/输出总线748中的任两者的频宽的总和。子共享输入/输出总线718可大于或等于内部输入/输出总线715及内部输入/输出总线716的频宽的总和。子共享输入/输出总线728可大于或等于内部输入/输出总线725及内部输入/输出总线726的频宽的总和。子共享输入/输出总线738可大于或等于内部输入/输出总线735及内部输入/输出总线736的频宽的总和。子共享输入/输出总线748可大于或等于内部输入/输出总线745及内部输入/输出总线746的频宽的总和。举例而言,共享输入/输出总线701的频宽可为2千字节,且子共享输入/输出总线718、子共享输入/输出总线728、子共享输入/输出总线738以及子共享输入/输出总线748的频宽中的每一个可为1千字节。内部输入/输出总线715、内部输入/输出总线725、内部输入/输出总线735以及内部输入/输出总线745以及内部输入/输出总线716、内部输入/输出总线726、内部输入/输出总线736以及内部输入/输出总线746的频宽中的每一个可为512字节。因此,存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740的至少部分的读取操作或写入操作中的至少一个可同时独立地执行,其中存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740的至少部分可同时经由子共享输入/输出总线718、子共享输入/输出总线728、子共享输入/输出总线738以及子共享输入/输出总线748将数据传输至共享输入/输出总线701,且同时经由子共享输入/输出总线718、子共享输入/输出总线728、子共享输入/输出总线738以及子共享输入/输出总线748自共享输入/输出总线701接收数据。

[0048]

在本发明的实施例中,采用存储器芯片710作为一实例,由于读取放大器713及写入放大器714分别耦接至体组711及体组712,因而读取放大器713及写入放大器714能够独立地存取不同体组711及体组712。也就是说,可由选择器717选择读取放大器713以根据存储器地址自体组711及体组712中的一个读取数据,且同时可由选择器717选择写入放大器714以根据另一存储器地址将数据写入至体组711及体组712中的另一个中。换言之,存储器700的存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740能够同时对不同体组执行读取操作及写入操作中的至少一个。存储器芯片710、存储器芯片720、存储器芯片730以及存储器芯片740无需等待彼此的存取操作以节省等待存取的时间。因此,本发明的存储器700能够提供快速且高效的存储器数据存取效率以满足大量数据的存储器存取需求,且进一步减少耦接至外部的输入/输出总线的数目。应注意,图3至图6的操作时序图也可应用于存储器芯片700,且对应用于存储器芯片700的图3至图6的操作时序图的实施方案内容及技术特征的充足教导及建议可自图1至图6的实施例的相关描述习得,且其细节不重复。

[0049]

图8为根据本发明的一实施例的存储器数据存取方法的流程图。参考图1及图8,图8的存储器数据存取方法可至少适用于图1的存储器100的存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的任一个,且以下描述采用存储器芯片110作为一实例。在步骤s810中,存储器芯片110接收读取开始命令以开始读取操作。在步骤s820中,读取

放大器113在读取操作的读取时段期间自第一体组111及第二体组112中的一个读取第一数据。在步骤s830中,存储器芯片110在读取时段期间连续接收写入开始命令以开始写入操作。在步骤s840中,写入放大器114在写入操作的写入时段期间将第二数据写入至第一体组111及第二体组112中的一个中,其中读取时段与写入时段部分交叠。因此,由于读取操作的读取时段与写入操作的写入时段部分交叠,因而图8的存储器数据存取方法能够制造存储器100中的存储器芯片110、存储器芯片120、存储器芯片130以及存储器芯片140中的任一个以提供快速且高效的数据存取效率。

[0050]

另外,可自图1至图7的实施例的相关描述习得对实施例的存储器100的其他存储器特征、实施方案细节及技术特征的充足教导及建议,且不重复其细节。

[0051]

总之,在存储器中,根据本发明的存储器芯片及其存储器数据存取方法,存储器的存储器芯片能够同时对不同存储体组执行读取操作及写入操作。此外,若在写入操作之前预先对相同存储体组执行读取操作,则读取操作的读取时段与写入操作的写入时段可部分交叠。因此,本发明的存储器芯片及存储器能够提供较佳存储器数据存取效率,且避免存储器数据存取冲突。

[0052]

本领域的技术人员将显而易见,在不偏离本发明的范畴或精神的情况下,能够对所揭露实施例作出各种修改及变化。鉴于前述,本发明意欲覆盖修饰及变化,前提为所述修饰及变化属于以下申请专利范围及其等效物的范畴内。

[0053]

【符号说明】

[0054]

100、700:存储器

[0055]

101、102、201、202:输入/输出总线

[0056]

110、120、130、140、200、710、720、730、740:存储器芯片

[0057]

111、121、131、141、711、721、731、741:第一存储体组

[0058]

111_1、112_1、121_1、122_1、131_1、132_1、141_1、142_1、711_1、712_1、721_1、722_1、731_1、732_1、741_1、742_1:第一存储体

[0059]

111_2、112_2、121_2、122_2、131_2、132_2、141_2、142_2、711_2、712_2、721_2、722_2、731_2、732_2、741_2、742_2:第二存储体

[0060]

112、122、132、142、712、722、732、742:第二存储体组

[0061]

113、123、133、143、207、713、723、733、743:读取放大器

[0062]

114、124、134、144、208、714、724、734、744:写入放大器

[0063]

115、116、125、126、135、136、145、146:子输入/输出总线

[0064]

203:全局数据线

[0065]

204_1、204_n:局部数据线

[0066]

205、206:全局数据线放大器

[0067]

210_1、210_n:子存储器阵列

[0068]

220_1、220_n:感测放大器

[0069]

311、312、313、314、315、321、322、323、324、325、411、412、413、414、415、421、422、423、424、425、511、512、513、514、515、521、522、523、524、525、611、612、613、614、615、621、622、623、624、625:时段

[0070]

701:共享输入/输出总线

[0071]

715、716、725、726、735、736、745、746:内部输入/输出总线

[0072]

717、727、737、747选择器

[0073]

718、728、738、748:子共享输入/输出总线

[0074]

cmd、sa、sa0、sa1、ld、ld0、ld1、gd、gd0、gd1、out、in、i/o:时间顺序

[0075]

s810、s820、s830、s840:步骤

[0076]

t10、t11、t12、t13、t20、t21、t22、t23、t30、t31、t32、t33、t40、t41、t42、t43:时间点

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1