具有宽传感裕度的差动传感装置的制作方法

1.本发明关于差动传感装置,特别是一种具有宽传感裕度(margin)的差动传感装置。

背景技术:

2.电阻式随机存取内存(reram)由于低功耗及高速的特性而被广泛采用。通常,reram单元可包含储存组件,当施加适当的高压时,储存组件的电阻会改变。例如,储存组件可包含过渡金属氧化物(transition metal oxide,tmo),当施加适当的高压时,过渡金属氧化物的电阻会减小。因此,可通过施加高电压来对储存组件进行编程,且可依据储存组件的电阻来读取储存在reram单元中的数据。

3.在现有技术中,通常需要使用精确的参考电流来读取储存在reram单元中的数据。然而不同存储单元的物理特性不同,因此很难使用同一个准确的参考电流来读取所有不同的存储单元。此外,若使用不合适的参考电流,则读取裕度会很小,较小的读取裕度会减慢读取过程,影响reram的效率。

技术实现要素:

4.本发明是有关于一种差动传感装置,包含第一参考单元、第二参考单元、第一路径选择器、第二路径选择器、第三路径选择器、第四路径选择器、第一取样电路、第二取样电路、第三取样电路及第四取样电路。第一参考单元用以提供第一参考电流。第二参考单元用以提供第二参考电流。第一路径选择器耦接于第一传感节点、第二参考单元及第一存储单元。第二路径选择器耦接于第二传感节点、第一参考单元及第一存储单元。第三路径选择器耦接于第三传感节点、第一参考单元及第二存储单元。第四路径选择器耦接于第四传感节点、第二参考单元及第二存储单元。第一取样电路耦接于第一传感节点,用以在取样操作期间取样由第一存储单元产生的第一单元电流。第二取样电路耦接于第二传感节点,用以在取样操作期间取样第一参考电流。第三取样电路耦接于第三传感节点,用以在取样操作期间取样由第二存储单元产生的第二单元电流。第四取样电路耦接于第四传感节点,用以在取样操作期间取样第二参考电流。第一参考电流小于第二参考电流。在竞争操作中,第一传感节点的电压依据第一单元电流及第二参考电流之间的竞争而稳定,第二传感节点的电压依据第一参考电流及第一单元电流之间的竞争而稳定,第三传感节点的电压依据第二单元电流及第一参考电流之间的竞争而稳定,及第四传感节点的电压依据第二参考电流及第二单元电流之间的竞争而稳定。

附图说明

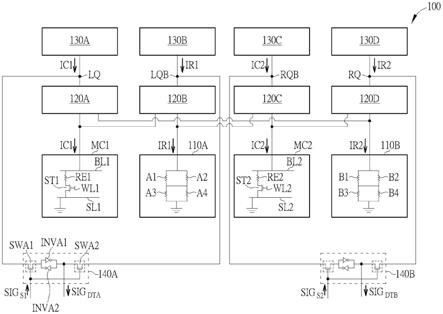

5.图1显示本发明实施例中的一种差动传感装置。

6.图2显示本发明实施例中的另一种差动传感装置。

7.其中,附图标记说明如下:

8.100,200:差动传感装置

9.110a,110b:参考单元

10.120a,120b,120c,120d,220a,220b,220c,220d:路径选择器

11.130a,130b,130c,130d,230a,230b,230c,230d:取样电路

12.140a,140b:传感放大器

13.a1,a2,a3,a4,b1,b2,b3,b4,re1,re2:电阻组件

14.bl1,bl2:位线

15.c1:电容

16.ic1,ic2:单元电流

17.inva1,inva2:反相器

18.ir1,ir2:参考电流

19.lq,lqb,rq,rqb:传感节点

20.mc1,mc2:存储单元

21.n1,n2,n3,n4:n型晶体管

22.sig

dta

,sig

dtb

:数据信号

23.sig

s1

,sig

s2

,sig

ctrl1

,sig

ctrl2

,sig

ctrl3

:控制信号

24.sl1,sl2:源极线

25.st1,st2,t1:晶体管

26.swa1,swa2,sw1,sw2,sw3:开关

27.vb1:偏压

28.vdd:电压端

29.wl1,wl2:字线

具体实施方式

30.图1显示本发明实施例中的一种差动传感装置100。差动传感装置100包含参考单元110a及110b、路径选择器120a、120b、120c及120d以及取样电路130a、130b、130c及130d。在一些实施例中,差动传感装置100可用于读取储存在存储单元mc1及mc2中的数据。

31.参考单元110a可提供参考电流ir1,且参考单元110b可提供参考电流ir2。在一些实施例中,存储单元mc1及mc2可以是电阻性随机存取内存(resistive random

‑

access memory,reram)单元。例如,存储单元mc1可包含电阻组件re1及选择晶体管st1。电阻组件re1具有第一端,耦接于位线bl1,及第二端。选择晶体管st1具有第一端,耦接于电阻组件re1的第二端;第二端,耦接于源极线sl1;及控制端,耦接于字线wl1。

32.类似地,存储单元mc2可包含电阻组件re2及选择晶体管st2。电阻组件re2具有第一端,耦接于位线bl2,及第二端。选择晶体管st2具有第一端,耦接于电阻组件re2的第二端;第二端,耦接于源极线sl2;及控制端,耦接于字线wl2。

33.在此情况下,参考电流ir1可用于模拟由高电阻的电阻型随机存取内存产生的单元电流,而参考电流ir2可用于模拟由低电阻的电阻型随机存取内存产生的单元电流。例如,参考单元110a可包含至少一具有高电阻的电阻组件,且参考单元110b可包含至少一具有低电阻的电阻组件。

34.在图1中,参考单元110a包含四个具有高电阻的电阻组件a1、a2、a3及a4。此外,并联的电阻组件a1及a2可与并联的电阻组件a3及a4串接。因此可平均四个电阻组件a1至a4的电阻变化,且参考单元110a的总电阻可用作高电阻存储单元的通用参考值。类似地,参考单元110b可包含具有低电阻的四个电阻组件b1、b2、b3及b4,以针对低电阻存储单元产生通用仿真结果。在此情况下,参考单元110a提供的参考电流ir1会小于参考单元110b提供的参考电流ir2。在一些实施例中,参考单元110a及110b可包含更多的电阻组件,用以依据系统要求提供通用参考值。然而,在一些其他实施例中,参考单元110a及110b可各自包含一个电阻组件以减小电路面积。另外,在图1中,路径选择器120a可耦接于传感节点lq、参考单元110b及存储单元mc1。路径选择器120b可耦接于传感节点lqb、参考单元110a及存储单元mc1。路径选择器120c可耦接于传感节点rqb、参考单元110a及存储单元mc2。路径选择器120d可耦接于传感节点rq、参考单元110b及存储单元mc2。

35.此外在图1中,取样电路130a可耦接于传感节点lq,取样电路130b可耦接于传感节点lqb,取样电路130c可耦接于传感节点rqb,并且取样电路130d可耦接于传感节点rq。

36.在一些实施例中,当使用差动传感装置100读取储存在存储单元mc1及mc2中的数据时,差动传感装置100可先执行取样操作。在取样操作期间,路径选择器120a可在传感节点lq及存储单元mc1之间形成电连接,并且路径选择器120b可在传感节点lqb及参考单元110a之间形成电连接。而且,路径选择器120c可在传感节点rqb及存储单元mc2之间形成电连接,且路径选择器120d可在传感节点rq及参考单元110b之间形成电连接。在此情况下,在取样操作期间,取样电路130a可取样存储单元mc1产生的单元电流ic1,取样电路130b可取样参考电流ir1,取样电路130c可取样存储单元mc2产生的单元电流ic2,及取样电路130d可取样参考电流ir2。因此,在取样操作之后,传感节点lq的电压会依据单元电流ic1而被调节为稳定值,且传感节点lqb的电压会依据参考电流ir1而被调节为稳定值。类似地,传感节点rqb及rq的电压会分别依据单元电流ic2及参考电流ir2而被调整为稳定值。在一些实施例中,在取样操作之后会执行竞争操作以比较单元电流ic1及ic2及参考电流ir1及ir2,进而判定储存在存储单元mc1及mc2中的数据。

37.在竞争操作期间,依据单元电流ic1及参考电流ir2之间的竞争来稳定传感节点lq的电压,依据参考电流ir1及单元电流ic1之间的竞争来稳定传感节点lqb的电压,依据单元电流ic2及参考电流ir1之间的竞争来稳定传感节点rqb的电压,及依据参考电流ir2及单元电流ic2之间的竞争来确定传感节点rq的电压。因此,差动传感装置100可传感传感节点lq,lqb,rqb及rq的电压,以读取储存在存储单元mc1及mc2中的数据。

38.例如,在竞争操作期间,路径选择器120a可在传感节点lq及参考单元110b之间形成电连接,且路径选择器120b可在传感节点lqb及存储单元mc1之间形成电连接。此外,在竞争操作期间,取样电路130a可保持单元电流ic1且取样电路130b可保持参考电流ir1。在此情况下,若参考电流ir2大于单元电流ic1,则参考电流ir2会下拉传感节点lq的电压。然而,若参考电流ir2小于单元电流ic1,则单元电流ic1会抬升传感节点lq的电压。即传感节点lq的电压可用于表示单元电流ic1减去参考电流ir2的结果。类似地,传感节点lqb的电压可用于表示参考电流ir1减去单元电流ic1的结果。

39.在本实施例中,参考电流ir1小于参考电流ir2。因此,若存储单元mc1具有低电阻,则单元电流ic1会略小于或等于基准电流ir2,且会显着大于基准电流ir1。在此情况下,当

传感节点lqb的电压下降时,传感节点lq的电压可能不会发生显着改变。然而,若存储单元mc1具有高电阻,则单元电流ic1会略大于或等于参考电流ir1,且会显着小于参考电流ir2。在此情况下,传感节点lq的电压会下降而传感节点lqb的电压可能不会发生显着变化。

40.即当存储单元mc1具有低电阻时,传感节点lq的电压会大于传感节点lqb的电压。此外,当存储单元mc1具有高电阻时,传感节点lq的电压会小于传感节点lqb的电压。因此,通过观察传感节点lq及lqb的电压之间的关系可识别存储单元mc1的电阻,从而读取储存在存储单元mc1中的数据。在一些实施例中,差动传感装置100可还包含传感放大器140a。传感放大器140a可耦接于传感节点lq及lqb。传感放大器140a可依据传感节点lq及lqb之间的压差输出与存储单元mc1相对应的数据信号sig

dta

。

41.如图1所示,传感放大器140a可用交叉耦接的反相器来实现。例如,传感放大器140a可包含开关swa1及swa2及反相器inva1及inva2。开关swa1具有第一端,耦接于传感节点lq;第二端;及控制端,用以接收控制信号sig

s1

。开关swa2具有第一端,耦接于传感节点lqb;第二端;及控制端,用以接收控制信号sig

s1

。反相器inva1具有输入端,耦接于开关swa1的第二端;及输出端,耦接于开关swa2的第二端。反相器inva2具有输入端,耦接于开关swa2的第二端;及输出端,耦接于开关swa1的第二端。在一些实施例中,控制信号开关swa1及swa2可在取样操作期间依据控制信号sig

s1

截止,且可在竞争操作期间当传感节点lq及lqb的电压已达到稳定值时导通。当开关swa1及swa2导通时,反相器inva1及inva2可增大传感节点lq及lqb的电压之间的差值且很快达到锁存状态。因此,传感放大器140a可相应地通过反相器inva1的输出端及/或反相器inva2的输出端输出数据信号。

42.类似地,在竞争操作期间,路径选择器120c可在传感节点rqb及参考单元110a之间形成电连接,且路径选择器120d可在传感节点rq及存储单元mc2之间形成电连接。此外,在竞争操作期间,取样电路130c可保持单元电流ic2,并且取样电路130d可保持参考电流ir2。在此情况下,传感节点rqb的电压可用以表示单元电流ic2减去参考电流ir1的结果。类似地,传感节点rq的电压可用以表示参考电流ir2减去单元电流ic2的结果。

43.因此,若存储单元mc2具有低电阻,则单元电流ic2会略小于或等于基准电流ir2,且将明显大于基准电流ir1。在此情况下,当传感节点rqb的电压上升时,传感节点rq的电压可能不会发生显着改变。然而,若存储单元mc2具有高电阻,则单元电流ic2会略大于或等于参考电流ir1,且会显着小于参考电流ir2。在此情况下,传感节点rq的电压会上升而传感节点rqb的电压可能不会发生显着变化。

44.即当存储单元mc2具有低电阻时,传感节点rqb的电压会大于传感节点rq的电压。另外,当存储单元mc2具有高电阻时,传感节点rqb的电压会小于传感节点rq的电压。因此,通过观察传感节点rq及rqb的电压之间的关系可辨识存储单元mc2的电阻,从而读取储存在存储单元mc2中的数据。在一些实施例中,差动传感装置100可还包含传感放大器140b。传感放大器140b可耦接于传感节点rq及rqb。传感放大器140b可由控制信号sig

s2

控制,并依据传感节点rq及rqb之间的压差输出与存储单元mc2相对应的数据信号sig

dtb

。

45.在此情况下,差动传感装置100可与传感放大器140a及140b并行读取储存在两个存储单元mc1及mc2中的数据,同时可共享取样及提供参考电流ir1及ir2的硬件,进而减少差动传感装置100所需的电路面积,同时提高差动传感装置100的读取效率。此外,由于参考单元110a及110b可提供参考电流ir1及ir2以分别仿真由高电阻存储单元及低电阻存储单

元产生的电流,因此可增加传感裕度(margin),从而提高传感精度。

46.然而,在一些实施例中,若适当地选择高电阻存储单元相对应的电流及低电阻存储单元相对应的电流之间的中点做为参考电流ir1及ir2,则参考单元110a及110b提供的参考电流ir1及ir2也可相同。此外,尽管在图1中显示存储单元mc1及mc2是电阻性随机存取存储(resistive random

‑

access memory,reram)单元,在一些其他实施例中,存储单元mc1及mc2亦可是磁阻随机存取存储(magnetoresistive random

‑

access memory,mram)单元,且参考单元110a及110b可包含用以相应模拟高阻值及低电阻存储单元的磁阻组件。

47.图2显示本发明实施例中的另一种差动传感装置200。在一些实施例中,差动传感装置100及200可具有相似的结构且可以相似的原理操作。差动传感装置200包含参考单元110a及110b、路径选择器220a、220b、220c及220d以及取样电路230a、230b、230c及230d。

48.如图2所示,取样电路230a、230b、230c及230d可具有相同的结构。例如,取样电路230a可包含晶体管t1、电容c1及开关sw1。晶体管t1具有第一端,耦接于电压端vdd,第二端,耦接于传感节点lq,及控制端。电容c1具有第一端,耦接于电压端vdd,及第二端,耦接于晶体管t1的控制端。开关sw1具有第一端,耦接于晶体管t1的控制端,第二端,耦接于晶体管t1的第二端,及控制端,用以接收控制信号sig

ctrl1

。

49.此外,在图2中,路径选择器220a、220b、220c及220d可具有相同的结构。例如,路径选择器220a可包含开关sw2及sw3。开关sw2具有第一端,耦接于传感节点lq,第二端,耦接于存储单元mc1,及控制端,用以接收控制信号sig

ctrl2

。开关sw3具有第一端,耦接于传感节点lq,第二端,耦接于参考单元110b,及控制端,用以接收控制信号sig

ctrl3

。

50.在此情况下,在取样操作期间,控制信号sig

ctrl1

可导通开关sw1,控制信号sig

ctrl2

可导通开关sw2,且控制信号sig

ctrl3

可截止开关sw3。在此情况下,取样电路230a可在取样操作期间通过路径选择器220a对单元电流ic1进行取样。

51.此外,在竞争操作期间,控制信号sig

ctrl1

可截止开关sw1,控制信号sig

ctrl2

可截止开关sw2,且控制信号sig

ctrl3

可导通开关sw3。在此情况下,取样电路230a可使用电容c1来保持单元电流ic1,并将依据参考单元110b提供的参考电流ir2来调节传感节点lq的电压。

52.类似地,可利用与取样电路230a相同的控制信号sig

ctrl1

来控制取样电路230b、230c及230d。而且,可使用与路径选择器220a相同的控制信号sig

ctrl2

及sig

ctrl3

来控制路径选择器220b、220c及220d。

53.在一些实施例中,取样电路230a、230b、230c及230d中使用的晶体管t1可以是p型晶体管,且路径选择器220a、220b、220c及220d中使用的开关sw2及sw3可以是n型晶体管。

54.此外,在取样操作及竞争操作期间,由于存储单元mc1及mc2中的选择晶体管st1及st2导通且源极线sl1及sl2处于低电压,若传感节点lq及rqb的电压相当高则可对电阻组件re1及re2进行编程。因此,在图2中,差动传感装置200还包含n型晶体管n1、n2、n3及n4,用以限制由存储单元mc1及mc2及参考单元110a及110b接收的电压。

55.n型晶体管n1可具有第一端,耦接于路径选择器220a;第二端,耦接于存储单元mc1;及控制端,用以接收偏压vb1。n型晶体管n2可具有第一端,耦接于路径选择器220b,第二端,耦接于参考单元110a,及控制端,用以接收偏压vb1。n型晶体管n3可具有第一端,耦接于路径选择器220c,第二端,耦接于存储单元mc2,及控制端,用以接收偏压vb1。n型晶体管n4可具有第一端,耦接于路径选择器220d,第二端,耦接于参考单元110b,及控制端,用以接

收偏压vb1。

56.因此,可由n型晶体管n1、n2、n3及n4来限制由存储单元mc1及mc2以及参考单元110a及110b接收的电压,以限制流经存储单元mc1,mc2及参考单元110a及110b的电流。

57.综上所述,本发明实施例提供的差动传感装置可并行读取两个存储单元中储存的数据,进而共享取样及提供参考电流的硬件。因此,可减小差动传感装置所需的电路面积,并可提高差动传感装置的读取效率。

58.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1