一种擦除方法、装置及计算机可读存储介质与流程

一种擦除方法、装置及计算机可读存储介质

1.本技术是申请日为2018年08月28日、申请号为201810991139.5、发明名称为“一种擦除方法、装置及计算机可读存储介质”的中国专利申请的分案申请。

技术领域

2.本发明涉及计算机技术领域,尤其涉及一种擦除方法、装置及计算机可读存储介质。

背景技术:

3.非易失存储器比如计算机闪存,具有不需电源仍可保存数据的特性,且具有擦除和写入功能,被广泛应用于各种电子产品上,但是擦除性能没有受到更多关注。

4.对非易失存储器进行擦除时,需要擦除五次才能完成擦除操作。在擦除过程中,由于擦除时间较长且不能暂停擦除动作,将会影响随机访问的正常进行,因而影响了访问性能。

5.因此,亟需找到一种能够缩短擦除时间的技术方案。

技术实现要素:

6.有鉴于此,本发明实施例期望提供一种擦除方法、装置及计算机可读存储介质,能够缩短擦除时间。

7.本发明实施例的技术方案是这样实现的:

8.本发明实施例提供一种擦除方法,所述方法包括:

9.对存储块中存储单元进行一次擦除;

10.从预设校验电压集合中查找使得所述存储块中存储单元通过校验的第一校验电压;

11.利用所述第一校验电压,确定对所述存储块中存储单元进行第二次擦除的第一擦除电压;

12.对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除,以使所述存储单元的阈值电压范围由一次擦除后的第一阈值电压范围变为初始阈值电压范围。

13.上述方案中,所述对存储块中存储单元进行一次擦除,包括:

14.对所述存储块中存储单元进行预编程;将预编程后的存储单元作为所述存储块中待擦除的存储单元;

15.相应地,所述对存储块中存储单元进行一次擦除,包括对所述存储块中待擦除的存储单元进行一次擦除。

16.上述方案中,所述从预设校验电压集合中查找使得所述存储块中存储单元通过校验的的第一校验电压,包括:

17.从预设校验电压集合中查找第i个校验电压,对所述存储块中存储单元施加所述第i个校验电压,进行一次校验;判断所述存储块中存储单元是否通过校验;

18.当确定未通过校验时,从预设校验电压集合中查找第i+1个校验电压,对所述存储块中存储单元施加所述第i+1个校验电压,再进行一次校验;判断所述存储块中存储单元是否通过校验;以此类推;

19.将使得所述存储块中存储单元通过校验的校验电压作为第一校验电压;

20.其中,i=1,3,5,

…

n,n为正整数。

21.上述方案中,所述利用所述第一校验电压,确定对所述存储块中存储单元进行第二次擦除的第一擦除电压,包括:

22.确定所述第一校验电压和预设初始校验电压的电压差;

23.利用所述电压差,以及对所述存储块中存储单元进行一次擦除时施加的初始擦除电压,得到所述电压差与所述初始擦除电压的电压之和;

24.将得到的电压之和作为对所述存储块中存储单元进行第二次擦除的第一擦除电压。

25.上述方案中,所述对存储块中存储单元进行一次擦除,包括:

26.确定初始擦除电压;

27.对所述存储块中存储单元施加所述初始擦除电压,进行第一次擦除,以使所述存储单元的阈值电压范围变为第一阈值电压范围。

28.上述方案中,所述确定初始擦除电压之前,所述方法还包括:

29.确定待处理的存储块;

30.对所述存储块中存储单元进行预编程,以使存储单元的阈值电压范围由初始阈值电压范围变为预编程后的第二阈值电压范围;

31.相应地,所述以使所述存储单元的阈值电压范围变为第一阈值电压范围,包括:

32.以使所述存储单元的阈值电压范围由预编程后的第二阈值电压范围变为第一次擦除后的第一阈值电压范围。

33.本发明实施例提供一种擦除装置,所述装置包括:

34.擦除模块,用于对存储块中存储单元进行一次擦除;

35.查找模块,用于从预设校验电压集合中查找使得所述存储块中存储单元通过校验的的第一校验电压;

36.确定模块,用于利用所述第一校验电压,确定对所述存储块中存储单元进行第二次擦除的第一擦除电压;

37.所述擦除模块,还用于对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除,以使所述存储单元的阈值电压范围由一次擦除后的第一阈值电压范围变为初始阈值电压范围。

38.上述方案中,所述查找模块,具体用于从预设校验电压集合中查找第i个校验电压,对所述存储块中存储单元施加所述第i个校验电压,进行一次校验;判断所述存储块中存储单元是否通过校验;当确定未通过校验时,从预设校验电压集合中查找第i+1个校验电压,对所述存储块中存储单元施加所述第i+1个校验电压,再进行一次校验;判断所述存储块中存储单元是否通过校验;以此类推;将使得所述存储块中存储单元通过校验的校验电压作为第一校验电压;其中,i=1,3,5,

…

n,n为正整数。

39.上述方案中,所述确定模块,具体用于确定所述第一校验电压和预设初始校验电

压的电压差;利用所述电压差,以及对所述存储块中存储单元进行一次擦除时施加的初始擦除电压,得到所述电压差与所述初始擦除电压的电压之和;将得到的电压之和作为对所述存储块中存储单元进行第二次擦除的第一擦除电压。

40.本发明实施例提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现上面所述任一项擦除方法的步骤。

41.本发明实施例提供一种擦除装置,包括:存储器、处理器以及存储在存储器上并可在处理器上运行的计算机程序;

42.其中,所述处理器用于运行所述计算机程序时,执行上面所述任一项擦除方法的步骤。

43.本发明实施例提供的擦除方法、装置及计算机可读存储介质,对存储块中存储单元进行一次擦除;从预设校验电压集合中查找使得所述存储块中存储单元通过校验的的第一校验电压;利用所述第一校验电压,确定对所述存储块中存储单元进行第二次擦除的第一擦除电压;对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除,以使所述存储单元的阈值电压范围由一次擦除后的第一阈值电压范围变为初始阈值电压范围。本发明实施例中,当对存储块中存储单元进行第一擦除后,对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除后,可使所述存储单元的阈值电压范围由一次擦除后的第一阈值电压范围直接变为初始阈值电压范围。显然,对所述存储块中存储单元擦除两次,就可以使存储单元的阈值电压范围变为初始阈值电压范围,缩短了擦除时间。

44.另外,由于擦除两次,就可以使存储单元的阈值电压范围变为初始阈值电压范围,通过缩短擦除时间,使得随机访问可以正常进行,从而提高访问性能。

附图说明

45.图1为相关技术中对存储块中存储单元执行擦除操作的流程示意图;

46.图2为相关技术中擦除过程中存储单元的阈值电压范围的示意图;

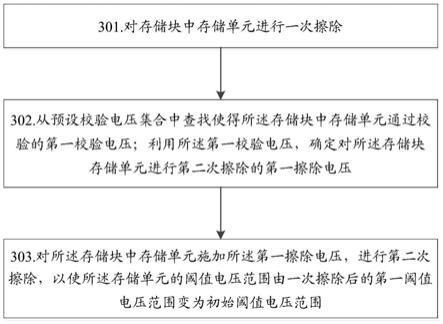

47.图3为本发明实施例擦除方法的流程示意图;

48.图4为本发明实施例擦除方法的具体实现流程示意图;

49.图5为本发明实施例擦除过程中存储块中存储单元的阈值电压的示意图;

50.图6为本发明实施例擦除装置的组成结构示意图一;

51.图7为本发明实施例擦除装置的组成结构示意图二。

具体实施方式

52.相关技术中,使用新出厂的移动闪存(mnand,mobile nand)或固态存储器时,闪存存储器件的擦除性能没有受到更多关注。比如,在擦除过程中,由于擦除时间较长且不能暂停擦除动作,如此,将会影响随机访问的正常进行。另外,当磁盘剩余空间越来越少时,数据的折叠或回收操作的高发生率导致的擦除时间较长,将会影响序列或者随机访问的性能;其中,数据的折叠操作是指通过对一个存储单元多次编程实现数据存储;数据的回收操作是指将写有数据但未被擦除过的存储单元中的废弃数据进行集中擦除处理。

53.图1是相关技术中对存储块中存储单元执行擦除操作的流程示意图,如图1所示,包括以下步骤:

54.步骤101:存储器的控制单元对存储块中存储单元进行预编程。

55.这里,在对存储块中存储单元进行擦除前,需要先进行预编程,主要是考虑到有部分存储单元可能已经写入数据,有部分存储单元可能未写入任何数据,对写入数据的存储单元进行擦除,不会对相应的存储单元产生任何不良影响,但对未写入数据的存储单元进行擦除,会产生过擦除,进而损坏存储单元。

56.步骤102:所述控制单元确定当次擦除的擦除电压。

57.擦除电压可以按照公式(1)进行计算,公式(1)如下:

58.v=pwell+stepno

×

stepsize

ꢀꢀꢀꢀ

(1)

59.其中,pwell表示初始擦除电压,为预设值,如16v;stepno表示已擦除次数;stepsize表示第一预设步长,为了实现更好的擦除效果,不宜设置过大,如设置为1v;stepno

×

stepsize表示抬升电压。

60.表1是初始擦除电压、抬升电压与擦除电压的对应关系。其中,擦除电压是按照公式(1)得到的。假设pwell为16v,stepsize为1v,则第一次擦除时,抬升电压=0

×

1=1v,擦除电压v=16+0

×

1=16v;则第二次擦除时,抬升电压=1

×

1=1v,擦除电压v=16+1

×

1=17v;则第三次擦除时,抬升电压=2

×

1=2v,擦除电压v=16+2

×

1=18v;则第四次擦除时,抬升电压=3

×

1=3v,擦除电压v=16+3

×

1=19v;则第五次擦除时,抬升电压=4

×

1=4v,擦除电压v=16+4

×

1=20v。

[0061] 初始擦除电压抬升电压擦除电压第一次擦除16v0v16v第二次擦除16v1v17v第三次擦除16v2v18v第四次擦除16v3v19v第五次擦除16v4v20v

[0062]

表1

[0063]

步骤103:所述控制单元通过字线向所述存储块中存储单元施加当次擦除的擦除电压,进行本次擦除。

[0064]

步骤104:本次擦除后,在存储单元的栅极上施加为0v的校验电压。

[0065]

步骤105:根据校验电压以及所述存储单元的初始阈值电压范围,判断校验是否通过;当校验通过时,结束擦除操作;当校验未通过时,执行步骤102。

[0066]

图2是相关技术中擦除过程中存储单元的阈值电压的示意图,如图2所示,横坐标表示存储单元的阈值电压,纵坐标表示存储单元分布;假设在出厂后,存储单元的初始阈值电压范围为(

‑

1,

‑

0.2v);按照图1所示的步骤对存储单元进行预编程后,假设存储单元的阈值电压在4v以上,显然,需要对存储块中存储单元执行5次擦除操作,才能使存储单元的阈值电压范围变为初始阈值电压范围。过长的擦除时间,加上擦除过程中不能暂停擦除动作,将会影响随机访问的正常进行。

[0067]

基于此,本发明实施例中,对存储块中存储单元进行一次擦除;从预设校验电压集合中查找使得所述存储块中存储单元通过校验的第一校验电压;利用所述第一校验电压,确定对所述存储块中存储单元进行第二次擦除的第一擦除电压;对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除,以使所述存储单元的阈值电压范围由一次擦除

后的第一阈值电压范围变为初始阈值电压范围。

[0068]

为了能够更加详尽地了解本发明实施例的特点与技术内容,下面结合附图对本发明实施例的实现进行详细阐述,所附附图仅供参考说明之用,并非用来限定本发明。

[0069]

如图3所示,详细说明本发明实施例擦除方法,本实施例的擦除方法应用于三维(3d,three dimensional)与非(nand)存储器,包括以下步骤:

[0070]

步骤301:对存储块中存储单元进行一次擦除。

[0071]

所述3d nand由存储单元阵列构成;所述存储单元阵列包括多个存储单元串;每个存储单元串包括多个存储单元,多个存储单元被布置为多个行和多个列。其中,多个列对应的方向为z方向,即存储单元串的排列方向;多个行对应的方向为x方向,即字线方向;与z方向垂直的方向为y方向,即位线方向。

[0072]

其中,所述存储块可以由多个存储单元串构成,比如6个存储单元串;每个存储单元串包括多个存储单元,比如128个存储单元;所述多个存储单元可以被布置为多个行和多个列。所述3d nand可以包括控制单元和存储单元;其中,所述控制单元可以是3d nand内部的控制单元,也可以是设置在3d nand外部的控制单元;所述存储单元用于储存数据;所述控制单元能够对所述3d nand中的存储块进行编程和擦除,且在编程和擦过程中,所述存储块中存储单元的阈值电压会在一定范围内发生改变。

[0073]

在一实施例中,所述对存储块中存储单元进行一次擦除,包括:确定初始擦除电压;对所述存储块中存储单元施加所述初始擦除电压,进行第一次擦除,以使所述存储块中存储单元的阈值电压范围变为第一阈值电压范围。

[0074]

其中,以存储块为单位进行擦除,也就是对所述存储块中所有存储单元进行擦除;所述初始擦除电压,为预设值,如16v。

[0075]

在一实施例中,所述确定初始擦除电压之前,所述方法还包括:确定待处理的存储块;对所述存储块中存储单元进行预编程,以使存储单元的阈值电压范围由初始阈值电压范围变为预编程后的第二阈值电压范围。其中,所述第二阈值电压范围的起始电压为存储单元的导通电压。

[0076]

这里,所述控制单元可以通过字线、位线确定待处理的存储块。

[0077]

为了能够对所述存储块中所有存储单元进行擦除,在擦除之前需要对所述存储块中存储单元进行预编程,可避免对所述存储块中所有存储单元同时施加擦除电压时,部分未写入数据的存储单元出现过擦除现象的发生。

[0078]

这里,当对所述存储块存储单元进行预编程后,存储单元的阈值电压范围由初始阈值电压范围变为预编程后的第二阈值电压范围。

[0079]

步骤302:从预设校验电压集合中查找使得所述存储块中存储单元通过校验的第一校验电压;利用所述第一校验电压,确定对所述存储块存储单元进行第二次擦除的第一擦除电压。

[0080]

其中,所述预设校验电压集合包括至少一个电压值;所述至少一个电压值中的最小电压值即初始校验电压,可以由用户根据存储单元的工艺进行设置;所述指示一个电压值中的最大电压值,可以由用户根据存储单元的导通电压进行设置;所述预设校验电压集合包括多个电压值时,每两个相邻电压值之间的步长值等于第二预设步长,比如1v。所述存储块中的不同存储单元对应的所述预设校验电压集合可能相同,也可能不同。

[0081]

举例来说,假设存储单元1、2的导通电压均为4v;针对存储单元1,设置初始校验电压为0v,并作为预设校验电压集合中的第一个电压值,基于第二预设步长值1v,可以得到预设校验电压集合为:{0v,1v,2v,3v,4v};针对存储单元2,设置初始校验电压为1v,并作为预设校验电压集合中的第一个电压值,基于第二预设步长值1v,可以得到预设校验电压集合为:{1v,2v,3v,4v}。

[0082]

在一实施例中,所述从预设校验电压集合中查找使得所述存储块中存储单元通过校验的第一校验电压,包括:从预设校验电压集合中查找第i个校验电压,对所述存储块中存储单元施加所述第i个校验电压,进行一次校验;判断所述存储块中存储单元是否通过校验;当确定未通过校验时,从预设校验电压集合中查找第i+1个校验电压,对所述存储块中存储单元施加所述第i+1个校验电压,再进行一次校验;判断所述存储块中存储单元是否通过校验;以此类推;将使得所述存储块中存储单元通过校验的校验电压作为第一校验电压;其中,i=1,3,5,

…

n,n为正整数。

[0083]

这里,以存储块中存储单元串为单位进行校验。

[0084]

为了避免当使用一个校验电压进行校验失败时就立即进行下一次的擦除操作,造成擦除次数过多的情况发生,可以从预设校验电压集合中查找使得所述存储块中存储单元通过校验的校验电压。

[0085]

实际应用时,进行第一次校验时,可以从预设校验电压集合中查找第1个校验电压即初始校验电压;对所述存储单元串中各个存储单元施加所述初始校验电压,进行一次校验;检测存储单元串上流通的电流;当检测的电流大于参考电流时,则确定所述各个存储单元通过校验,将相应校验电压作为第一校验电压;否则,基于初始校验电压和第二预设步长,得到抬升后的校验电压;基于所述抬升后的校验电压,对所述存储块中存储单元进行第二次校验。

[0086]

进行第二次校验时,对所述存储单元串中各个存储单元施加所述抬升后的校验电压;检测存储单元串上流通的电流;当检测的电流大于参考电流时,则确定所述各个存储单元通过校验;否则,基于第二预设步长,对所述抬升后的校验电压进行抬升,作为下次校验的校验电压。

[0087]

以此类推,通过多次校验,可以查找到使得所述存储块中存储单元通过校验的校验电压,并将通过校验的校验电压作为第一校验电压。

[0088]

在一实施例中,所述利用所述第一校验电压,确定对所述存储块存储单元进行第二次擦除的第一擦除电压,包括:确定所述第一校验电压和预设初始校验电压的电压差;利用所述电压差,以及对所述存储块存储单元进行一次擦除时施加的初始擦除电压,得到所述电压差与所述初始擦除电压的电压之和;将得到的电压和作为对所述存储块存储单元进行第二次擦除的第一擦除电压。

[0089]

为了避免对存储单元进行过多次数的循环擦除操作,利用所述第一校验电压和预设初始校验电压的电压差,对所述初始擦除电压进行抬升,得到第二次擦除的第一擦除电压。对所述存储块中所有存储单元施加所述第一擦除电压后,可以直接完成对所述存储块的擦除操作,也就是使所述存储块中存储单元的阈值电压范围变为初始阈值电压范围,显然,能避免过多次数的循环擦除操作,减小擦除时间。

[0090]

步骤303:对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除,以

使所述存储单元的阈值电压范围由一次擦除后的第一阈值电压范围变为初始阈值电压范围。

[0091]

实际应用时,可以通过3d nand中的控制单元对所述存储块中所有存储单元施加所述第一擦除电压,从而加快存储单元中存储的电荷向衬底方向移动,进而使存储单元的阈值电压范围能够直接变为初始阈值电压范围。

[0092]

需要说明的是,本发明实施例提供的擦除方法,可以通过3d nand中的状态机或者固件(firmware)实现。

[0093]

采用本发明实施例的技术方案,当对存储块中存储单元进行第一擦除后,对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除后,可使所述存储单元的阈值电压范围由第一次擦除后的第一阈值电压范围变为初始阈值电压范围。显然,对所述存储块存储单元擦除两次,就可以使存储单元的阈值电压范围变为初始阈值电压范围,缩短了擦除时间。

[0094]

另外,由于擦除两次,就可以使存储单元的阈值电压范围变为初始阈值电压范围,通过缩短擦除时间,使得随机访问可以正常进行,从而提高访问性能。

[0095]

下面以具体实施例为例,详细说明本发明实施例擦除方法的具体实施过程和原理。

[0096]

图4是本发明实施例擦除方法的具体实现流程示意图,如图4所示,以对3d nand进行擦除为例,具体包括以下步骤:

[0097]

步骤401:3d nand的控制单元对存储块中存储单元进行预编程。

[0098]

这里,在对存储块中存储单元进行擦除前,需要先进行预编程,主要是考虑到有部分存储单元可能已经写入数据,有部分存储单元可能未写入任何数据,对写入数据的存储单元进行擦除,不会对相应的存储单元产生任何不良影响,但对未写入数据的存储单元进行擦除,会产生过擦除,进而损坏存储单元。

[0099]

步骤402:所述控制单元确定当次擦除的擦除电压。

[0100]

第一次擦除时的擦除电压按照步骤102中的公式(1)进行计算,假设pwell为16v,stepsize为1v,则第一次擦除时的擦除电压v=16+0

×

1=16v。第二次擦除时的擦除电压按照公式(2)进行计算。

[0101]

第二次擦除时的擦除电压按照公式(2)进行计算,公式(2)如下:

[0102]

v=pwell+(vtop

‑

ev)=pwell+vdelta

ꢀꢀꢀꢀ

(2)

[0103]

其中,pwell表示初始擦除电压;vdelta=vtop

‑

ev,vtop表示使得所述存储块中存储单元通过校验的第一校验电压,ev表示初始校验电压,为预设值。

[0104]

表2是擦除电压与校验电压的对应关系。其中,第二次擦除时的擦除电压是按照公式(2)得到的。第二次擦除时,假设pwell为16v,初始校验电压为0v,经过多次校验得到的第一校验电压为4v,则vdelta=4

‑

0=4v,第二次擦除时的擦除电压v=16+4=20v。

[0105] 初始擦除电压校验电压集合擦除电压第二次擦除16v{0v,1v,2v,3v,4v}20v

[0106]

表2

[0107]

步骤403:所述控制单元向所述存储块中存储单元施加当次擦除时的擦除电压,进行本次擦除。

[0108]

以存储块为单位进行擦除,即所述控制单元在所述存储块中所有存储单元的衬底上施加擦除电压,进行擦除。

[0109]

步骤404:本次擦除后,所述控制单元对所述存储块中存储单元施加校验电压即0v。

[0110]

以存储块中存储单元串为单位进行校验,即所述控制单元通过字线(wl)向所述存储块的存储单元串中各个存储单元的栅极上施加初始校验电压。所述初始校验电压是用户预先设置的,比如0v或者1v等等。

[0111]

步骤405:判断校验是否通过;当校验通过时,结束擦除操作;当校验未通过时,执行步骤406。

[0112]

检测存储单元串上流通的电流;当检测的电流大于参考电流时,则确定所述存储块中存储单元通过校验,并结束擦除操作;否则,执行步骤406。

[0113]

步骤406:基于第二预设步长,对校验电压进行抬升,得到下次校验的校验电压,执行步骤407。

[0114]

步骤407:判断校验是否通过;当校验通过时,执行步骤402;否则,执行步骤406。

[0115]

图5是本发明实施例擦除过程中存储块存储单元的阈值电压发生改变的示意图,如图5所示,横坐标表示存储单元的阈值电压,纵坐标表示存储单元分布;假设在出厂后,存储单元的初始阈值电压范围为(

‑

1,

‑

0.2v);按照图4所示的擦除流程对存储单元进行预编程后,存储单元的阈值电压在4v以上;对存储块存储单元执行2次擦除操作,就能使存储单元的阈值电压范围变为初始阈值电压范围。其中,擦除电压的周期为914us,校验电压的周期为65us,存储块包括6个存储单元串,擦除时间和校验时间的总时间为4168us。

[0116]

需要说明的是,相关技术中,擦除时间和校验时间的总时间为6520us,擦除次数为5次,显然,本发明实施例,能缩短擦除时间,从而可保证随机访问的正常进行,进而提高访问性能。

[0117]

基于本技术各实施例提供的擦除方法,本发明实施例还提供一种擦除装置,如图6所示,所述装置包括:

[0118]

擦除模块61,用于对存储块中存储单元进行一次擦除;

[0119]

查找模块62,用于从预设校验电压集合中查找使得所述存储块中存储单元通过校验的第一校验电压;

[0120]

确定模块63,用于利用所述第一校验电压,确定对所述存储块中存储单元进行第二次擦除的第一擦除电压;

[0121]

所述擦除模块61,还用于对所述存储块中存储单元施加所述第一擦除电压,进行第二次擦除,以使所述存储单元的阈值电压范围由一次擦除后的第一阈值电压范围变为初始阈值电压范围。

[0122]

在一实施例中,所述擦除模块61,具体用于确定初始擦除电压;对所述存储块中存储单元施加所述初始擦除电压,进行第一次擦除,以使所述存储块中存储单元的阈值电压范围变为第一阈值电压范围。

[0123]

所述装置还包括:预编程模块;其中,

[0124]

所述预编程模块,用于确定待处理的存储块;对所述存储块中存储单元进行预编程,以使存储单元的阈值电压范围由初始阈值电压范围变为预编程后的第二阈值电压范

围。其中,所述第二阈值电压范围的起始电压为存储单元的导通电压。

[0125]

在一实施例中,所述查找模块62,具体用于从预设校验电压集合中查找第i个校验电压,对所述存储块中存储单元施加所述第i个校验电压,进行一次校验;判断所述存储块中存储单元是否通过校验;当确定未通过校验时,从预设校验电压集合中查找第i+1个校验电压,对所述存储块中存储单元施加所述第i+1个校验电压,再进行一次校验;判断所述存储块中存储单元是否通过校验;以此类推;将使得所述存储块中存储单元通过校验的校验电压作为第一校验电压;其中,i=1,3,5,

…

n,n为正整数。

[0126]

在一实施例中,所述确定模块63,具体用于确定所述第一校验电压和预设初始校验电压的电压差;利用所述电压差,以及对所述存储块中存储单元进行一次擦除时施加的初始擦除电压,得到所述电压差与所述初始擦除电压的电压之和;将得到的电压之和作为对所述存储块中存储单元进行第二次擦除的第一擦除电压。

[0127]

这里,所述擦除模块61对所述存储块中所有存储单元施加所述第一擦除电压,从而加快存储单元中存储的电荷向衬底方向移动,进而使存储单元的阈值电压范围能够直接变为初始阈值电压范围。

[0128]

需要说明的是:上述实施例提供的擦除装置在进行擦除3d nand时,仅以上述各程序模块的划分进行举例说明,实际应用中,可以根据需要而将上述处理分配由不同的程序模块完成,即将装置的内部结构划分成不同的程序模块,以完成以上描述的全部或者部分处理。另外,上述实施例提供的擦除装置与擦除方法实施例属于同一构思,其具体实现过程详见方法实施例,这里不再赘述。

[0129]

在实际应用中,擦除模块61、查找模块62、确定模块63可由位于擦除装置上的处理器比如中央处理器(cpu,central processing unit)、微处理器(mpu,micro processor unit)、数字信号处理器(dsp,digital signal processor)、或现场可编程门阵列(fpga,field programmable gate array)等实现。

[0130]

图7是本发明擦除装置的结构示意图,图7所示的擦除装置700包括:至少一个处理器701、存储器702、用户接口703、至少一个网络接口704。擦除装置700中的各个组件通过总线系统705耦合在一起。可理解,总线系统705用于实现这些组件之间的连接通信。总线系统705除包括数据总线之外,还包括电源总线、控制总线和状态信号总线。但是为了清楚说明起见,在图7中将各种总线都标为总线系统705。

[0131]

其中,用户接口703可以包括显示器、键盘、鼠标、轨迹球、点击轮、按键、按钮、触感板或者触摸屏等。

[0132]

本发明实施例中的存储器702用于存储各种类型的数据以支持擦除装置700的操作。这些数据的示例包括:用于在擦除装置700上操作的任何计算机程序,如操作系统7021和应用程序7022;其中,操作系统7021包含各种系统程序,例如框架层、核心库层、驱动层等,用于实现各种基础业务以及处理基于硬件的任务。应用程序7022可以包含各种应用程序,用于实现各种应用业务。实现本发明实施例方法的程序可以包含在应用程序7022中。

[0133]

上述本发明实施例揭示的方法可以应用于处理器701中,或者由处理器701实现。处理器701可能是一种集成电路芯片,具有信号的处理能力。在实现过程中,上述方法的各步骤可以通过处理器701中的硬件的集成逻辑电路或者软件形式的指令完成。上述的处理器701可以是通用处理器、数字信号处理器,或者其他可编程逻辑器件、分立门或者晶体管

逻辑器件、分立硬件组件等。处理器701可以实现或者执行本发明实施例中的公开的各方法、步骤及逻辑框图。通用处理器可以是微处理器或者任何常规的处理器等。结合本发明实施例所公开的方法的步骤,可以直接体现为硬件译码处理器执行完成,或者用译码处理器中的硬件及软件模块组合执行完成。软件模块可以位于存储介质中,该存储介质位于存储器702,处理器701读取存储器702中的信息,结合其硬件完成前述方法的步骤。

[0134]

可以理解,存储器702可以是易失性存储器或非易失性存储器,也可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(rom,read only memory)、可编程只读存储器(prom,programmable read

‑

only memory)、可擦除可编程只读存储器(eprom,erasable programmable read

‑

only memory)、电可擦除可编程只读存储器(eeprom,electrically erasable programmable read

‑

only memory)、磁性随机存取存储器(fram,ferromagnetic random access memory)、快闪存储器(flash memory)、磁表面存储器、光盘、或只读光盘(cd

‑

rom,compact disc read

‑

only memory);磁表面存储器可以是磁盘存储器或磁带存储器。易失性存储器可以是随机存取存储器(ram,random access memory),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用,例如静态随机存取存储器(sram,static random access memory)、同步静态随机存取存储器(ssram,synchronous static random access memory)、动态随机存取存储器(dram,dynamic random access memory)、同步动态随机存取存储器(sdram,synchronous dynamic random access memory)、双倍数据速率同步动态随机存取存储器(ddrsdram,double data rate synchronous dynamic random access memory)、增强型同步动态随机存取存储器(esdram,enhanced synchronous dynamic random access memory)、同步连接动态随机存取存储器(sldram,synclink dynamic random access memory)、直接内存总线随机存取存储器(drram,direct rambus random access memory)。本发明实施例描述的存储器702旨在包括但不限于这些和任意其它适合类型的存储器。

[0135]

基于本技术各实施例提供的擦除方法,本技术还提供一种计算机可读存储介质,参照图7所示,所述计算机可读存储介质可以包括:用于存储计算机程序的存储器702,上述计算机程序可由擦除装置700的处理器701执行,以完成前述方法所述步骤。计算机可读存储介质可以是fram、rom、prom、eprom、eeprom、flash memory、磁表面存储器、光盘、或cd

‑

rom等存储器。

[0136]

以上所述,仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1