三维存储器的确定失效沟道孔的方法及测试样品与流程

1.本发明涉及半导体技术领域,具体涉及一种三维存储器的确定失效沟道孔的方法及测试样品。

背景技术:

2.相关技术的三维存储器(3d nand)产品研发和量产过程中,经常出现字线与沟道孔(ch)之间的漏电失效,影响产品良率以及质量。通常对于此类的失效,先通过卡片测试(sort test)初步定位到失效芯片中失效块区域(block)和字线(wl)信息,并制备包含失效wl的样品,最后用扫描透射电子显微镜(stem)观察几千个沟道孔,找出与漏电字线相连的失效沟道孔,这样不仅比较费时,而且对于一些轻微漏电,较小缺陷的情况,stem表征不出缺陷,找不出失效ch,成功率低,无法帮助fab及时找出失效原因。

技术实现要素:

3.本发明的目的在于提供一种三维存储器的确定失效沟道孔的方法,能够容易检测失效沟道孔,且能够准确检测到轻微漏电和较小缺陷的失效点。

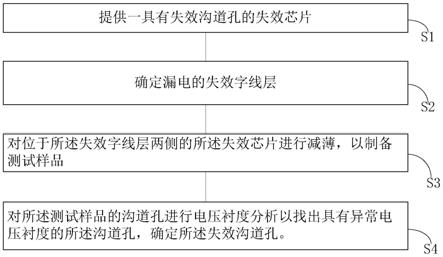

4.根据本发明实施例的三维存储器的确定失效沟道孔的方法,包括:提供一具有失效沟道孔的失效芯片;确定漏电的失效字线层,对位于所述失效字线层两侧的所述失效芯片进行减薄,以制备测试样品;对所述测试样品的沟道孔进行电压衬度分析以找出具有异常电压衬度的所述沟道孔,确定所述失效沟道孔。

5.根据本发明的一些实施例,所述失效芯片在垂直所述失效字线层的厚度方向上的两侧分别为第一表面和第二表面,对位于所述失效字线层两侧的所述失效芯片进行减薄的步骤包括:采用聚焦离子束对所述第一表面进行减薄,直至所述第一表面到所述失效字线层的厚度为第一预设厚度;采用聚焦离子束对所述第二表面进行减薄,直至所述第二表面到所述失效字线层的厚度为第二预设厚度。

6.根据本发明的一些实施例,在采用聚焦离子束对所述失效芯片的第一表面进行减薄,直至所述第一表面到所述失效字线层的厚度为第一预设厚度的步骤中,所述聚焦离子束对所述第一表面减薄至沿所述失效字线层朝向所述第一表面的方向的上相邻的字线层上。

7.根据本发明的一些实施例,对所述测试样品的沟道孔进行电压衬度分析以找出具有异常电压衬度的所述沟道孔,确定所述失效沟道孔的步骤包括:采用离子束扫描所述测试样品表面以产生电压衬度图像,多个所述沟道孔在所述电压衬度图像形成多个呈现暗亮的衬度点;根据所述电压衬度图像,寻找发亮的所述衬度点以确定所述失效沟道孔。

8.根据本发明的一些实施例,在采用聚焦离子束对所述失效芯片的第二表面进行减薄,直至所述第二表面到所述失效字线层的厚度为第二预设厚度的步骤中,所述聚焦离子束对所述第二表面减薄至沿所述失效字线层朝向所述第二表面的方向的上相邻的字线层上。

9.根据本发明的一些实施例,在确定漏电的失效字线层的步骤中采用纳米探针检测所述失效芯片的字线结构的电性参数以确定漏电的所述失效字线层。

10.根据本发明的一些实施例,在确定漏电的所述失效字线层的步骤后,在对位于所述失效字线层两侧的所述失效芯片进行减薄之前还包括:对所述失效字线层进行标记。

11.根据本发明的一些实施例,对所述失效字线层进行标记的步骤包括:对所述失效字线层进行电路修补,从所述失效字线层的栓塞端引出第一导电层,从所述衬底引出第二导电层;确定所述失效字线层和所述失效沟道孔形成的失效点所在的失效区域,并对所述失效字线层作标记。

12.根据本发明的一些实施例,在对位于所述失效字线层两侧的所述失效芯片进行减薄的步骤中对所述失效区域的两侧进行减薄。

13.根据本发明的一些实施例,采用激光诱导电阻变化显微镜确定所述失效区域,并对所述失效字线层作标记。

14.根据本发明的一些实施例,所述失效区域的宽度为5-10um。

15.根据本发明的一些实施例,采用聚焦离子束显微镜对所述测试样品的沟道孔进行电压衬度分析以找出具有异常电压衬度的所述沟道孔,确定所述失效沟道孔。

16.根据本发明的一些实施例,在采用聚焦离子束显微镜对所述测试样品的沟道孔进行电压衬度分析的步骤中使得所述聚焦离子束显微镜在不同观测电压下观测所述测试样品。

17.本发明的还提出了一种具有失效沟道孔的fib失效测试样品。

18.根据本发明实施例的具有失效沟道孔的fib失效测试样品包括失效字线层和失效沟道孔,在沿所述失效字线层的厚度方向上,所述失效字线层的两侧分别均设有1-2层字线层,所述失效沟道孔贯穿所述失效字线层和位于其两侧的所述字线层。

19.由此根据本发明实施例的三维存储器的确定失效沟道孔的方法及测试样品,在确定漏电失效字线层后,对位于失效字线层厚度方向两侧的失效芯片进行减薄,以制备测试样品,通过对减薄的测试样品进行电压衬度分析以找出失效沟道孔,由于减薄后的测试样品厚度较小,沟道孔的深度较小,对测试样品进行失效分析时,观测机台容易观测到将轻微漏电和较小缺陷的情况,而且电压衬度分析时对测试样品的表面进行扫描形成电压衬度图像,失效沟道孔和其它沟道孔在电压衬度成像上显示的明亮程度不同,例如失效沟道孔在电压衬度图像上相对其它沟道孔显示更为明亮,这样根据电压衬度图像更容易找到异常电压衬度的失效沟道孔,从而不需要对多个沟道孔进行一一观察分析,能够减少失效分析时间,也能够提高找到失效沟道孔的速率和精确度,及时有效地找到失效原因,提高产品良率和质量。

附图说明

20.图1为根据本发明的实施例的三维存储器的确定失效沟道孔的方法的流程图;

21.图2为根据本发明实施例的三维存储器的确定失效沟道孔的方法的失效芯片的结构示意图;

22.图3为根据本发明实施例的三维存储器的确定失效沟道孔的方法的测试样品的结构示意图;

23.图4为根据本发明一个实施例的三维存储器的确定失效沟道孔的方法的失效芯片的电压衬度图像;

24.附图标记;

25.100:失效芯片;

26.10:测试样品;

27.1:失效字线层,2:失效沟道孔;

28.3:朝向第一表面的上一层字线层,4:朝向第二表面的上一层字线层。

具体实施方式

29.以下结合附图和具体实施方式对本发明提出的一种三维存储器的确定失效沟道孔的方法作进一步详细说明。

30.下面参见附图描述根据本发明实施例的三维存储器的确定失效沟道孔2的方法。

31.如图1所示,根据本发明实施例的三维存储器的确定失效沟道孔2的方法可以包括提供一具有失效沟道孔2的失效芯片100;确定漏电的失效字线层1,对位于失效字线层1两侧的失效芯片100进行减薄,以制备测试样品10;对所述测试样品10的沟道孔进行电压衬度分析以找出具有异常电压衬度的所述沟道孔,确定所述失效沟道孔2。

32.如图1所示,步骤s1提供一具有失效沟道孔2的失效芯片100,所述失效芯片100为三维存储器芯片,所述三维存储器芯片内包括多个沟道孔和字线结构,沟道孔贯穿字线结构,字线结构包括多个字线层,每个字线层均与多个沟道孔接触连接,字线层与沟道孔之间容易出现漏电失效问题,本发明的方法用于确定与失效字线层1之间产生漏电的沟道孔以确定具体失效位置,以便于进行失效分析。

33.步骤s2:确定漏电失效字线层1。

34.可以通过纳米探针检测失效芯片100的字线结构的电性参数以确定漏电的所述失效字线层1,具体可通过检测字线的电阻、电流等,对失效芯片100的多个字线层进行检测,找出其中存在电性参数异常的字线层,所述电性参数异常的字线层即为存在漏电的失效字线层1。

35.在本发明的一些具体实施例中,在确定漏电的失效字线层1的步骤还包括对失效字线层1进行电路修补,从失效字线层1的栓塞端引出第一导电层,从衬底引出第二导电层,例如可采用聚离子束机台进行电路修补,以从失效字线层1的栓塞端和衬底两端分别引出5*15um大小的导电层,可以对失效导电线路所在的漏电路径的漏电方向进行测试和分析,具体地,可以通过第一导电层和第二导电层外接电路,以测试电性参数的变化关系,并进行测试分析以获得漏电路径以及漏电方向,以便于进行后续的失效分析。

36.然后确定失效点所在的失效区域,所述的失效点即失效字线层1和失效沟道孔2所在的位置,具体地,可通过激光诱导电阻变化显微镜(obirch)来确定失效点所在失效区域,所述失效区域可以为理解为失效字线层1和失效沟道孔2发生漏电的区域,失效区域的尺寸通常较大,在几个微米的范围内,通过激光诱导电阻变化显微镜(obirch)可用于失效芯片100内部电阻异常以及漏电分析,通过激光扫描失效芯片100内部的连接结构,并产生温度梯度,并产生阻值变化,经由阻值变化的比对,可定位出失效芯片100内失效点所在的失效区域。其中所述失效区域的宽度为5-10um,在一些具体示例中,可通过激光诱导电阻变化显

微镜(obirch)可将失效点所在的失效区域定位在6*6um范围内,并做好标记。

37.确定失效区域后可采用聚离子束工艺制备具有失效字线层1和失效沟道孔2的平面样品,以便于找出具体失效沟道孔2,失效芯片100在垂直失效字线层1的厚度方向上具有第一表面和第二表面。

38.结合图2和图3所示,制备测试样品10的方法包括:s3:对位于失效字线层1两侧的失效芯片100进行减薄,具体地,在确定失效字线层1后,从失效芯片100厚度方向的两侧进行减薄以靠近失效字线层1。

39.在一些示例中,失效芯片100在垂直失效字线层1的厚度方向上的两侧可分别为第一表面和第二表面,可采用聚焦离子束对第一表面进行减薄,直至第一表面到失效字线层1的厚度为第一预设厚度,采用聚焦离子束对所述第二表面进行减薄,直至所述第二表面到所述失效字线层1的厚度为第二预设厚度,以制备测试样品10。即可通过聚离子束工艺对失效芯片100的失效字线层1厚度方向的两侧进行减薄,使得第一表面和第二表面能够接近失效字线层1,以减少形成的测试样品10的厚度,使得测试样品10的沟道孔的深度减小,在后续失效分析时,能够有利于观察到测试样品10的轻微漏电和较小缺陷的情况,由此一方面能够实现通过对失效芯片100的减薄以方便对失效字线层1的失效分析,另一方面也能够防止第一表面和第二表面过于接近失效字线层1而对失效字线层1造成破坏。

40.在本发明的一些具体示例中,可采用聚焦离子束对第一表面减薄至沿失效字线层1朝向所述第一表面的方向的上相邻的字线层3上,采用聚焦离子束对第二表面减薄至沿所述失效字线层1朝向所述第二表面的方向的上相邻的字线层4上,也就是说,在采用聚离子束机台对失效芯片100的第一表面减薄时,第一表面减薄可停刀到失效字线层1朝向第一表面的上一层的字线层3上,在采用聚离子束机台对失效芯片100的第二表面减薄时,第二表面减薄可停刀到失效字线层1朝向第二表面的上一层的字线层4上,从而使得失效芯片100能够减薄至更小的厚度,也能够避免过于减薄而导致失效字线层1结构被破坏。

41.s4:对测试样品10的沟道孔进行电压衬度分析以找出具有异常电压衬度的沟道孔,确定失效沟道孔2。具体地,可采用具有一定能量的电子发射到测试样品10表面,测试样品10表面会有二次电子散射出来,通过检测这些二次电子从而电压衬度图像,失效沟道孔2与其它沟道孔在电压衬度图像的成像不同,通多对电压衬度图像分析可找出具有异常电压衬度的沟道孔以确定失效沟道孔2,从而不需要对多个沟道孔进行一一观察分析,能够快速准确的找到失效沟道孔2。

42.在一些示例中,可采用电子束或离子束扫描测试样品10的表面,当电子束(离子束)加速打到测试样品10的表面时,会与测试样品10的表面发生非弹性碰撞,在测试样品10的表面会产生二次电子,通过对二次电子的收集检测从而成像,测试样品10表面的电势会影响二次电子的产率,电位高放射二次电子量少,电位低放射二次电子量少,测试样品10表面检测二次电子量的不同则在电压衬度图像具有暗亮对比,由此多个沟道孔在电压衬度成像上可形成多个衬度点,沟道孔与失效沟道孔2的电势不同则其在电压衬度图像上的暗亮不同,根据对测试样品10表面多个沟道孔的扫描可形成多个衬度点,暗亮程度明显与其它不同的衬度点对应的沟道孔即为失效沟道孔2。

43.如图4所示为根据本发明一个实施例的三维存储器的确定失效沟道孔的方法的测试样品10的电压衬度图像,其中明显有一个亮度明显较为大的点即具有异常电压衬度的衬

度点,这样显示较为亮的位置即为异常电压衬度的沟道孔,从而能够确定为失效沟道孔2,具体地可通过采用聚焦离子束显微镜对测试样品10的沟道孔进行电压衬度分析以找出具有异常电压衬度的所述沟道孔,确定失效沟道孔2,或者也可通过电子显微镜例如扫描电子显微镜对测试样品10进行电压衬度分析。可选地,在此步骤中,聚焦离子束显微镜可在不同观测电压下观测所述测试样品10,通过在不同观测电压下观测测试样品10,从而能够精确找到异常电压衬度的沟道孔即失效沟道孔2。

44.由此根据本发明实施例的三维存储器的确定失效沟道孔2的方法,在确定漏电失效字线层1后,通过聚焦离子束工艺对失效芯片100的第一表面和第二表面分别减薄至第一预设厚度和第二预设厚度,以制备测试样品10,通过对减薄的测试样品10进行电压衬度分析以找出失效沟道孔2,由于减薄后的测试样品10厚度较小,沟道孔的深度较小,对测试样品10进行失效分析时,观测机台容易观测到将轻微漏电和较小缺陷的情况,而且电压衬度分析时电压衬度图形显示更加明显,从而容易找到异常电压衬度的失效沟道孔2,也能够提高找到失效沟道孔2的速率和精确度,有利于对失效芯片100的失效分析。

45.本发明还提出了一种具有失效沟道孔2的fib失效测试样品10。

46.根据本发明实施例的具有失效沟道孔2的fib失效测试样品10包括失效字线层1和失效沟道孔2,在沿所述失效字线层1的厚度方向上,所述失效字线层1的两侧分别均设有1-2层字线层,所述失效沟道孔2贯穿所述失效字线层1和位于其两侧的所述字线层。在如图3所示的示例中,测试样品10沿失效字线层1厚度方向上的两侧分别保留有一层字线层,这样在制备测试样品10时能够使得测试样品10能够减薄至较小的厚度,同时也能够防止测试样品10被过度减薄而导致失效字线层1结构被破坏。

47.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1