基板及其制备方法、芯片封装结构及其封装方法与流程

本发明涉及半导体封装领域,特别是涉及一种基板及其制备方法、芯片封装结构及其封装方法。

背景技术:

封装是把集成电路装配为芯片最终产品的过程,是把foundry生产出来的集成电路裸片(die)放在一块起到承载作用的基板上,把管脚引出来,然后固定包装成为一个整体。通常可以采用倒装芯片封装技术对芯片进行封装,倒装芯片封装技术是裸芯片封装技术之一,在芯片的电极区制作好金属凸柱,然后把金属凸柱与印刷基板上的电极区进行压焊连接,封装的占有面积基本上与芯片尺寸相同,是所有封装技术中体积最小、最薄的一种。但是,由于金属凸柱形成的位置不同导致金属凸柱相对于芯片的高度不统一,就会导致在压焊连接时,较低的凸柱不能与基板连接,降低芯片良率。

技术实现要素:

基于此,针对上述问题,本发明提供一种基板及其制备方法、芯片封装结构及其封装方法。

本发明提供一种基板,包括:基板本体;第一焊盘,形成于所述基板本体表面;第二焊盘,形成于所述基板本体表面;介质层,形成于所述基板本体表面,所述介质层具有第一窗口和第二窗口,所述第一窗口暴露出所述第一焊盘,所述第二窗口暴露出所述第二焊盘,所述第一窗口内具有第一空余空间,所述第二窗口内具有第二空余空间,所述第一空余空间的体积大于所述第二空余空间的体积。

上述基板的第一空余空间的体积大于第二空余空间的体积,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片无需改变,使得实施简单,易于操作,易于工业化推广。

在其中一个实施例中,所述第一焊盘的表面积大于所述第二焊盘的表面积。第一焊盘的表面积大于第二焊盘的表面积,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。

在其中一个实施例中,所述第一焊盘具有开孔。第一焊盘具有开孔,使得部分第一焊料能进入开孔内,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。

在其中一个实施例中,所述第一焊盘的厚度介于10um~15um之间。第一焊盘的厚度介于10um~15um之间,厚度小使得第一焊盘容易开孔,还能使焊料更容易进入开孔内,而且能提高第一焊盘的稳定性,使得第一焊盘不易倾斜或者脱落,还能为第一焊料提供更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。

本发明还提供一种芯片封装结构,包括:上述的基板;芯片;连通介质层,形成于所述芯片表面,所述连通介质层具有开口;第一凸柱,形成于所述连通介质层表面;第二凸柱,形成于所述开口内并与所述芯片电性连接,所述第一凸柱相对于所述连通介质层的高度高于所述第二凸柱相对于所述连通介质层的高度;所述第一凸柱与所述第一焊盘通过第一焊料固定连接,所述第二凸柱与所述第二焊盘通过第二焊料固定连接。

上述芯片的封装结构中第一空余空间的体积大于第二空余空间的体积,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片无需改变,使得实施简单,易于操作,易于工业化推广。

本发明提供一种基板的制备方法,包括:提供一基板本体,于所述基板本体表面形成第一焊盘和第二焊盘;于所述基板本体表面形成介质层,所述介质层具有第一窗口和第二窗口,所述第一窗口暴露出所述第一焊盘,所述第二窗口暴露出所述第二焊盘,所述第一窗口内具有第一空余空间,所述第二窗口内具有第二空余空间,所述第一空余空间的体积大于所述第二空余空间的体积。

上述基板的制备方法使得基板的第一空余空间的体积大于第二空余空间的体积,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片无需改变,使得实施简单,易于操作,易于工业化推广。

在其中一个实施例中,所述第一焊盘的表面积大于所述第二焊盘的表面积。第一焊盘的表面积大于第二焊盘的表面积,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。

在其中一个实施例中,所述第一焊盘具有开孔。第一焊盘具有开孔,使得部分第一焊料能进入开孔内,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。

在其中一个实施例中,所述第一焊盘的厚度介于10um~15um之间。第一焊盘的厚度介于10um~15um之间,厚度小使得第一焊盘容易开孔,还能使焊料更容易进入开孔内,而且能提高第一焊盘的稳定性,使得第一焊盘不易倾斜或者脱落,还能为第一焊料提供更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。

本发明还提供一种芯片封装方法,包括:提供一芯片,所述芯片表面形成有连通介质层,所述连通介质层具有开口,所述连通介质层表面形成有第一凸柱,所述开口内形成有第二凸柱,所述第二凸柱与所述芯片电性连接,所述第一凸柱相对于所述连通介质层的高度高于所述第二凸柱相对于所述连通介质层的高度;上述的基板的制备方法制备基板;将所述第一凸柱通过第一焊料焊接于所述第一焊盘上,将所述第二凸柱通过第二焊料焊接于所述第二焊盘上。

上述芯片封装方法使得第一空余空间的体积大于第二空余空间的体积,为第一焊料提供相比于第二焊料更大的空间,以缓冲第一凸柱与第二凸柱之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱与第一焊盘、第二凸柱与第二焊盘都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片无需改变,使得实施简单,易于操作,易于工业化推广。

附图说明

图1为本发明的基板的制备方法的流程图。

图2~图5为本发明的基板的制备方法各步骤所呈现的结构示意图。

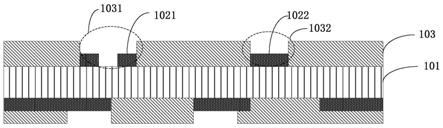

图5为本发明的基板所呈现的截面图。

图6为本发明的基板所呈现的俯视图。

图7为本发明的芯片封装方法的流程图。

图2~图5、图8~图9为本发明的芯片封装方法各步骤所呈现的结构示意图。

图9为本发明的芯片封装结构所呈现的结构示意图。

具体实施方式

为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的首选实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

在本发明的描述中,需要理解的是,术语“上”、“下”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方法或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

一个实施例,如图5~图6所示,提供一种基板,包括:基板本体101;第一焊盘1021,形成于基板本体101表面;第二焊盘1022,形成于基板本体101表面;介质层103,形成于基板本体101表面,介质层103具有第一窗口和第二窗口,所述第一窗口暴露出所述第一焊盘1021,所述第二窗口暴露出所述第二焊盘1022,第一窗口内具有第一空余空间1031,第二窗口内具有第二空余空间1032,第一空余空间1031的体积大于第二空余空间1032的体积。

在本实施例中,上述基板的第一空余空间1031的体积大于第二空余空间1032的体积,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片201无需改变,使得实施简单,易于操作,易于工业化推广。

在一个实施例中,焊盘的材质包括铜、铝、镍、金、银、钛中的一种或几种组合。基板本体101的材质包括树脂、硅、玻璃、氧化硅、陶瓷、金属中的一种或几种组合。介质层103的材质包括油墨、硬化剂、环氧树脂、硅胶、pi、pbo、pcb、氧化硅、磷硅玻璃或含氟玻璃中的一种或几种组合。介质层103能防止湿气、异物及电解质使基板氧化,防止基板受机械损伤,还能防止焊接时桥接短路。

在一个实施例中,第一焊盘1021的表面积大于第二焊盘1022的表面积。第一焊盘1021的表面积大于第二焊盘1022的表面积,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。

在一个实施例中,第一焊盘1021的表面积是第二焊盘1022的表面积的1.1倍~1.5倍,例如,第一焊盘1021的表面积是第二焊盘1022的表面积的1.3倍。

在一个实施例中,第一焊盘1021具有开孔10211。第一焊盘1021具有开孔10211,使得部分第一焊料30能进入开孔10211内,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。

在一个实施例中,开孔10211的形状包括但不限于圆形或矩形。

在一个实施例中,开孔10211的直径至少3um,例如,开孔10211的直径可以是4um、5um、6um、7um。

在一个实施例中,第一焊盘1021的厚度介于10um~15um之间,例如,第一焊盘1021的厚度可以是11um、13um、14um。第一焊盘1021的厚度介于10um~15um之间,厚度小使得第一焊盘1021容易开孔10211,还能使焊料更容易进入开孔10211内,而且能提高第一焊盘1021的稳定性,使得第一焊盘1021不易倾斜或者脱落,还能为第一焊料30提供更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。

一个实施例,如图9所示,提供一种芯片封装结构,包括:上述的基板;芯片201;连通介质层202,形成于芯片201表面,连通介质层202具有开口;第一凸柱2031,形成于连通介质层202表面;第二凸柱2032,形成于开口内并与芯片201电性连接,第一凸柱2031相对于连通介质层202的高度高于第二凸柱2032相对于所述连通介质层202的高度;第一凸柱2031与第一焊盘1021通过第一焊料30固定连接,第二凸柱2032与第二焊盘1022通过第二焊料30固定连接。

在本实施例中,上述芯片201的封装结构中第一空余空间1031的体积大于第二空余空间1032的体积,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片201无需改变,使得实施简单,易于操作,易于工业化推广。第一凸柱2031起支撑、减少应力的作用。

在一个实施例中,如图8所示,所述连通介质层202包括第三焊盘2023、保护层2022和重新布线层2024,保护层2022形成于芯片201表面,保护层2022具有第三窗口,第三焊盘2023形成于芯片201表面,第三窗口暴露出第三焊盘2023,重新布线层2024形成于保护层2022表面,重新布线层2024表面具有形成第二凸柱2032的开口2021,重新布线层2024包括图形化的第一介质层20241、图形化的金属层20242、图形化的第二介质层20243,芯片201与第二凸柱2032通过第三焊盘2023和重新布线层2024中的金属层20242电性连接。

在一个实施例中,连通介质层202的材质包括聚酰亚胺或高分子材料。连通介质层202能起到缓冲、绝缘的作用,还能防止芯片受损。第一凸柱2031和第二凸柱2032的材质包括铜、铝、镍、金、银、钛中的一种或几种组合。焊料30的材质包括锡、铜、铝、镍、金、银、钛中的一种或几种组合。

一个实施例,如图1所示,提供一种基板的制备方法,包括:提供一基板本体101,于基板本体101表面形成第一焊盘1021和第二焊盘1022;于基板本体101表面形成介质层103,介质层103具有第一窗口和第二窗口,所述第一窗口暴露出所述第一焊盘1021,所述第二窗口暴露出所述第二焊盘1022,第一窗口内具有第一空余空间1031,第二窗口内具有第二空余空间1032,第一空余空间1031的体积大于第二空余空间1032的体积。

在本实施例中,上述基板的制备方法使得基板的第一空余空间1031的体积大于第二空余空间1032的体积,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片201无需改变,使得实施简单,易于操作,易于工业化推广。

s11:提供一基板本体101,于基板本体101表面形成第一焊盘1021和第二焊盘1022。

在一个实施例中,步骤s11包括:

s111:如图2所示,提供一基板本体101,如图3所示,于基板本体101表面形成焊盘材料层102;

s112:如图4所示,采用光刻工艺刻蚀焊盘材料层102,以形成第一焊盘1021和第二焊盘1022。

在一个实施例中,焊盘材料层102包括铜箔,在步骤s111之前还包括:对铜箔进行粗化处理。粗化处理是采用化学液对铜箔进行微腐蚀。粗化处理能增加铜箔的表面积,还能提高铜箔跟基板本体101的结合力,防止分层。

在一个实施例中,步骤s112之后还包括:采用电镀或化学镀工艺于第一焊盘1021和第二焊盘1022的表面形成镍、金或有机保焊膜(osp)。

在一个实施例中,步骤s112还包括:采用光刻工艺刻蚀焊盘材料层,以在第一焊盘1021上形成开孔10211。第一焊盘1021具有开孔10211,使得部分第一焊料30能进入开孔10211内,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。

在一个实施例中,焊盘的材质包括铜、铝、镍、金、银、钛中的一种或几种组合。形成焊盘的方法包括物理气相沉积或化学气相沉积。基板本体101的材质包括树脂、硅、玻璃、氧化硅、陶瓷、金属中的一种或几种组合。

在一个实施例中,开孔10211的形状包括但不限于圆形或矩形。

在一个实施例中,开孔10211的直径至少3um,例如,开孔10211的直径可以是4um、5um、6um、7um。

在一个实施例中,第一焊盘1021的表面积大于第二焊盘1022的表面积。第一焊盘1021的表面积大于第二焊盘1022的表面积,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。

在一个实施例中,第一焊盘1021的表面积是第二焊盘1022的表面积的1.1倍~1.5倍,例如,第一焊盘1021的表面积是第二焊盘1022的表面积的1.3倍。

在一个实施例中,第一焊盘1021的厚度介于10um~15um之间,例如,第一焊盘1021的厚度可以是11um、13um、14um。第一焊盘1021的厚度介于10um~15um之间,厚度小使得第一焊盘1021容易开孔10211,还能使焊料更容易进入开孔10211内,而且能提高第一焊盘1021的稳定性,使得第一焊盘1021不易倾斜或者脱落,还能为第一焊料30提供更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。

s12:如图5所示,于基板本体101表面形成介质层103,介质层103具有第一窗口和第二窗口,第一焊盘1021位于第一窗口内,第二焊盘1022位于第二窗口内,第一窗口内具有第一空余空间1031,第二窗口内具有第二空余空间1032,第一空余空间1031的体积大于第二空余空间1032的体积。

在一个实施例中,步骤s12包括:

s121:于基板本体101表面及第一焊盘1021和第二焊盘1022表面形成介质层103;

s122:以光刻工艺形成第一窗口和第二窗口,以暴露出第一焊盘1021和第二焊盘1022。

在一个实施例中,介质层103的材质包括油墨、硬化剂、环氧树脂、硅胶、pi、pbo、pcb、氧化硅、磷硅玻璃或含氟玻璃中的一种或几种组合。形成介质层103的方法包括旋涂或cvd。介质层103能防止湿气、异物及电解质使基板氧化,防止基板受机械损伤,还能防止焊接时桥接短路。

一个实施例,如图7所示,提供一种芯片封装方法,包括:提供一芯片201,芯片201表面形成有连通介质层202,连通介质层202具有开口,连通介质层202表面形成有第一凸柱2031,开口内形成有第二凸柱2032,第二凸柱2032与芯片201电性连接,第一凸柱2031相对于连通介质层202的高度高于第二凸柱2032相对于所述连通介质层202的高度;上述的基板的制备方法制备基板;将第一凸柱2031通过第一焊料30焊接于第一焊盘1021上,将第二凸柱2032通过第二焊料30焊接于第二焊盘1022上。

在本实施例中,上述芯片201封装方法使得第一空余空间1031的体积大于第二空余空间1032的体积,为第一焊料30提供相比于第二焊料30更大的空间,以缓冲第一凸柱2031与第二凸柱2032之间的高度差,以达到共面性,使得在焊接阶段,第一凸柱2031与第一焊盘1021、第二凸柱2032与第二焊盘1022都能很好的固定连接,提高焊接性能。而且本发明是对基板进行改进,芯片201无需改变,使得实施简单,易于操作,易于工业化推广。第一凸柱2031起支撑、减少应力的作用。

s21:如图8所示,提供一芯片201,芯片201表面形成有连通介质层202,连通介质层202具有开口,连通介质层202表面形成有第一凸柱2031,开口内形成有第二凸柱2032,第二凸柱2032与芯片201电性连接,第一凸柱2031相对于连通介质层202的高度高于第二凸柱2032。

在一个实施例中,如图8所示,所述连通介质层202包括第三焊盘2023、保护层2022和重新布线层2024,保护层2022形成于芯片201表面,保护层2022具有第三窗口,第三焊盘2023形成于芯片201表面,第三窗口暴露出第三焊盘2023,重新布线层2024形成于保护层2022表面,重新布线层2024表面具有形成第二凸柱2032的开口2021,重新布线层2024包括图形化的第一介质层20241、图形化的金属层20242、图形化的第二介质层20243,芯片201与第二凸柱2032通过第三焊盘2023和重新布线层2024中的金属层20242电性连接。

在一个实施例中,连通介质层202的材质包括聚酰亚胺或高分子材料。连通介质层202能起到缓冲、绝缘的作用,还能防止芯片受损。第一凸柱2031和第二凸柱2032的材质包括铜、铝、镍、金、银、钛中的一种或几种组合。

s22:如图2~图5所示,采用上述的基板的制备方法制备基板。

s23:如图9所示,将第一凸柱2031通过第一焊料30焊接于第一焊盘1021上,将第二凸柱2032通过第二焊料30焊接于第二焊盘1022上。

在一个实施例中,焊料30的材质包括锡、铜、铝、镍、金、银、钛中的一种或几种组合。

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

以上实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

- 还没有人留言评论。精彩留言会获得点赞!