超薄桥和多管芯超细间距贴片架构及其制造方法与流程

[0001]

实施例涉及封装半导体器件。更具体而言,实施例涉及具有包括超薄桥和多管芯超细间距贴片架构的封装衬底的半导体器件。

背景技术:

[0002]

过去几十年来,集成电路(ic)中的特征的缩放已经成为不断成长的半导体工业背后的驱动力。缩放到越来越小的特征使得能够在半导体器件的有限芯片面积上实现增大密度的功能单元。然而,追求缩小ic中的特征同时优化每个器件的性能,并非没有问题。

[0003]

对于数据中心型商务而言,在封装中异质集成多个芯片/管芯是必要的。以最低功率和高带宽密度使这些芯片互连驱动着封装衬底上的超细的线/空间/过孔焊盘。近来,嵌入式桥管芯技术解决了服务器产品中的这种需要。然而,随着对多管芯互连的需求不断增大,要求封装衬底嵌入外来的桥管芯(例如,多于10个桥管芯)以容纳这些多个管芯和多管芯互连。更重要地,用于这样的封装衬底的封装组装工艺还要求用焊料将多个管芯附接到这些外来的桥管芯区域,并且期望的结果是高良品率和增大的桥管芯凸块间距。然而,这样的工艺需要另外的组装步骤和时间,并且需要在这些封装的大区域上精确地控制衬底平坦度。

[0004]

这限制了用于基于焊料的嵌入式桥管芯连接部的桥管芯凸块间距。对桥管芯凸块间距的这些限制导致了几个主要封装问题,包括小于期望的凸块密度,这进一步导致管芯中的互连物理区域增大和用于这样的增大的硅区域的成本增大。此外,现有技术还使用硅内插器尝试解决这些间距缩放限制和问题。对于多管芯架构而言,硅内插器的尺寸可能超过掩模(reticle)尺寸的两倍(或更多),因此其需要拼接掩模,但导致过高的成本和增大的复杂度。

附图说明

[0005]

本文描述的实施例以举例的方式进行说明,并且不限于附图的各个图,在附图中相似的附图标记指示类似的特征。此外,已经省略了一些常规细节,以免使本文描述的发明性概念难以理解。

[0006]

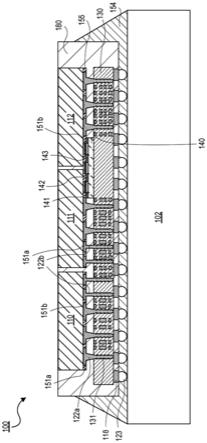

图1是根据一个实施例的半导体封装的截面视图的图示,所述半导体封装具有多个管芯、高密度封装(hdp)衬底、具有混合层的薄桥、多个第一和第二穿模过孔(through mold via,tmv)和封装衬底。

[0007]

图2a-图2l是根据一些实施例的形成半导体封装的工艺流程的截面视图的图示,所述半导体封装具有多个管芯、hdp衬底、具有混合层的薄桥、多个第一和第二tmv和封装衬底。

[0008]

图3是根据一个实施例的半导体封装的截面视图的图示,所述半导体封装具有多个管芯、多个hdp衬底、具有混合层的多个薄桥、多个第一和第二tmv和封装衬底。

[0009]

图4是示出了根据一个实施例的利用半导体封装的计算机系统的示意性框图的图

示,所述半导体封装具有多个管芯、hdp衬底、具有混合层的薄桥、多个第一和第二tmv和封装衬底。

具体实施方式

[0010]

本文描述的是一种具有封装衬底和超薄(或薄)桥和多管芯超细间距贴片架构的半导体封装以及一种形成这样的半导体封装的方法。根据一些实施例,下文描述的半导体封装和形成这样的半导体封装的方法可以包括多个管芯、高密度封装(hdp)衬底、薄桥、多个第一穿模过孔(tmv)、多个第二tmv和封装衬底。本文描述的半导体封装的这些实施例无需焊料球/连接部而组合hdp衬底(例如,高密度(hd)有机衬底)和薄桥(例如,薄嵌入式多管芯互连桥(emib)),并且使桥的数量最小化,并且使得能够用混合电介质/导电接合层(例如,二氧化硅/铜(sio2/cu)接合层)在hdp衬底和管芯之间直接耦合(或附接)薄桥。

[0011]

如本文使用的,“桥”可以指硅互连桥或由适于形成这样的互连桥(例如,嵌入式多管芯互连桥(emib))的任何其他衬底材料制成的互连桥。因此,如本文使用的,“薄桥”(或“超薄桥”)可以指可以具有大约10μm-15μm的厚度和/或大约或小于10μm的厚度的桥。如上所述,本文描述的薄桥不需要焊料球来耦合到管芯,相反,这样的薄桥可以用混合层(或混合接合层)直接耦合(和/或通信耦合)到管芯。如本文使用的,“混合层”(或混合接合层)可以指由多个导电焊盘(或cu焊盘)、电介质层(或sio2层)和表面抛光层(或锡(sn)层)构成的薄层(或超薄层),其中电介质层可以围绕导电焊盘,其中导电焊盘的顶表面与用于使导电焊盘绝缘的电介质层的顶表面基本共面,并且其中表面抛光层可以直接设置(或涂覆)在导电焊盘的顶表面上。

[0012]

例如,为了用混合层将无焊料的薄桥直接耦合到管芯,薄桥可以将sn直接设置在该薄桥的薄cu焊盘上,其中超薄桥的sn直接与管芯的cu焊盘反应,(i)以在薄桥和管芯之间实施sn/cu金属间化合物,并且(ii)用混合接合工艺等将薄桥直接锁定(或在适当位置接合)到管芯。根据实施例,混合接合工艺可以包括温度加热、压力和还原性气氛以在超薄桥和管芯之间实施锁定。需注意,如下所述,如果期望,混合层可以省略表面抛光层。

[0013]

本文描述的组合的hdp衬底和薄桥通过充分地减少(或消除/减轻)如上文结合现有技术所述的典型需要的薄桥的总数而有助于半导体封装。下文描述的半导体封装的实施例使得能够改进通往诸如管芯的输入/输出(i/o)电路的布线和电力输送功能。本文描述的实施例还为半导体封装提供了改进的翘曲益处。例如,该半导体封装可以在临时玻璃载体上实施,这显著减小了热膨胀系数(cte)失配应力,尤其是在包封层(或模制层)处理步骤之后。

[0014]

本文描述的实施例通过消除基于焊料的桥互连(即,本文描述的桥(或emib)可以无需焊料连接部而与另一个部件耦合),由此提供改进的桥间距缩放、管芯上减小的互连物理区域、和降低的组装成本,从而提供了对现有封装方案的改进。而且,对现有封装方案的另一改进包括消除了对昂贵的硅内插器的需要,由此降低了总体封装成本。这些半导体封装还通过实施并且组合无焊料桥(或emib)互连、桥到玻璃贴片混合接合(例如,sio2/cu接合)、具有充分减小的线/间隔(l/s)(例如,小于2/2的l/s)、超细光刻限定(光刻)过孔、和零非对准过孔架构的hdp衬底布线层,从而提供了对封装方案的改进。

[0015]

可以在一种或多种电子装置中实施本文描述的技术。可以利用本文描述的技术的

电子装置的非限制性示例包括任何种类的移动装置和/或固定装置,例如基于微机电系统(mems)的电子系统、陀螺仪、高级驾驶辅助系统(adas)、5g通信系统、相机、蜂窝电话、计算机终端、台式计算机、电子阅读器、传真机、信息亭、上网本计算机、笔记本计算机、上网装置、支付终端、个人数字助理、媒体播放器和/或录音器、服务器(例如,刀片式服务器、机架安装式服务器、其组合等)、机顶盒、智能电话、平板个人计算机、超移动个人计算机、有线电话、其组合等。这样的装置可以是便携的或固定的。在一些实施例中,可以在台式计算机、膝上型计算机、智能电话、平板计算机、上网本计算机、笔记本计算机、个人数字助理、服务器、其组合等中采用本文描述的技术。更一般地,可以在包括具有封装衬底、管芯、hdp衬底、具有混合层的薄桥(或薄emib)、和具有不同宽度的tmv的半导体封装的各种各样的电子装置中的任一种中采用本文描述的技术。

[0016]

在以下描述中,将采用本领域技术人员通常采用的术语来描述说明性实施方式的各方面,以向本领域其他技术人员传达其工作的实质。然而,对本领域技术人员而言显而易见的是,可以仅用所述方面中的一些来实践本实施例。出于解释的目的,阐述了具体的数量、材料和构造,以便提供对说明性实施方式的透彻理解。然而,对本领域技术人员将显而易见的是,可以在没有具体细节的情况下实践本实施例。在其他实例中,省略或简化了公知的特征,以免使说明性实施方式难以理解。

[0017]

将以对理解本实施例最有帮助的方式按次序将各种操作描述为多个分立的操作,然而,不应当将描述的次序解释为暗示这些操作必然取决于次序。具体而言,不需要按照所表达的次序执行这些操作。

[0018]

如本文使用的,术语“顶部”、“底部”、“上部”、“下部”、“最下部”和“最上部”在相对于一个或多个元件使用时,意在传达相对而非绝对的物理构造。因而,被描述为装置中的“最上部元件”或“顶部元件”的元件在翻转装置时可以转而形成装置中的“最下部元件”或“底部元件”。类似地,被描述为装置中的“最下部元件”或“底部元件”的元件在翻转装置时可以转而形成装置中的“最上部元件”或“顶部元件”。

[0019]

现在参考图1,示出了根据实施例的半导体封装100的截面图示。在实施例中,半导体封装100可以包括多个管芯110-112、hdp衬底130、具有混合层141-143的薄桥140、多个tmv 122a-b和封装衬底102。对于一个实施例而言,半导体封装100可以组合(或堆叠)管芯110-112、薄桥140和hdp衬底130,其中薄桥140可以用混合层141-143直接耦合(或附接)在hdp衬底130和管芯110-112之间,并且其中混合层141-143由多个导电焊盘141(或cu焊盘)、电介质层142(sio2层)和表面抛光层143(sn层或裸露cu表面层)(即,混合电介质/导电接合层)构成。

[0020]

换言之,根据一些实施例,管芯110-112可以设置在hdp衬底130和薄桥140上方,并且薄桥140可以直接设置在管芯110-112下方并且在管芯110-112之间,而hdp衬底130可以设置在封装衬底102上方。需注意,尽管图1中示出了一个hdp衬底130、一个薄桥140和三个管芯110-112,但要认识到任何数量的hdp衬底130、薄桥140和管芯110-112都可以与封装衬底102组合/堆叠、设置在封装衬底102上/上方,并且耦合到封装衬底102。

[0021]

对于一个实施例而言,封装衬底102可以包括但不限于封装、衬底、印刷电路板(pcb)和/或主板。对于一个实施例而言,封装衬底102是pcb。对于一个实施例而言,pcb由在两侧上都层合了薄铜箔的fr-4玻璃环氧树脂基底制成。对于特定实施例而言,可以使用多

层pcb,其中使用预浸材料(pre-preg)和铜箔制造另外的层。例如,多层pcb可以包括一个或多个电介质层,其中每个电介质层可以是光敏电介质层。对于一个实施例而言,pcb 102可以包括多个导电层,pcb 102还可以包括铜(或金属)迹线、线、焊盘、过孔、过孔焊盘、孔和/或平面。

[0022]

如图1所示,hdp衬底130可以设置在封装衬底102上方,其中hdp衬底130可以用多个焊料球123导电耦合到封装衬底102。在一些实施例中,hdp衬底130可以包括由具有大约或小于2/2μm的l/s的迹线、光刻过孔、零非对准过孔、和/或具有大约或小于18μm的厚度的过孔焊盘构成的多个再分布层(rdl)。hdp衬底130可以是用于与管芯110-112和/或薄桥140通信的具有增大(或高)的输入/输出(i/o)密度和带宽的硅衬底。在一个实施例中,hdp衬底130可以具有大约10μm到200μm的厚度。

[0023]

在一个实施例中,hdp衬底130可以具有多个第一导电焊盘118和多个导电互连131。第一导电焊盘118可以设置在hdp衬底130的底表面上。在一个实施例中,第一导电焊盘118可以具有大于大约80μm的间距。第一导电焊盘118可以是多个球栅阵列(bga)焊盘等。hdp衬底130的导电互连131可以包括过孔、迹线、线、焊盘等。例如,导电互连131可以直接耦合到第一导电焊盘118,其中焊料球123可以将hdp衬底130的第一导电焊盘118导电耦合到封装衬底102的顶表面。

[0024]

导电互连131可以从hdp衬底130的底表面垂直延伸到顶表面。例如,hdp衬底130的导电互连131的底表面可以直接耦合到第一导电焊盘118,其中导电互连131的底表面可以与hdp衬底130的底表面基本共面。与此同时,在另一个示例中,hdp衬底130的导电互连131的顶表面可以直接耦合到多个tmv 122a-b,其中导电互连131的顶表面可以与hdp衬底130的顶表面基本共面。

[0025]

对于一个实施例而言,薄桥140可以直接设置在hdp衬底130上方/上,其中薄桥140的底表面可以直接耦合到hdp衬底130的顶表面。在一个实施例中,薄桥140可以包括由导电焊盘141、电介质层142和表面抛光层143构成的混合层141-143。在一个实施例中,导电焊盘141可以是多个cu焊盘等。对于一个实施例而言,电介质层142可以是由sio2材料和/或使导电焊盘141绝缘的任何已知的电介质/绝缘材料等形成的钝化层。此外,如上所述,在一个实施例中,表面抛光层143可以包括可以提供额外焊料(例如,锡等)的一种或多种导电材料。例如,导电焊盘141和电介质层142可以直接设置在薄桥140的顶表面上,其中电介质层142围绕导电焊盘141。此外,导电焊盘141的顶表面可以与电介质层142的顶表面基本共面,其中表面抛光层143可以直接设置在导电焊盘141的顶表面上。

[0026]

对于一个实施例而言,薄桥140可以具有大约10μm到15μm的厚度。在另一个实施例中,薄桥140可以具有大约或小于10μm的厚度。对于一个实施例而言,桥140的导电焊盘141和电介质层142可以具有大约5μm的厚度。在另一个实施例中,桥140的导电焊盘141和电介质层142可以具有大约或小于10μm的厚度。对于一个实施例而言,桥140的表面抛光层143可以具有大约1μm到2μm的厚度。在另一个实施例中,桥140的表面抛光层143可以具有大约或小于5μm的厚度。需注意,在一些替代实施例中,可以省略表面抛光层143,如图2c所示。照此,在一个实施例中,混合层141-143可以具有大约5μm到7μm的厚度;而在另一个实施例中,混合层141-143可以具有大约或小于7μm的厚度。

[0027]

另外,如图1所示,tmv 122a-b可以直接设置在hdp衬底130的导电互连131的顶表

面上/上方并且耦合到hdp衬底130的导电互连131的顶表面。例如,tmv 122a-b可以从hdp衬底130的导电互连131的顶表面垂直延伸到管芯110-112的大致底表面(或管芯110-112的多个第二导电焊盘151a-b的底表面)。需注意,在一些实施例中,tmv 122a-b在hdp衬底130的导电互连131上可以不是直接(或完美)对准的。

[0028]

在一个实施例中,tmv 122a-b可以由诸如cu等的导电材料形成。tmv 122a-b可以用光刻工艺(等)形成,因为tmv 122a-b可以被无电地生长、用模料包封、并且随后被平面化。另外,tmv 122a-b可以具有多个第一tmv 122a和多个第二tmv 122b。在一个实施例中,第一tmv 122a的宽度可以比第二tmv 122b的宽度更大。此外,在一些实施例中,第一tmv 122a可以具有渐缩的侧壁,而第二tmv 122b可以具有基本垂直的侧壁和/或可以具有轻微渐缩的侧壁的角度,该角度显著小于第一tmv 122a的渐缩的侧壁的角度。

[0029]

对于一些实施例而言,tmv 122a-b可以围绕薄桥140。在实施例中,薄桥140可以通信耦合第一管芯110、第二管芯111、第三管芯112和/或hdp衬底130。如图1所示,薄桥140可以直接耦合到管芯111-112。然而,需注意,薄桥140可以耦合到两个或更多管芯110-112中的任一个。在实施例中,薄桥140可以包括电布线(或互连结构(例如,穿硅过孔(tsv)),以用导电焊盘141和/或表面抛光层143将第二管芯111通信耦合到第三管芯112。如上所述,薄桥140不需要焊料球来直接耦合到管芯111-112,相反,薄桥140可以用由导电焊盘141、电介质层142和表面抛光层143构成的混合层直接耦合到管芯111-112。在一些实施例中,薄桥140可以被称为emib。对于另外的实施例而言,薄桥140可以包括多个tsv,多个tsv可以进一步用于将薄桥140耦合到管芯111-112和/或hdp衬底130。

[0030]

如图1所示,管芯110-112可以包括第一管芯110、第二管芯111和第三管芯112。第一、第二和第三管芯110-112可以设置在hdp衬底130上方。第二和第三管芯111-112可以设置在hdp衬底130和薄桥140两者上方。在一些实施例中,管芯110-112可以包括第二导电焊盘151a-b和电介质层155。第二导电焊盘151a-b和电介质层155两者都可以直接设置在管芯110-112的底表面上,其中电介质层155可以围绕第二导电焊盘151a-b。

[0031]

在一个实施例中,第二导电焊盘151a-b可以是多个cu焊盘等。对于一个实施例而言,电介质层155可以是由sio2材料和/或使第二导电焊盘151a-b绝缘的任何已知的电介质/绝缘材料等形成的钝化层。对于一个实施例而言,管芯110-112可以具有大约或大于200μm的厚度。在另一个实施例中,管芯110-112可以具有大约或小于200μm的厚度。对于一个实施例而言,管芯110-112的导电焊盘151a-b和电介质层155可以具有大约2μm的厚度。在另一个实施例中,管芯110-112的导电焊盘151a-b和电介质层155可以具有大约或小于5μm的厚度。

[0032]

在一个实施例中,第二导电焊盘151a-b可以包括多个第二导电焊盘151a和多个第二导电焊盘151b。在这些实施例中,第二导电焊盘151a的宽度可以比第二导电焊盘151b的宽度更大。例如,第一tmv 122a可以将管芯110-112的第二导电焊盘151a导电耦合到hdp衬底130的导电互连131。同样,第二tmv 122b可以将第一和第二管芯110-111的第二导电焊盘151b导电耦合到hdp衬底130的导电互连131,而第二和第三管芯111-112的第二导电焊盘151b可以直接耦合到薄桥140的表面抛光层143和导电焊盘141上。

[0033]

对于一个实施例而言,管芯110-112可以包括但不限于半导体管芯、电子器件(例如,无线器件)、集成电路(ic)、中央处理单元(cpu)、微处理器、平台控制器集线器(pch)、存

储器(例如,高带宽存储器(hbm))、和/或现场可编程门阵列(fpga)。管芯110-112可以由诸如硅的材料形成,并且在其上具有要耦合到hdp衬底130和薄桥140的电路。

[0034]

对于一个实施例而言,包封层180可以设置在具有第二导电焊盘151a-b和电介质层155的管芯110-112、tmv 122a-b、具有导电焊盘141、电介质层142、以及表面抛光层143的薄桥140、以及具有第一导电焊盘118的hdp衬底130上方。照此,tmv 122a-b可以被包封层180围绕,并且可以垂直延伸穿过包封层180,以将hdp衬底130导电耦合到管芯110-111。在一个实施例中,包封层180可以包括一种或多种包封材料,例如模制材料、底填材料、填充材料、(一种或多种)任何类似的材料、和/或其任意组合。对于一个实施例而言,包封层180可以被平面化,因为包封层180的顶表面可以与管芯110-112的顶表面基本共面,其中包封层180也可以设置在管芯110-112之间。

[0035]

而且,包封层180可以设置在底填材料154(或底填层)上方。在一个实施例中,底填材料154可以设置在封装衬底102上方,其中底填材料154设置在封装衬底102的顶表面和包封层180以及第一导电焊盘118的底表面之间。底填材料154可以围绕(或嵌入)包封层180的部分和设置在包封层180和封装衬底102之间的焊料球123。

[0036]

在另外的实施例中,热方案(或热器件)可以设置在管芯110-112和/或包封层180的顶表面上方,其中热方案可以包括热沉、集成散热器(ihs)、歧管、冷板等。

[0037]

需注意,基于期望的封装设计,半导体封装100可以包括更少的或另外的封装部件。

[0038]

图2a-图2l是根据实施例的形成半导体封装200的工艺流程的截面视图的图示。在实施例中,根据一些实施例,半导体封装200可以包括多个管芯210-212、hdp衬底230、具有混合层241-243的薄桥240、多个tmv 222a-b和封装衬底202。图2a-图2l中所示的工艺流程形成基本类似于上文在图1中所述的半导体封装100的半导体封装200。同样,半导体封装200的部件基本类似于上文在图1中所述的半导体封装100的部件。因此,如上所述,封装衬底200的工艺流程示出了用于组合管芯210-212、薄桥240和hdp衬底230的方式之一,因为薄桥240可以用混合层241-243、使用tmv 222a-b和导电焊盘255a-b以超细互连/布线间距直接耦合在hdp衬底230和管芯210-212之间,而无需焊料连接部。

[0039]

现在参考图2a,示出了根据实施例的半导体封装200的截面图示。在实施例中,半导体封装200可以包括设置在载体201上的粘合剂层261(或粘合剂膜、接合膜等)。对于一个实施例而言,载体201可以是玻璃载体(或临时玻璃面板载体)、金属载体和/或任何类似的平坦和刚性载体/衬底。

[0040]

另外,在一个实施例中,多个管芯210-212可以设置在粘合剂层261和载体201上方,其中管芯210-212可以彼此相邻地定位并且用粘合剂层261耦合到载体201。例如,管芯210-212可以彼此相邻地设置,其中管芯到管芯间隔大约或小于50μm。此外,如图2a所示,管芯210-212的顶表面可以直接设置在粘合剂层261上以将管芯210-212耦合到载体201。管芯210-212可以基本类似于上文在图1中所述的管芯110-112。照此,管芯210-212可以具有多个第二导电焊盘251a-b和电介质层255,其中第二导电焊盘251a的宽度可以大于第二导电焊盘251b的宽度。

[0041]

此外,如图2a所示,第二导电焊盘251a-b的顶表面可以在电介质层255的顶表面上方突出。例如,第二导电焊盘251a-b可以被过度镀覆有在电介质层厚度上面大约2μm到3μm

的厚度。另外,在一个实施例中,第二导电焊盘251b可以具有大约或小于5μm的间距,所述间距可以被实施用于桥界面和hd互连(例如,图2e的tmv 222b)。而在另一个实施例中,第二导电焊盘251a可以具有大约或大于25μm的间距,所述间距可以被实施用于非桥界面。这些过度镀覆的第二导电焊盘251a-b有助于减轻管芯210-212之间的厚度变化,其中还可以调节(或选择)电介质层255的厚度以适应管芯210-212之间的这种厚度变化。

[0042]

现在参考图2b,示出了根据实施例的半导体封装200的截面图示。在实施例中,可以对过度镀覆的第二导电焊盘251a-b进行平面化,使得第二导电焊盘251a-b的顶表面与电介质层255的顶表面基本共面。这一平面化工艺还使得第二导电焊盘251a-b能够具有彼此基本相同的厚度,由此减小了半导体封装200的任何厚度变化。

[0043]

在实施例中,可以用化学机械平面化(cmp)工艺等实施平面化。由于存在充当停止点的电介质层255,平面化工艺可以具有高度的精确度。在对第二导电焊盘251a-b进行平面化之后,第二导电焊盘251a-b的暴露的顶表面可以与电介质层255的顶表面基本共面,但第二导电焊盘251a-b的暴露的顶表面具有轻微的凹陷。例如,可以选择性刻蚀第二导电焊盘251a-b以创建在电介质层255的顶表面下方大约或小于0.5μm的轻微凹陷(或欠刻蚀),其中这种轻微凹陷有助于桥(例如,图2d的桥240)与第二和第三管芯211-212保持被锁定在适当位置,如上所述且如下方图2d所示。

[0044]

现在参考图2c,示出了根据实施例的半导体封装200的截面图示。在实施例中,多个薄桥240可以直接设置在第二和第三管芯211-212上(如下方图2d中所示)。薄桥240可以基本类似于上文在图1中所述的薄桥140。因此,在一个实施例中,薄桥240可以包括混合层241-243(如图2c的右侧的薄桥240所示),其中混合层241-243由多个导电焊盘241、电介质层242和表面抛光层243构成(例如,混合层241-243可以包括cu/sio2/sn的组合等)。在一个实施例中,可以用快速切削(fly-out)工艺等在薄桥240上方对导电焊盘241和电介质层242进行平面化。随后,在这些实施例中,然后可以用sn涂覆工艺等(例如,利用浸渍sn镀覆、电镀等实施sn涂覆工艺)将表面抛光层243直接设置在导电焊盘241的暴露的顶表面上方。而且需指出,如图2c所示,表面抛光层243可以在电介质层242的顶表面上方突出。

[0045]

在替代实施例中,薄桥240可以包括混合层241

’-

242’(如图2c的左侧的薄桥240所示),其中混合层241

’-

242’由多个导电焊盘241’和电介质层242’构成。在省略表面抛光层243之后,混合层241

’-

242’可以基本类似于混合层241-243。

[0046]

现在参考图2d,示出了根据实施例的半导体封装200的截面图示。对于一个实施例而言,具有混合层241-243的薄桥240可以设置在第二和第三管芯211-212上方。在实施例中,可以用面向下的混合层241-243将薄桥240精确地定位到第二和第三管芯211-212的第二导电焊盘251b上(即,定位到(具有轻微凹陷的)精细间距导电(或cu)焊盘上)。在这些实施例中,薄桥240的表面抛光层243和导电焊盘241可以是多个sn涂覆的cu焊盘。对于一个实施例而言,可以用精确的拾放工具(等)将薄桥240的sn涂覆的cu焊盘精确地放置在第二和第三管芯211-212的第二导电焊盘251b上。此外,如上所述,可以在sn涂覆的cu焊盘在大约240℃

–

250℃下被加热以在薄桥240的导电焊盘241与第二和第三管芯211-212的相应的第二导电焊盘251b之间创建cu-sn-cu金属间接合部时,在薄桥240的sn涂覆的cu焊盘上实施混合接合工艺(或cu/sio

2-cu/sio2混合接合工艺)。因此,在这些实施例中,cu-sn-cu金属间接合部可以将薄桥240锁定(或在适当位置牢固地保持)到第二和第三管芯211-212上。

[0047]

现在参考图2e,示出了根据实施例的半导体封装200的截面图示。在实施例中,可以实施光刻图案化和镀覆工艺(等)以将多个tmv 222a-b直接设置(或镀覆/形成)在管芯210-212的相应的第二导电焊盘251a-b上。光刻工艺可以包括如下所述的几个步骤。例如,可以将种子层设置在管芯210-212的电介质层255和第二导电焊盘251a-b的暴露的顶表面上方。在一个实施例中,种子层可以包括铜、钛、其任意组合等。可以用溅镀工艺等形成种子层。

[0048]

在设置种子层之后,在一个实施例中,可以在种子层上方设置抗蚀剂层。在实施例中,抗蚀剂层可以是干膜抗蚀剂(dfr)等。在实施例中,可以用光刻工艺、激光钻孔工艺等对抗蚀剂层进行图案化(或曝光/显影)以形成过孔开口。所述过孔开口可以暴露非桥界面(或部分/区域)中的管芯210-212的第二导电焊盘251a-b的顶表面。

[0049]

在一些实施例中,可以将导电材料(例如,cu)设置(或镀覆)到过孔开口中,以在管芯210-212的第二导电焊盘251a-b的暴露的顶表面上分别形成tmv 222a-b(或光刻过孔,该过孔可以被无电地生长,随后用模料包封并且被平面化)。tmv 222a-b可以称为导电柱/互连。tmv 222a-b可以基本类似于上文在图1中所述的tmv 122a-b。在实施例中,可以在抗蚀剂层的顶表面上方过度镀覆tmv 222,以便确保完全填充抗蚀剂层中的过孔开口。对于一个实施例而言,tmv 222a-b可以从第二导电焊盘251a-b垂直延伸到抗蚀剂层的顶表面/到抗蚀剂层的顶表面上方。在实施例中,可以用电镀工艺等形成tmv 222a-b。

[0050]

在实施例中,在tmv 222a-b被过度镀覆时,可以对过度镀覆的tmv 222a-b进行平面化,使得tmv 222a-b的顶表面与抗蚀剂层的顶表面基本共面。这一平面化工艺还使得tmv 222a-b能够具有彼此基本相同的厚度,由此减小了半导体封装200的任何厚度变化。例如,在对tmv 222a-b进行平面化之后,tmv 222a-b的暴露的表面可以与桥240的暴露的表面基本共面。在实施例中,可以用cmp工艺等实施平面化。由于存在充当停止点的抗蚀剂层,平面化工艺可以具有高度的精确度。最后,可以用诸如灰化、湿法剥离等的任何适当的工艺来剥离抗蚀剂层。在去除抗蚀剂层之后,可以暴露种子层的部分。照此,可以用刻蚀工艺等刻蚀暴露的种子层。

[0051]

现在参考图2f,示出了根据实施例的半导体封装200的截面图示。对于一个实施例而言,包封层280可以设置在tmv 222a-b、具有电介质层242的薄桥240、具有导电焊盘251a-b和电介质层255的管芯210-212、以及粘合剂层261上方。在实施例中,可以设置包封层280以覆盖tmv 222a-b的顶表面。在一个实施例中,包封层280可以是模制层和/或(一种或多种)任何类似的包封材料。对于一个实施例而言,模制层280可以包括具有一种或多种填充材料的环氧树脂(例如,软环氧树脂、刚性环氧树脂、不透明环氧树脂等)。在实施例中,包封层280可以是挤压模制的、层合的等。

[0052]

包封层280可以基本类似于上文在图1中所述的包封层180。在实施例中,包封层280可以被平面化(或研磨),使得tmv 222a-b的顶表面与包封层280和/或桥240的顶表面基本共面。另外,包封层280被平面化/研磨以暴露tmv 222a-b和/或桥240的顶表面。在实施例中,可以用cmp工艺等实施平面化。

[0053]

现在参考图2g,示出了根据实施例的半导体封装200的截面图示。在实施例中,hdp衬底230可以设置在包封层280、tmv 222a-b和桥240的顶表面上方。照此,hdp衬底230的桥界面可以直接设置在桥240的暴露的表面上,由此具有混合层241-243的桥240被夹置在管

芯211-212和hdp衬底230之间。hdp衬底230可以基本类似于上文在图1中所述的hdp衬底130。照此,hdp衬底230可以包括多个导电互连231和多个第一导电焊盘218。hdp衬底230的导电互连231可以将tmv 222a-b和管芯210-212导电耦合到第一导电焊盘218。

[0054]

在一个实施例中,如上所述,可以用光刻工艺将第一导电焊盘218设置(或镀覆)在hdp衬底230的顶表面上。需注意,在如图2l所示的翻转半导体封装200之后,第一导电焊盘218最终被定位在hdp衬底230下方,耦合到hdp衬底230的底表面,并且类似于上文在图1中所述的第一导电焊盘118。对于一个实施例而言,hdp衬底230可以包括一个或多个rdl层,一个或多个rdl层具有大约或小于2/2的l/s的导电迹线(或线)、光刻过孔、零非对准过孔、和/或大约或小于18μm的过孔焊盘。在一个实施例中,hdp衬底230的第一导电焊盘218可以具有大约或大于80μm的间距。

[0055]

现在参考图2h,示出了根据实施例的半导体封装200的截面图示。在实施例中,包封层280可以进一步设置在第一导电焊盘218、hdp衬底230和现有的包封层280上方,以完全围绕(或包围/嵌入)hdp衬底230、桥240和管芯210-212。包封层280可以基本类似于上文在图2f中所述的包封层280。另外,在一个实施例中,可以对包封层280进行平面化以暴露第一导电焊盘218的顶表面,其中第一导电焊盘218的顶表面与包封层280的顶表面基本共面。如上所述,可以用cmp工艺等对包封层280进行平面化。

[0056]

现在参考图2i,示出了根据实施例的半导体封装200的截面图示。在一个可选的实施例中,可以将多个焊料球223直接设置到第一导电焊盘218的暴露的表面上并且耦合到第一导电焊盘218的暴露的表面。焊料球223可以基本类似于上文在图1中所述的焊料球123。

[0057]

现在参考图2j,示出了根据实施例的半导体封装200的截面图示。在实施例中,可以从管芯210-212和包封层280下方去除载体201和粘合剂层261,以暴露管芯210-212的(顶)表面。在去除粘合剂层261以及载体201之后,管芯210-212的(顶)表面可以与包封层280的(顶)表面基本共面。

[0058]

现在参考图2k,示出了根据实施例的半导体封装200的截面图示。在实施例中,半导体封装200可以将多个贴片(封装)进行单个化(singulate),以形成基本类似于上文在图1中所述的半导体封装100的个体的贴片(或封装)。可以通过将多个贴片切片、锯切、激光处理(等)成如图2k中所示的封装所示出的一个贴片,来实施半导体封装200的贴片的单个化。

[0059]

现在参考图2l,示出了根据实施例的半导体封装200的截面图示。在实施例中,hdp衬底230的第一导电焊盘218可以设置并且耦合到封装衬底202的顶表面上。封装衬底202可以基本类似于上文在图1中所述的封装衬底102。另外,如上所述,底填材料254可以设置在包封层280和封装衬底202上方,其中底填材料254可以设置在hdp衬底230和封装衬底202之间。底填材料254可以围绕包封层280的部分和第一焊料球223。底填材料254可以基本类似于上文在图1中所述的底填材料154。

[0060]

需注意,基于期望的封装设计,图2a-图2l的半导体封装200可以包括更少的或另外的封装部件。

[0061]

现在参考图3,示出了根据实施例的半导体封装300的截面图示。半导体封装300可以基本类似于图1和图2a-图2l的半导体封装100和200,区别在于两组管芯310-312分别设置在两个hdp衬底330和两个薄桥340上方并且分别耦合到两个hdp衬底330和两个薄桥340,并且薄桥340中的一个或多个可以包括多个tsv(如果需要的话),由此,如果需要tsv,则可

以将薄桥340的tsv直接耦合(或焊接)到hdp衬底330,以直接向诸如管芯310-312的i/o电路和/或衬底301供电。

[0062]

尽管在图1中一组管芯110-112设置在一个hdp衬底130和一个薄桥140上方并且耦合到一个hdp衬底130和一个薄桥140,但在图3中两组管芯310-312以超细间距设置在相应的hdp衬底330和薄桥340上方并且通信耦合到相应的hdp衬底330和薄桥340,由此添加了另外的期望ic(例如,另外的管芯),从而改进了半导体封装300的总体性能,同时仅使用一个具有超薄混合层341-343的薄桥340,从而为半导体封装300保持充分减小的总厚度(或z高度)。

[0063]

而且,尽管在图1中薄桥140具有不带有任何tsv的混合层141-143,但在图3中薄桥340可以实施具有tsv的混合层341-343,由此直接向相应的管芯310-312和/或衬底301供电,以改进半导体封装300的总体功率性能。尽管在每个贴片中,示出了三个管芯310-312、一个hdp衬底330和一个薄桥340,但要认识到,在每个贴片中,可以在衬底301上/上方设置(或定位)任意数量的管芯310-312、hdp衬底330和薄桥340。需注意,可以将半导体封装300从两个贴片(或封装)单个化成个体贴片(或封装),如上文在图2k-图2l中所示/所述。

[0064]

在一个实施例中,衬底301可以是封装衬底、载体、内插器等。需注意,如上所述,半导体封装300可以基本类似于上文在图1中所述的半导体封装100。同样,上述的半导体封装300的部件基本类似于上文在图1中所述的半导体封装100的部件。另外,衬底301、管芯310-312、tmv 322a-b、焊料球323、hdp衬底330、导电互连331、薄桥340、混合层341-343、第一和第二导电焊盘318和351a-b、电介质层355和包封层380可以基本类似于上文在图1中所述的封装衬底101、管芯110-112、tmv 122a-b、焊料球123、hdp衬底130、导电互连131、薄桥140、混合层141-143、第一和第二导电焊盘118和151a-b、电介质层155和包封层180。

[0065]

需注意,基于期望的封装设计,半导体封装300可以包括更少的或另外的封装部件。

[0066]

图4是示出了根据一个实施例的利用器件封装410(或半导体封装)的计算机系统400的示意性框图的图示,器件封装410(或半导体封装)具有多个管芯、hdp衬底、具有混合层的薄桥、多个tmv和封装衬底。图4示出了计算装置400的示例。计算装置400容纳主板402。主板402可以包括若干部件,包括但不限于处理器404、器件封装410(或半导体封装)和至少一个通信芯片406。处理器404物理和电耦合到主板402。对于一些实施例而言,至少一个通信芯片406也物理和电耦合到主板402。对于其他实施例而言,至少一个通信芯片406是处理器404的部分。

[0067]

取决于其应用,计算装置400可以包括可以或可以不物理和电耦合到主板402的其他部件。这些其他部件包括但不限于易失性存储器(例如,dram)、非易失性存储器(例如,rom)、闪速存储器、图形处理器、数字信号处理器、加密处理器、芯片组、天线、显示器、触摸屏显示器、触摸屏控制器、电池、音频编解码器、视频编解码器、功率放大器、全球定位系统(gps)装置、罗盘、加速度计、陀螺仪、扬声器、相机和大容量存储装置(例如,硬盘驱动器、紧凑盘(cd)、数字多用盘(dvd)等)。

[0068]

至少一个通信芯片406能够实现用于将数据传输到计算装置400和从计算装置400传输数据的无线通信。术语“无线”及其派生词可以用于描述可以通过使用调制的电磁辐射通过非固体介质来传送数据的电路、装置、系统、方法、技术、通信信道等。该术语并不暗示

相关联的装置不包含任何线路,尽管在一些实施例中它们可以不包含任何线路。至少一个通信芯片406可以实施若干无线标准或协议中的任何标准或协议,包括但不限于wi-fi(ieee 802.11系列)、wimax(ieee 802.112系列)、ieee 802.20、长期演进(lte)、ev-do、hspa+、hsdpa+、hsupa+、edge、gsm、gprs、cdma、tdma、dect、蓝牙、其衍生物,以及被指定为3g、4g、5g和更高版本的任何其他无线协议。计算装置400可以包括多个通信芯片406。例如,第一通信芯片406可以专用于诸如wi-fi和蓝牙的短程无线通信,并且第二通信芯片406可以专用于诸如gps、edge、gprs、cdma、wimax、lte、ev-do或其他的长程无线通信。

[0069]

计算装置400的处理器404包括封装在处理器404内的集成电路管芯。器件封装410可以是可以包括但不限于衬底、封装衬底和/或pcb的半导体封装。在一个实施例中,器件封装410可以基本类似于本文描述的图1-图3的半导体封装。器件封装410可以包括本文描述的管芯、hdp衬底、具有混合层的薄桥、具有变化宽度的互连(例如,图1的导电焊盘151a-b和tmv122a-b)、以及封装衬底(例如,如上文结合图1-图3的半导体封装所示和所述的)、或者来自本文描述的附图的任何其他部件。

[0070]

需注意,器件封装410可以是单个部件/器件、部件的子集、和/或整个系统,因为材料、特征和部件可能限于如本文所述的可能需要以超细间距和超薄混合层锁定/耦合/设置在管芯和hdp衬底之间的无焊料超薄桥的器件封装410和/或计算装置400的任何其他部件(例如,主板402、处理器404和/或可能需要本文描述的半导体封装的实施例的计算装置400的任何其他部件)。

[0071]

对于一些实施例而言,可以将集成电路管芯与封装衬底上的一个或多个器件封装在一起,所述一个或多个器件包括用于无线通信的热稳定的rfic和天线以及如本文描述的器件封装,以减小计算装置的z高度。术语“处理器”可以指处理来自寄存器和/或存储器的电子数据以将该电子数据变换成可以存储在寄存器和/或存储器中的其他电子数据的任何装置或装置的部分。

[0072]

至少一个通信芯片406也包括封装在通信芯片406内的集成电路管芯。对于一些实施例而言,通信芯片406的集成电路管芯可以与一个或多个器件一起被封装在包括如本文所述的一个或多个器件封装的封装衬底上。

[0073]

在以上说明书中,已经参考其具体示例性实施例描述了各实施例。然而,应当记住,所有的这些以及类似的术语都与适当的物理量相关联,并且只是应用于这些量的方便标签。显而易见的是,在不脱离更广泛的实质和范围的情况下,可对其进行各种修改。因此,说明书和附图应当被认为是出于说明性目的而非限制性目的。

[0074]

以下示例涉及其他实施例。不同实施例的各种特征可以通过各种方式与一些包括的特征和排除的其他特征组合以适应各种不同应用。

[0075]

以下示例涉及其他实施例:

[0076]

示例1是一种半导体封装,包括:hdp衬底上的桥,其中桥包括混合层;桥和hdp衬底上方的多个管芯,其中桥耦合在多个管芯和hdp衬底之间,其中桥用混合层直接耦合到多个管芯中的两个管芯,其中桥的混合层的顶表面直接在多个管芯的底表面上,并且其中桥的底表面直接在hdp衬底的顶表面上;以及hdp衬底上的多个tmv,其中多个tmv将hdp衬底耦合到多个管芯,并且其中多个tmv的厚度基本等于桥的厚度。

[0077]

在示例2中,示例1的主题可以任选地包括:桥的混合层包括多个导电焊盘和电介

质,并且其中电介质围绕多个导电焊盘。

[0078]

在示例3中,示例1-2的主题可以任选地包括:桥的混合层还包括表面抛光,并且其中表面抛光直接在多个导电焊盘的顶表面上。

[0079]

在示例4中,示例1-3的主题可以任选地包括:其中多个导电焊盘是多个铜焊盘,其中电介质包括二氧化硅材料,并且其中表面抛光包括锡材料。

[0080]

在示例5中,示例1-4的主题可以任选地包括,其中桥是emib,并且其中emib通信耦合到多个管芯。

[0081]

在示例6中,示例1-5的主题可以任选地包括:其中hdp衬底包括多个导电互连,其中多个管芯包括多个第二导电焊盘和第一电介质,其中多个第二导电焊盘和第一电介质在多个管芯的底表面上,其中第一电介质围绕多个第二导电焊盘,其中多个tmv从hdp衬底的顶表面垂直延伸到多个管芯的底表面,并且其中多个tmv将hdp衬底的多个导电互连导电耦合到多个管芯的多个第二导电焊盘。

[0082]

在示例7中,示例1-6的主题可以任选地包括:hdp衬底的底表面上的多个第一导电焊盘;封装衬底上方的hdp衬底,其中hdp衬底的多个第一导电焊盘用多个焊料球导电耦合到封装衬底;在多个管芯、多个第一和第二导电焊盘、第一电介质、多个tmv、桥、混合层、hdp衬底上方并且围绕它们的包封层,其中包封层具有与多个管芯的顶表面基本共面的顶表面,并且其中包封层具有与多个第一导电焊盘的底表面基本共面的底表面;以及包封层和封装衬底上方的底填材料,其中底填材料在包封层的底表面和封装衬底的顶表面之间,并且其中,底填材料围绕包封层和多个焊料球。

[0083]

在示例8中,示例1-7的主题可以任选地包括:其中,多个tmv包括多个第一tmv和多个第二tmv,其中多个第一tmv的宽度大于多个第二tmv的宽度,其中多个第二导电焊盘包括多个第三导电焊盘和多个第四导电焊盘,其中多个第三导电焊盘的宽度大于多个第四导电焊盘的宽度,其中多个第一tmv直接耦合到多个第三导电焊盘,并且其中多个第二tmv直接耦合到多个第四导电焊盘。

[0084]

在示例9中,示例1-8的主题可以任选地包括:桥的混合层的表面抛光直接耦合到多个管芯中的两个管芯的多个第四导电焊盘,并且其中,表面抛光直接在桥的混合层的多个导电焊盘与多个管芯中的两个管芯的多个第四导电焊盘之间。

[0085]

在示例10中,示例1-9的主题可以任选地包括:桥是薄桥,并且其中,薄桥的厚度大约或小于15μm,其中薄桥无需焊料材料而直接耦合到多个管芯中的两个管芯和hdp衬底,并且其中,薄桥包括多个tsv以耦合hdp衬底和多个管芯。

[0086]

示例11是一种形成半导体封装的方法,包括:在载体上方设置多个管芯,其中多个管芯用粘合剂层耦合到载体;在多个管芯中的两个管芯上方设置桥,其中桥包括混合层,并且其中桥用混合层直接耦合到两个管芯;在多个管芯上方设置多个tmv,其中多个tmv围绕桥;在多个管芯、桥、混合层、多个tmv和粘合剂层上方设置包封层;以及在包封层、多个tmv、桥和多个管芯上方设置hdp衬底,其中多个tmv将hdp衬底耦合到多个管芯,其中多个tmv的厚度基本等于桥的厚度,其中桥耦合在多个管芯和hdp衬底之间,其中桥的混合层的顶表面直接在多个管芯的底表面上,并且其中桥的底表面直接在hdp衬底的顶表面上。

[0087]

在示例12中,示例11的主题可以任选地包括:桥的混合层包括多个导电焊盘和电介质,并且其中电介质围绕多个导电焊盘。

[0088]

在示例13中,示例11-12的主题可以任选地包括:桥的混合层还包括表面抛光,并且其中表面抛光直接在多个导电焊盘的顶表面上。

[0089]

在示例14中,示例11-13的主题可以任选地包括:多个导电焊盘是多个铜焊盘,其中电介质包括二氧化硅材料,并且其中表面抛光包括锡材料。

[0090]

在示例15中,示例11-14的主题可以任选地包括,桥是emib,并且其中emib通信耦合到多个管芯。

[0091]

在示例16中,示例11-15的主题可以任选地包括:其中hdp衬底包括多个导电互连,其中多个管芯包括多个第二导电焊盘和第一电介质,其中多个第二导电焊盘和第一电介质在多个管芯的底表面上,其中第一电介质围绕多个第二导电焊盘,其中多个tmv从hdp衬底的顶表面垂直延伸到多个管芯的底表面,并且其中,多个tmv将hdp衬底的多个导电互连导电耦合到多个管芯的多个第二导电焊盘。

[0092]

在示例17中,示例11-16的主题可以任选地包括:在hdp衬底的底表面上设置多个第一导电焊盘;在多个第一导电焊盘和hdp衬底上方和周围设置包封层,其中包封层围绕多个管芯、多个第一和第二导电焊盘、第一电介质、多个tmv、桥、混合层、hdp衬底,其中包封层具有与多个管芯的顶表面基本共面的顶表面,并且其中包封层具有与多个第一导电焊盘的底表面基本共面的底表面;去除载体以暴露包封层的顶表面和多个管芯的顶表面;在封装衬底上方设置包封层和hdp衬底的底表面,其中hdp衬底的多个第一导电焊盘用多个焊料球导电耦合到封装衬底;以及在包封层和封装衬底上方设置底填材料,其中底填材料在包封层的底表面和封装衬底的顶表面之间,并且其中底填材料围绕包封层和多个焊料球。

[0093]

在示例18中,示例11-17的主题可以任选地包括:多个tmv包括多个第一tmv和多个第二tmv,其中多个第一tmv的宽度大于多个第二tmv的宽度,其中多个第二导电焊盘包括多个第三导电焊盘和多个第四导电焊盘,其中多个第三导电焊盘的宽度大于多个第四导电焊盘的宽度,其中多个第一tmv直接耦合到多个第三导电焊盘,并且其中多个第二tmv直接耦合到多个第四导电焊盘。

[0094]

在示例19中,示例11-18的主题可以任选地包括:桥的混合层的表面抛光直接耦合到多个管芯中的两个管芯的多个第四导电焊盘,并且其中表面抛光直接在桥的混合层的多个导电焊盘和多个管芯中的两个管芯的多个第四导电焊盘之间。

[0095]

在示例20中,示例11-19的主题可以任选地包括:桥是薄桥,并且其中薄桥的厚度大约或小于15μm,其中薄桥无需焊料材料而直接耦合到多个管芯中的两个管芯和hdp衬底,并且其中薄桥包括多个tsv以耦合hdp衬底和多个管芯。

[0096]

示例21是一种半导体封装,包括:封装衬底上方的hdp衬底;hdp衬底上的桥,其中桥包括混合层,并且其中混合层包括多个导电焊盘、表面抛光和电介质;桥和hdp衬底上方的多个管芯,其中桥耦合在多个管芯和hdp衬底之间,其中桥用混合层直接耦合到多个管芯中的两个管芯,其中桥的混合层的顶表面直接在多个管芯的底表面上,并且其中桥的底表面直接在hdp衬底的顶表面上;hdp衬底上的多个tmv,其中多个tmv将hdp衬底耦合到多个管芯,并且其中多个tmv的厚度基本等于桥的厚度;以及在多个管芯、多个tmv、桥、混合层和hdp衬底上方并且围绕它们的包封层,其中包封层的顶表面直接在多个管芯的顶表面上方。

[0097]

在示例22中,示例21的主题可以任选地包括:电介质围绕多个导电焊盘,其中表面抛光直接在多个导电焊盘的顶表面上,其中多个导电焊盘是多个铜焊盘,其中电介质包括

二氧化硅材料,并且其中表面抛光包括锡材料,其中桥是emib,并且其中,emib通信耦合到多个管芯。

[0098]

在示例23中,示例21-22的主题可以任选地包括:hdp衬底包括多个导电互连,其中多个管芯包括多个第二导电焊盘和第一电介质,其中多个第二导电焊盘和第一电介质在多个管芯的底表面上,其中第一电介质围绕多个第二导电焊盘,其中多个tmv从hdp衬底的顶表面垂直延伸到多个管芯的底表面,并且其中多个tmv将hdp衬底的多个导电互连导电耦合到多个管芯的多个第二导电焊盘。

[0099]

在示例24中,示例21-23的主题可以任选地包括:hdp衬底的底表面上的多个第一导电焊盘;其中hdp衬底的多个第一导电焊盘用多个焊料球导电耦合到封装衬底;其中包封层围绕多个管芯、多个第一和第二导电焊盘、第一电介质、多个tmv、桥、混合层、hdp衬底,其中包封层具有与多个第一导电焊盘的底表面基本共面的底表面;包封层和封装衬底上方的底填材料,其中底填材料在包封层的底表面和封装衬底的顶表面之间,并且其中底填材料围绕包封层和多个焊料球;以及多个管芯的顶表面和包封层的顶表面上方的一个或多个热器件。

[0100]

在示例25中,示例21-24的主题可以任选地包括:多个tmv包括多个第一tmv和多个第二tmv,其中多个第一tmv的宽度大于多个第二tmv的宽度,其中多个第二导电焊盘包括多个第三导电焊盘和多个第四导电焊盘,其中多个第三导电焊盘的宽度大于多个第四导电焊盘的宽度,其中多个第一tmv直接耦合到多个第三导电焊盘,并且其中多个第二tmv直接耦合到多个第四导电焊盘,其中桥的混合层的表面抛光直接耦合到多个管芯中的两个管芯的多个第四导电焊盘,其中表面抛光直接在桥的混合层的多个导电焊盘与多个管芯中的两个管芯的多个第四导电焊盘之间,其中桥是薄桥,其中薄桥的厚度大约或小于15μm,其中薄桥无需焊料材料而直接耦合到多个管芯中的两个管芯和hdp衬底,并且其中薄桥包括多个tsv以耦合hdp衬底和多个管芯。

[0101]

在以上说明书中,已经参考其特定示例性实施例描述了方法和设备。显而易见的是,在不脱离更广泛的实质和范围的情况下,可以对其进行各种修改。因此,说明书和附图应被认为是出于说明性目的而非限制性目的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1