电子封装件及其承载基板的制作方法

1.本发明有关一种半导体封装结构,尤指一种电子封装件及其承载基板。

背景技术:

2.现有半导体封装基板的内部依功能需求配置多个线路,如具有传输信号(signal)、接地(ground)及电源(power)等功能的线路。

3.图1a为现有封装基板1的剖面示意图。如图1a所示,所述的封装基板1包括:一核心层10、至少一贯通该核心层10的导电通孔100、及形成于该核心层10上且电性连接该导电通孔100的增层结构11。该增层结构11具有多个介电层110、多个设于该介电层110上的线路层111及多个设于该介电层110中并电性连接各该线路层111的导电盲孔112。

4.该增层结构11于接触该核心层10的线路层111配置有一差分信号部12,其包含用以输入信号的第一信号线路13a、用以输出信号的第二信号线路13b、第一接地线路14a及第二接地线路14b,且该第一信号线路13a与第二信号线路13b作为信号组,以通过两者的信号传输方向分别为一进一出的相反方向,及该第一信号线路13a与第二信号线路13b的布线路径大致设计为相似且等长(如图1b所示),使两者的信号之间的杂讯尽可能相互抵消,且于该第一信号线路13a与第二信号线路13b的外侧分别配置第一接地线路14a及第二接地线路14b(如图1c所示),并于该差分信号部12的上、下侧分别配置接地层120,以屏蔽该第一信号线路13a与第二信号线路13b的信号,使该第一信号线路13a与第二信号线路13b的信号不受外界信号或杂讯干扰。

5.然而,现有差分信号部12中,该第一信号线路13a与第二信号线路13b的布线路径常无法符合实际设计需求。例如,为了配合其它线路的配置,该第一信号线路13a与第二信号线路13b需弯曲布设(如图1b所示),若两者需对称或平行布设,则两者无法等长;若两者需等长配置,则不仅需耗时设计两者的路径(需考虑其它功能线路的路径),且两者难以对称或平行布设。因此,现有差分信号部12常因无法满足该第一信号线路13a与第二信号线路13b的布线路径相同且等长的设计需求,因而两者的信号之间的杂讯的抵消程度难以符合实际需求。

6.此外,该差分信号部12的信号组配置于同一线路层111,致使该核心层10的布设面积需考虑该第一信号线路13a、第二信号线路13b、第一接地线路14a及第二接地线路14b的布设路径,因而难以缩减该核心层10的布设面积,导致该封装基板1难以符合微小化的需求。

7.因此,如何克服上述现有技术的种种问题,实已成目前亟欲解决的课题。

技术实现要素:

8.鉴于上述现有技术的种种缺陷,本发明提供一种电子封装件及其承载基板,使两者的信号之间的杂讯的抵消程度符合需求。

9.本发明的承载基板包括:线路板体;第一信号层,其设于该线路板体中,用以传输

差分信号;以及第二信号层,其设于该线路板体中且间隔堆叠于该第一信号层的其中一侧,用以传输差分信号。

10.前述的承载基板中,该线路板体包含绝缘部及结合该绝缘部的线路部,使该线路部电性连接该第一信号层与第二信号层。

11.前述的承载基板中,该线路板体包含一核心层,其具有相对的第一表面与第二表面及至少一连通该第一表面与第二表面的导电通孔,且于该第一表面与第二表面上形成增层结构,以令该第一信号层与第二信号层配置于该增层结构中。例如,该第一信号层位于该核心层的第一表面上,且该第二信号层位于该核心层的第二表面上。另外,还可于该第一信号层与第二信号层两侧设置接地线路。

12.前述的承载基板中,还包括设于该线路板体中的第一接地层,其间隔堆叠于该第一信号层的另一侧。

13.前述的承载基板中,还包括设于该线路板体中的第二接地层,其与该第二信号层间隔堆叠。

14.本发明还提供一种电子封装件,包括:前述的承载基板;以及电子元件,其结合该承载基板且电性连接该承载基板。

15.前述的电子封装件中,该电子元件电性连接该第一信号层与第二信号层。

16.前述的电子封装件中,还包括多个结合该承载基板的导电元件。

17.由上可知,本发明的电子封装件及其承载基板中,主要通过第二信号层间隔堆叠于该第一信号层的其中一侧,使两者的长度及形状一致,故相比于现有技术,本发明的第一信号层与第二信号层的布线路径能符合需求,使两者的信号之间的杂讯的抵消程度符合需求。

18.此外,通过该第一信号层与第二信号层相互堆叠配置,使该承载基板的单一层线路布设面积仅需考虑该第一或第二信号层的布设路径,故相比于现有技术,该承载基板能有效缩减其布设面积,以利于该承载基板的微小化。

附图说明

19.图1a为现有封装基板的剖面示意图。

20.图1b为图1a的局部上视示意图。

21.图1c为图1a的局部立体示意图。

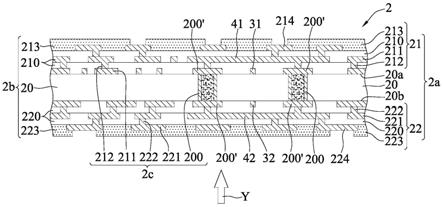

22.图2a为本发明的承载基板的剖视示意图。

23.图2b为图2a的局部立体示意图。

24.图3为本发明的承载基板与现有封装基板的插入损失的比较曲线图。

25.图4为本发明的电子封装件的剖视示意图。

26.附图标记说明

27.1:封装基板

28.10:核心层

29.100:导电通孔

30.11:增层结构

31.110:介电层

32.111:线路层

33.112:导电盲孔

34.12:差分信号部

35.120:接地层

36.13a:第一信号线路

37.13b:第二信号线路

38.14a:第一接地线路

39.14b:第二接地线路

40.2:承载基板

41.2a:线路板体

42.2b:绝缘部

43.2c:线路部

44.20:核心层

45.20a:第一表面

46.20b:第二表面

47.200:导电通孔

48.200’:垫部

49.21:第一增层结构

50.210:第一介电层

51.211:第一线路层

52.211’,221’:接地线路

53.212:第一导电盲孔

54.213:第一绝缘保护层

55.214:电性接触垫

56.22:第二增层结构

57.220:第二介电层

58.221:第二线路层

59.222:第二导电盲孔

60.223:第二绝缘保护层

61.224:植球垫

62.31:第一信号层

63.32:第二信号层

64.41:第一接地层

65.42:第二接地层

66.5:电子封装件

67.50:电子元件

68.500:导电凸块

69.51:导电元件

70.52:封装层

71.p1,p2:分贝比例

72.y:箭头方向。

具体实施方式

73.以下通过特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其他优点及功效。

74.须知,本说明书所附附图所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供本领域技术人员的了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等的用语,也仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本发明可实施的范畴。

75.图2a至图2b为本发明的承载基板2的示意图。如图2a所示,所述的承载基板2包括:一线路板体2a、设于该线路板体2a中的第一信号层31、第二信号层32、第一接地层41及第二接地层42。

76.于本实施例中,该线路板体2a包含一绝缘部2b及结合该绝缘部2b的线路部2c,且令该线路部2c电性连接该第二接地层42、第二信号层32、第一信号层31与第一接地层41。

77.例如,该线路板体2a包含一核心层20,其具有相对的第一表面20a与第二表面20b及至少一连通该第一表面20a与第二表面20b的导电通孔200,且于该第一表面20a与第二表面20b上分别形成第一增层结构21与第二增层结构22,以令该第二接地层42、第二信号层32、第一信号层31与第一接地层41配置于该第一增层结构21与第二增层结构22中。

78.进一步,该第一增层结构21具有多个第一介电层210、多个设于该第一介电层210上的第一线路层211及多个设于该第一介电层210中并电性连接各该第一线路层211的第一导电盲孔212,且该第一增层结构21于最外侧可形成有一如防焊层的第一绝缘保护层213,以令该第一绝缘保护层213外露部分该第一线路层211,从而供作为电性接触垫214。例如,该第一线路层211可为扇出(fan out)型重布线路层(redistribution layer,简称rdl),且该第一介电层210的介电材为如聚对二唑苯(polybenzoxazole,简称pbo)、聚酰亚胺(polyimide,简称pi)、预浸材(prepreg,简称pp)等。

79.相同地,该第二增层结构22具有多个第二介电层220、多个设于该第二介电层220上的第二线路层221及多个设于该第二介电层220中并电性连接各该第二线路层221的第二导电盲孔222,且该第二增层结构22于最外侧可形成有一如防焊层的第二绝缘保护层223,以令该第二绝缘保护层223外露部分该第二线路层221,从而供作为植球垫224。例如,该第二线路层221可为扇出(fan out)型重布线路层(redistribution layer,简称rdl),且该第二介电层220的介电材为如聚对二唑苯(polybenzoxazole,简称pbo)、聚酰亚胺(polyimide,简称pi)、预浸材(prepreg,简称pp)等。

80.因此,于本实施例中,该绝缘部2b包含该核心层20、第一介电层210、第一绝缘保护层213、第二介电层220及第二绝缘保护层223,且该线路部2c包含该导电通孔200、第一线路层211、第一导电盲孔212、第二线路层221及第二导电盲孔222。应可理解地,有关该线路板

体2a的形式种类繁多,如无核心层(coreless)形式,故其构造并不限于上述。

81.所述的第一信号层31设于该核心层20的第一表面20a上且电性连接该第一线路层211。

82.于本实施例中,该第一信号层31包含至少一线体(如图2b所示),其用以传输差分信号。例如,该第一增层结构21于制作最内侧的第一线路层211时,可一并制作该第一信号层31。

83.所述的第二信号层32设于该核心层20的第二表面20b上且电性连接该第二线路层221。

84.于本实施例中,该第二信号层32包含至少一线体(如图2b所示),其用以传输差分信号,且该第二信号层32间隔堆叠于该第一信号层31的一侧。例如,该第二增层结构22于制作最内侧的第二线路层221时,可一并制作该第二信号层32,使该第二信号层32与该第一信号层31通过该核心层20相互间隔堆叠。

85.所述的第一接地层41设于该第一介电层210上且电性连接该第一线路层211与第一导电盲孔212。

86.于本实施例中,该第一接地层41包含一片体(如图2b所示),其间隔堆叠于该第一信号层31的另一侧。例如,该第一增层结构21于制作外侧第一线路层211时,可一并制作该第一接地层41,使该第一接地层41与该第一信号层31通过该第一介电层210相互间隔堆叠。

87.所述的第二接地层42设于该第二介电层220上且电性连接该第二线路层221与第二导电盲孔222。

88.于本实施例中,该第二接地层42包含一片体(如图2b所示),其与该第二信号层32相互间隔堆叠,以沿一方向(如图2a所示的由下往上的箭头方向y)依序堆叠该第二接地层42、第二信号层32、第一信号层31与第一接地层41。例如,该第二增层结构22于制作外侧第二线路层221时,可一并制作该第二接地层42,使该第二接地层42与该第二信号层32通过该第二介电层220相互间隔堆叠。

89.此外,该导电通孔200通过垫部200’电性连接该第一导电盲孔212与该第二导电盲孔222,使该导电通孔200得以电性连接该第一接地层41与第二接地层42。

90.因此,本发明的承载基板2通过该第一信号层31与第二信号层32相互堆叠配置,即差动信号线路采用重直式布局,使差分信号组的上方线路(如第一信号层31)与下方线路(如第二信号层32)的长度及形状一致(如图2b所示),即以相互垂直投影方式配置两者,故相比于现有技术,本发明的第一信号层31与第二信号层32的布线路径能符合需求,使两者的信号之间的杂讯的抵消程度符合需求,如差分信号的杂讯可完全消除。具体地,以线宽为13微米(um)及阻抗为90欧姆(ohm)的设计,本发明的插入损失(insertion loss)几乎贴合(0.6%@30ghz),且,如图3所示本发明的回波损耗(return loss)的分贝(db)比例p1远小于现有的回波损耗的分贝比例p2,如本发明的回波损耗均在-25db以下的良好表现。

91.此外,本发明的承载基板2将该第一信号层31与第二信号层32相互堆叠配置于上下层(如该核心层20的第一表面20a与第二表面20b),使该核心层20的第一表面20a的布设面积仅需考虑该第一信号层31的布设路径,而其第二表面20b的布设面积仅需考虑该第二信号层32的布设路径,故相比于现有技术,该核心层20的布设面积能缩减21%,因而能有效缩减该核心层20的布设面积,以利于该承载基板2的微小化。

92.另外,若该核心层20的布设面积同于现有封装基板的布设面积,则该核心层20多出来的布设面积可依需求布设其它功能线路,以提升该承载基板2的面积利用率。

93.另外,该第一信号层31与第二信号层32的上下两侧配置如接地片(ground plane)的第一接地层41与第二接地层42,且该第一信号层31与第二信号层32的左右两侧可依需求配置接地线路211’,221’(如图2b所示),以屏蔽该第一信号层31与第二信号层32的信号,使该第一信号层31与第二信号层32的信号不受外界信号或杂讯干扰。

94.本发明还提供一种电子封装件5,包括:承载基板2以及至少一结合该承载基板2的电子元件50。

95.所述的电子元件50电性连接该承载基板2,如电性连接该第一信号层31与第二信号层32。

96.于本实施例中,该电子元件50为主动元件、被动元件或其二者组合,且该主动元件为例如半导体芯片,而该被动元件为例如电阻、电容及电感。例如,该半导体芯片通过多个如焊锡材料、金属柱(pillar)或其它等的导电凸块500以覆晶方式设于该承载基板2的电性接触垫214上以电性连接该第一线路层211与该第一信号层31,且可依需求以如底胶(图略)包覆该些导电凸块500;或者,该电子元件50可通过多个焊线(图未示)以打线方式电性连接该电性接触垫214;亦或,该电子元件50可直接接触该电性接触垫214。应可理解地,有关电子元件50电性连接承载基板2的方式繁多,并不限于上述。

97.此外,可于该承载基板2上形成一包覆该电子元件50的封装层52,其形成材质为绝缘材,如聚酰亚胺(polyimide,简称pi)、干膜(dry film)、环氧树脂(epoxy)或封装层(molding compound)。例如,该封装层52的制程可选择液态封胶(liquid compound)、喷涂(injection)、压合(lamination)或模压(compression molding)等方式形成于该承载基板2上。

98.应可理解地,该电子元件50也可嵌埋于该承载基板2中,以省略该封装层52的制作。因此,有关电子元件50的封装方式繁多,并无特别限制。

99.于一实施例中,该电子封装件5还包括多个结合该承载基板2的导电元件51。例如,该些导电元件51接触结合该植球垫224,以电性连接该第二线路层221。

100.综上所述,本发明的电子封装件及其承载基板,通过该第一信号层与第二信号层相互堆叠配置,使两者的长度及形状一致,故本发明的第一信号层与第二信号层的布线路径能符合需求,使两者的信号之间的杂讯的抵消程度符合需求。

101.此外,本发明的承载基板将该第一信号层与第二信号层相互堆叠配置于上下层,以利于缩减该承载基板的布设面积,故能有效微小化该承载基板。

102.上述实施例仅用以示例性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修改。因此本发明的权利保护范围,应如权利要求书所列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1