一种微型发光二极管显示器的芯片结构的制作方法

1.本发明有关于微型发光二极管显示器,尤其有关于微型发光二极管显示器的芯片结构。

背景技术:

2.微型发光二极管(micro led)显示器,如美国公告第us 10,062,675b2号等等。每一个微发光二极管都是单一个体,都可视为独立的发光模组,由于具有自发光的显示特性,且结构相当简单,没有背光元件,具有低能耗、高亮度的特性可解决目前显示器的耗电与亮度问题,极具发展前景。

3.请再参阅「图1」与「图2」所示,微型发光二极管显示器的驱动电路大致可分为共阴极驱动(如图1所示)与共阳极驱动(如图2所示)两种。如图1所示的共阴极驱动方式,微型发光二极管在形成发光二极管阵列1(led array)之后,相邻位置且不同颜色(通常是r、g、b各一)的发光二极管作为同一个像素2,并共极连接一n通道mosfet(nmos)3,n通道mosfet 3可以控制电流是否通过,而同一个像素2的发光二极管则由不同的源极驱动(source drive)ic 4控制不同颜色发光二极管的通过电流量(电子流),以控制不同颜色发光二极管的发光亮度,因而通过混光方式即可以让像素以全彩的方式显示。而如图2所示的共阳极驱动方式,一个像素2为共极连接一p通道mosfet(pmos)5,p通道mosfet 5可以控制电流是否通过,而不同颜色发光二极管同样由不同的源极驱动(source drive)ic 4控制不同颜色发光二极管的通过电流量(电子流)。

4.如上所述的驱动结构,控制电流是否通过的n通道mosfet 3或p通道mosfet 5为整合于一栅极驱动ic,且该栅极驱动ic为集成电路,当微型发光二极管有高密度与高亮度的使用需求时,该栅极驱动ic会需要乘载高电流,也就是说该栅极驱动ic需要较大的芯片(die)尺寸,因此该栅极驱动ic的栅极通道(gate channel)的数量不能太多,否则会有散热与良率的问题,其会导致需要多个该栅极驱动ic而导致成本高昂。

技术实现要素:

5.爰此,本发明的主要目的在于揭露一种适用于高密度与高亮度的微型发光二极管的芯片结构。

6.本发明为一种微型发光二极管显示器的芯片结构,供连接一输入电压、一主控制电路与一源极驱动(source drive)电路,其包含一封装载板、至少一发光二极管元件、至少一金氧半场效晶体管(mosfet)以及一连接线路。

7.其中,该至少一发光二极管元件位于该封装载板上,该至少一金氧半场效晶体管位于该封装载板上,且该至少一金氧半场效晶体管分别具有一源极、一栅极与一漏极,该至少一源极共极连接该输入电压,该至少一栅极连接至该主控制电路。而该至少一发光二极管元件的一端藉由该连接线路连接该至少一漏极,且该至少一发光二极管元件的另一端独立连接该源极驱动电路。

8.据此,本发明为整合金氧半场效晶体管(mosfet)于芯片结构内,并通过该主控制电路进行控制mosfet的开关,可节省栅极驱动ic的成本。又传统集成的mosfet电路为分散至每一芯片内,每一芯片内的mosfet仅需乘载单一芯片内的发光二极管元件所需的电流,即每一芯片内的mosfet乘载的电流相对较小,更可通过该封装板散热,因此散热良好,可满足微型发光二极管有高密度与高亮度的使用需求。

9.以下结合附图和具体实施例对本发明进行详细描述,但不作为对本发明的限定。

附图说明

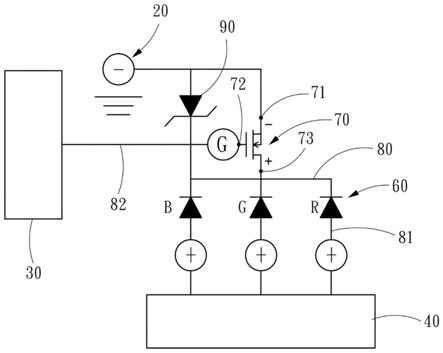

10.图1,为现有共阴极驱动方式电路示意图;

11.图2,为现有共阳极驱动方式电路示意图;

12.图3,为本发明芯片结构电路示意图;

13.图4a,为本发明芯片结构俯视示意图;

14.图4b,为本发明芯片结构侧视示意图;

15.图5,为本发明另一芯片结构电路示意图;

16.图6,第一实施例的电路示意图;

17.图7,第二实施例的电路示意图;

18.图8,第三实施例的电路示意图;

19.图9,第四实施例的电路示意图;

20.图10,第五实施例的电路示意图;

21.图11,第六实施例的电路示意图;

22.图12,第七实施例的电路示意图。

具体实施方式

23.为对本发明的特征、目的及功效,有着更加深入的了解与认同,兹列举一较佳实施例并配合附图说明如后:

24.请参阅「图3」、「图4a」与「图4b」所示,本发明为一种微型发光二极管显示器的芯片结构,供连接一输入电压20、一主控制电路30与一源极驱动(source drive)电路40,其包含一封装载板50、至少一发光二极管元件60、至少一金氧半场效晶体管70(mosfet)以及一连接线路80。如「图3」所示的图式,该至少一金氧半场效晶体管70为一个,而该至少一发光二极管元件60为三个且分别以红光(r)二极管、绿光(g)二极管与蓝光(b)二极管为例加以说明,在实际实施时,该至少一发光二极管元件60可以为单个或单一颜色或特定的颜色,端赖实际的使用需求而决定。

25.其中,该至少一发光二极管元件60位于该封装载板50上,且该至少一金氧半场效晶体管70位于该封装载板50上,并该至少一金氧半场效晶体管70分别具有一源极71、一栅极72与一漏极73,该至少一源极71共极连接该输入电压20,该至少一栅极72连接至该主控制电路30。而该至少一发光二极管元件60的一端藉由该连接线路80连接该至少一漏极73,且该至少一发光二极管元件60的另一端独立连接该源极驱动电路40。在实际实施时,每一该发光二极管元件60可以藉由一第一接电线路81独立连接该源极驱动电路40;而每一该栅极72则可藉由一第二接电线路82与该主控制电路30连接。

26.在实际结构上,一实施例如「图4a」与「图4b」所示,该至少一发光二极管元件60与该至少一金氧半场效晶体管70可以为覆晶连接于该封装载板50上,而该连接线路80为以电镀铜工艺制成,更明确的说,该连接线路80可以电镀铜工艺取代传统的打线工艺,以快速量产化。而连接该输入电压20、该主控制电路30与该源极驱动(source drive)电路40所需的接点与线路为设置于该封装载板50上,为属于封装工艺的一部分,在此不多加叙述。另为了个别保护每一该至少一发光二极管元件60免受静电的破坏,于「图3」所示的电路结构,该栅极72与该源极71之间可以连接一静电保护二极管90,藉此可降低寄生电容的影响而提升画质,并可优化亮度及消耗电力速度,提升电力的使用效率。

27.请参阅「图5」所示,为本发明另一芯片结构电路示意图。其中该至少一发光二极管元件60可以为多个且具有不同的颜色并分组形成多个像素91,该多个像素91为a

×

b矩阵排列(如图5所示为2

×

2矩阵),而该至少一金氧半场效晶体管70具有a个,且同一列的该发光二极管元件60为连接至同一个该金氧半场效晶体管70的该漏极73。也就是说,同一列的该发光二极管元件60为共同使用同一个该金氧半场效晶体管70,藉以节省使用成本。而在其他实施例中,亦可以设计同一行的该发光二极管元件60共同使用同一个该金氧半场效晶体管70,或者让特定数量矩阵排列的该发光二极管元件60,如2

×

2矩阵或3

×

3矩阵内的该发光二极管元件60共同使用同一个该金氧半场效晶体管70。只要简单的改变电路接线设计即可达成。又同样的,每一该金氧半场效晶体管70的该栅极72与该源极71之间连接一静电保护二极管90,藉以降低寄生电容的影响。

28.以下列举几个本发明可行的实施例,该些实施例仅为本发明的部分实施方式,并不对本发明的实施方式形成限制。

29.请参阅「图6」所示,为本发明的第一实施例的电路示意图,于本实施例中,为共阴极驱动方式。该至少一发光二极管元件60为多个且具有不同的颜色并分组形成多个矩阵排列的像素,且该至少一金氧半场效晶体管70为使用n通道mosfet,且该至少一金氧半场效晶体管70的数量相同于该至少一发光二极管元件60的数量,并该多个发光二极管元件60为一对一连接至对应的该金氧半场效晶体管70。

30.请参阅「图7」所示,为本发明的第二实施例的电路示意图,于本实施例中,为与第一实施例类似,但改为共阳极驱动方式。同样的,该至少一发光二极管元件60为多个且具有不同的颜色并分组形成多个矩阵排列的像素,且该至少一金氧半场效晶体管70a为使用p通道mosfet,且该至少一金氧半场效晶体管70a的数量相同于该至少一发光二极管元件60的数量,并该多个发光二极管元件60为一对一连接至对应的该金氧半场效晶体管70a。

31.请参阅「图8」所示,为本发明的第三实施例的电路示意图,于本实施例中,为以第一实施例为基础,为共阴极驱动方式,并加上静电破获(esd)保护。其中该第一接电线路81与一接地端93之间连接一静电保护二极管90。

32.请参阅「图9」所示,为本发明的第四实施例的电路示意图,于本实施例中,为以第一实施例为基础,为共阴极驱动方式,并加上静电破获(esd)保护。其中每一该发光二极管元件60并联一静电保护二极管90。

33.请参阅「图10」所示,为本发明的第五实施例的电路示意图,为共阴极驱动方式。其中该至少一发光二极管元件60为多个且具有不同的颜色并分组形成多个矩阵排列的像素91,且该至少一金氧半场效晶体管70的数量相同于该多个像素91的数量,并同一该像素91

的该多个发光二极管元件60为连接至对应该像素91的该金氧半场效晶体管70。

34.请参阅「图11」所示,为本发明的第六实施例的电路示意图,于本实施例中,为以第五实施例为基础,为共阴极驱动方式,并加上静电破获(esd)保护。其中每一该金氧半场效晶体管70的该栅极72与该源极71之间连接一静电保护二极管90。

35.请参阅「图12」所示,为本发明的第七实施例的电路示意图,于本实施例中,为以第五实施例为基础,为共阴极驱动方式,并加上静电破获(esd)保护。其中该第二接电线路82与一接地端93之间连接一静电保护二极管90。

36.如上所述,本发明的特点至少包含:

37.1.让该至少一金氧半场效晶体管设置于该封装载板上而分散设置于各芯片结构内,每一芯片内的mosfet仅需乘载单一芯片内的发光二极管元件所需的电流,即每一芯片内的mosfet乘载的电流相对较小,更可通过该封装板散热,因此散热良好,可满足微型发光二极管高密度(dot pitch《0.5mm)或高亮度(》1000nits)的使用需求。

38.2.整合该静电保护二极管于芯片结构内,可降低寄生电容的影响而提升画质,并可优化亮度及消耗电力速度,提升电力的使用效率。

39.3.不需要传统的栅极驱动ic,可改由该主控制电路控制栅极的开关,以解省成本。

40.4.可使用电镀铜工艺,降低成本,生产速度可加快,可靠度提升,且不需要打线(wire bonding)或铜柱元件。

41.当然,本发明还可有其它多种实施例,在不背离本发明精神及其实质的情况下,熟悉本领域的技术人员当可根据本发明作出各种相应的改变和变形,但这些相应的改变和变形都应属于本发明所附的权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1