芯片零件的制作方法

1.本发明涉及在组件本体的两端设置有焊接用外部电极的表面安装型芯片零件及其制造方法。

背景技术:

2.片式电阻器是芯片零件中的一个例子,主要是由长方体状的绝缘基板(组件本体)、在绝缘基板的表面上以特定间隔面对配置的一对表面电极、桥接成对的表面电极的电阻器(功能组件)、覆盖电阻器的保护膜、在绝缘基板的背面以特定间隔面对配置的一对背面电极、桥接相对应的表面电极及背面电极的一对端面电极,及一对覆盖表面电极、背面电极和端面电极并形成于绝缘基板两端的外部电极等所构成。

3.表面电极、背面电极及端面电极构成内部电极,是以银(ag)或铜(cu)为主要成分的材料所形成。外部电极是由附着在内部电极表面以镍(ni)为主成分的阻挡层以及附着在阻挡层表面以锡(sn)为主成分的外部连接层所构成。阻挡层以及外部连接层是通过电解电镀所形成。

4.将片式电阻器设置在电路板上时,在电路板上设置的布线图案的焊盘上涂敷焊料后,将片式电阻器安放在电路板上,使得外部连接层与焊料重叠,并在此状态下将焊料熔化、固化,使外部连接层焊接于焊盘。用作焊接的材料例如,使用锡(sn)和铅(pb)以大约6:4(sn63%-pb37%)的比例混合的焊锡材料,称为共晶焊锡。具有这样组成比例的共晶焊锡的熔点为183℃,但为了使焊锡熔融需要加热到熔点以上,因此构成内部电极的ag和cu在焊接时,可能会发生因焊接热而熔化到材料一侧的现象,即所谓“焊料咬合”的现象。

5.为了防止焊料咬合,设置了由镀镍构成的阻挡层,已知如果镀镍层的厚度为2μm以上,则能够有效地防止焊料咬合。但是,当镀镍层为较厚的状况时(尤其是15μm以上),镀镍层则容易因外部应力而从绝缘基板上剥离,可能会有因剥离后造成的断线,或是因腐蚀气体而生成剥离部件硫化的疑虑。因此,如专利文献1所述,以往是通过在片式电阻器的内部电极上閃镀非常薄的金(au)后,依次形成镀镍层(阻挡层)和镀锡层(外部连接层)的方式,提供了提高构成阻挡层的镀镍层的粘附性的终端电极结构。

6.现有技术文献

7.专利文献

8.专利文献1日本特开平7-230904号公报

技术实现要素:

9.本发明所要解决的问题

10.近年来,从地球环境保护的观点提倡无铅化,使用几乎不含铅的无铅焊料。例如使用sn96.5%-ag3%-cu0.5%的组成的无铅焊锡时,无铅焊锡的熔点为220℃,比起使用共晶焊锡时,焊接安装时的加热温度变高,因此构成阻挡层的镍容易向焊锡材料一侧熔出。因此,虽然有必要加厚镀镍层以防止焊料咬合,但是当镀镍层变厚时,镀镍层将变得更容易剥

落,同时也很难防止焊料咬合。再者,将镀镍层加厚的话,所花费的时间和材料成本也会增加。像是如专利文献1所述的终端电极结构,在镀镍层的基底闪镀上非常薄的金,则可以提高镀镍层的黏附性,但会有闪镀薄层金的成本问题。

11.本发明是鉴于现有技术的这种实际情况而完成的,其第一目的在于提供一种具有终端电极结构的芯片零件,所述结构能够防止焊料咬合和剥落。其第二目的在于提供一种制造所述芯片零件的方法。

12.用于解决问题的手段

13.为了达成上述第一目的,本发明芯片零件包括形成有功能组件的组件本体、与功能组件连接并覆盖组件本体两端的一对内部电极、形成于内部电极表面且以镍为主要成分的阻挡层及形成于阻挡层表面且以锡为主要成分的外部连接层;其中,阻挡层由电镀形成的镍和磷的合金镀层构成,合金镀层中的磷含有率在与内部电极连接的内侧区域和与外部连接层连接的外侧区域之间不同,且至少阻挡层的内侧区域具有磁性。

14.如上述构成的芯片零件,其中,用作外部连接层的基底层的阻挡层,是以镍(ni)用作主要成分及含有磷(p)的合金(ni-p)镀层所形成,由于合金镀层中向锡的扩散比镍慢,即使阻挡层没有形成较厚的厚度,也可以防止焊料在高温使用下发生焊料咬合。此外,通过使构成阻挡层的合金镀层中的磷含有率在内侧区域和外侧区域之间不同,使至少阻挡层的内侧区域具有磁性,因此可以利用其磁性,例如在产品检查过程中进行磁性分类,或是将产品存储至带状封装体的封装步骤,或是当产品从封装体中取出并安装在电路板上时,可以根据其磁性稳定产品的位置。

15.在具有上述结构的芯片零件中,为了使得阻挡层的内侧区域具有磁性,阻挡层内侧区域的磷含有率为5%以下较为适合。

16.为了达成上述第二目的,本发明芯片零件的制造方法包括以下步骤:在组件本体上形成功能组件;形成一对覆盖所述组件本体两端的内部电极;通过电解电镀在内部电极的表面上形成以镍用作主要成分及含有磷的阻挡层;通过电解电镀在阻挡层的表面形成以锡用作主要成分的外部连接层,其中,在形成阻挡层的电解电镀步骤中,通过随时间改变电流密度,使得与内部电极连接的内侧区域和与外部连接层连接的外侧区域之间的磷含有率不同。

17.如上述构成的芯片零件,其中,用作外部连接层的基底层的阻挡层,是以镍(ni)用作主要成分及含有磷(p)的合金(ni-p)镀层所形成,由于合金镀层中向锡的扩散比镍慢,即使阻挡层没有形成较厚的厚度,也可以防止焊料在高温使用下发生焊料咬合。此外,在形成阻挡层的电解电镀步骤中,因为电流密度随时间变化,使得合金镀层中的磷含有率在内侧区域和外侧区域之间不同,在阻挡层形成了磷含有率低的区域和磷含有率高的区域,通过磷含有率低的区域,可以使阻挡层具有磁性。因此可以利用其磁性,例如在产品检查过程中进行磁性分类,或是于将产品存储至带状封装体的封装步骤,或是当产品从封装体中取出并安装在电路板上时,可以根据其磁性稳定产品的位置。

18.在这种情况下,在形成阻挡层的电解电镀步骤中,先以特定的电流密度进行电解电镀,形成磷含有率为0.5%以下的低磷镀层之后,降低电流密度,形成磷含有率较高的高磷镀层,如此只需控制电解电镀的电流密度,就可以容易地形成兼具磁性和耐热性的阻挡层。

19.发明效果

20.根据本发明芯片零件及其制造方法,能够防止用作外部连接层的基底层所形成阻挡层的焊锡发生焊料咬合及剥离,并且通过利用赋予阻挡层的磁性,可以稳定地进行产品检查步骤和封装步骤。

附图说明

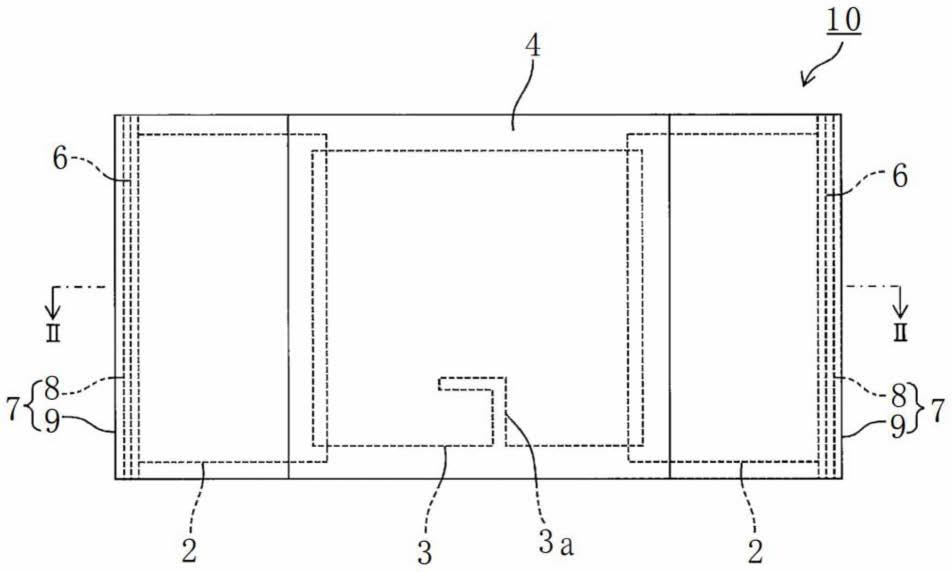

21.图1是本发明实施例的片式电阻器的平面图。

22.图2是沿着图1的ii-ii线的剖面图。

23.图3是表示片式电阻器的制造步骤的流程图。

具体实施方式

24.本发明的实施型态,以下参照附图对应本发明的实施方式进行说明,图1是本发明的实施例的片式电阻器10的平面图,图2是沿着图1中ii-ii线的剖面图。

25.如图1和图2所示,用作芯片零件一例的片式电阻器10主要具有长方体状的绝缘基板1、一对形成于绝缘基板1的表面上长边方向两端的表面电极2、桥接于表面电极2之间的电阻器3、覆盖住整个电阻器3及部份表面电极2的保护层4、一对形成于绝缘基板1的背面上长边方向两端的背面电极5、一对形成于绝缘基板1的长边方向的两个端面上并在对应的表面电极2和背面电极5之间导通的端面电极6,以及一对覆盖表面电极2、背面电极5以及端面电极6的外部电极7。

26.绝缘基板1是由陶瓷等构成的组件本体,通过将片状的大型基板沿着纵横延伸的1次分割槽和2次分割槽分割而得到多个基板。

27.成对的表面电极2在绝缘基板1的相对的短边一侧上以特定间隔形成矩形状,表面电极2是使用ag系焊料进行丝网印刷,并使其干燥及加热烧成而制成。

28.电阻器3为功能组件,其中,电阻器3是使用氧化钌等电阻焊料进行丝网印刷,并使其进行干燥及烧成而制成。电阻器3在平面图中形成为矩形,其长边方向的两端个别和表面电极2重叠。其中,整修槽3a形成在电阻器3上,并通过整修槽3a调整电阻器3的电阻值。

29.保护层4具有底涂层和外涂层的2层结构,底涂层是使用玻璃焊料进行丝网印刷,并使其进行加热烧成而制成,并且在形成整修槽3a之前,底涂层先行形成并覆盖电阻器3。外涂层是使用环氧树脂焊料进行丝网印刷,并进行加热硬化制成,并且在电阻器3形成整修槽3a之后,从底涂层上方覆盖包含整修槽3a、电阻器3及底涂层整体而形成。

30.成对的背面电极5在绝缘基板1的背面的与表面电极2对应的位置以特定间隔形成矩形状,背面电极5是使用ag焊料进行丝网印刷,并使其干燥及烧成而制成。

31.成对的端面电极6是通过在绝缘基板1的端面上进行溅镀ni-cr,或者在绝缘基板1的端面上涂敷ag系焊料并使其加热硬化而制成。端面电极6为在对应的表面电极2和背面电极5之间导通,表面电极2、端面电极6及背面电极5构成横截面为u字形的内部电极。

32.成对的外部电极7由附着在内部电极(表面电极2、端面电极6及背面电极5)的表面的阻挡层8和附着在阻挡层8的表面的外部连接层9所构成。阻挡层8和外部连接层9是通过电解电镀而形成。阻挡层8是以镍(ni)用作主要成分及含有磷(p)的合金镀层(ni-p镀层)所形成,其厚度设定在2μm~15μm的范围内。其中,外部连接层9是以锡(sn)为主要成分的sn镀

层,其厚度设定在2μm~15μm的范围内。

33.其中,在构成阻挡层8的合金镀层中,虽然镍中的磷含量越高,越能抑制向构成外部连接层9的锡的扩散,但磷含量越高时,阻挡层8的磁性就会随之丧失,因此阻挡层8相对于镍的磷含有率保持在5%以下。此时,通过控制电解电镀装置的电流密度,使得阻挡层8中的磷含有率在内侧区域和外侧区域不同,且至少阻挡层8的内侧区域具有磁性。具体来说,即通过在初始阶段在较高的电流密度条件下进行电解电镀,在阻挡层8的内侧区域中形成磷含有率为0.5%以下的低磷含量层之后,通过降低电流密度并在较低的电流密度条件下进行电解电镀,在阻挡层8的外侧区域形成磷含有率为约2%~5%的高磷含量层。

34.接着,参照图3所示的流程图,以下对如上所述构成的所述片式电阻器10的制造方法进行说明。

35.首先,准备可制造多个绝缘基板1的大型基板。大型基板具有格子状的1次分割槽和2次分割槽,被这两个分割槽分割的格子分别用作一个芯片区域,然后,如图3所示,在大型基板上一次执行以下描述的每个步骤。

36.第一步,在大型基板的背面上,使用ag焊料进行丝网印刷并使其干燥,在各芯片形成区域的长边方向的两端以特定间隔形成对向的成对背面电极5(步骤s1)。

37.接着,在大型基板的表面上,使用ag-pd焊料进行丝网印刷并使其干燥,在各芯片形成区域的长边方向的两端以特定间隔形成对向的成对表面电极2(步骤s2)。之后,将表面电极2和背面电极5同时在约850℃的高温下进行烧成。其中,表面电极2以及背面电极5可以个别进行烧成,两者的形成顺序可以相反,表面电极2可以早于背面电极5先行形成。

38.接着,在大型基板的表面上,使用含有氧化钌等电阻焊料进行丝网印刷并使其干燥,在形成两端重叠在表面电极2上的电阻器3之后,将其在约850℃的高温下进行烧成(步骤s3)。

39.接着,在覆盖于电阻器3的区域上,使用玻璃焊料进行丝网印刷并使其干燥,形成覆盖住电阻器3的底涂层之后,将其在约600℃的温度下进行烧成(步骤s4)。

40.接着,通过将探针接触成对的表面电极2来测量电阻器3的电阻值,同时从底涂层上方照射激光,进而在电阻器3中形成整修槽3a并调整电阻值(步骤s5)。

41.接着,在底涂层的上方使用环氧树脂焊料进行丝网印刷,然后在约200℃的温度下进行加热硬化以形成外涂层(步骤s6)。至此,已形成具有由底涂层和外涂层组成的2层结构的保护层4。

42.接着,先将大型基板沿着1次分割槽1次分割成条状基板后(步骤s7),在条状基板的分割面上溅镀ni/cr,以形成用于連接设置在条状基板中正背两面的表面电极2和背面电极5的端面电极6(步骤s8)。其中,条状基板的分割面上溅镀ni/cr的步骤,可由涂敷ag系焊料并使其加热硬化用作形成端面电极6的替代方案。

43.接着,将条状基板沿着2次分割槽2次分割成多个芯片状基板后(步骤s9),通过对芯片状基板进行电镀,在芯片状基板的两端形成覆盖内部电极(表面电极2、端面电极6及背面电极5)的阻挡层8(步骤s10)。阻挡层8由以镍(ni)用作主要成分及含有磷(p)的合金镀层(ni-p镀层)所形成,其厚度设定在2μm~15μm的范围内。

44.其中,在构成阻挡层8的合金镀层中,虽然镍中的磷含量越高,越能抑制向构成下一步骤中所形成的外部连接层9的锡的扩散,但磷含量越高时,阻挡层8的磁性就会随之丧

失,因此阻挡层8相对于镍的磷含有率保持在5%以下。此时,通过控制电解电镀装置的电流密度(单位面积电荷),在初始阶段在较高的电流密度条件下进行电解电镀,在阻挡层8的内侧区域中形成磷含有率为0.5%以下的低磷含量层之后,降低电流密度并在较低的电流密度条件下进行电解电镀,在阻挡层8的外侧区域形成磷含有率为较高(约2%~5%)的高磷含量层。因此,可以通过阻挡层8中磷含有率低的内侧区域具有磁性,同时可以通过阻挡层8中磷含有率高的外侧区域抑制扩散。

45.接着,对芯片状基板进行电解电镀,形成覆盖阻挡层8表面的外部连接层9(步骤s11)。外部连接层9是以锡(sn)为主要成分的sn镀层,其厚度设定在2μm~15μm的范围内,至此形成由阻挡层8及外部连接层9所构成的2层结构的外部电极7,如图1及图2所示。

46.如上所述,在本实施例的所述片式电阻器10中,由镀锡制成的外部连接层9中用作基底层的阻挡层8,是以镍用作主要成分及含有磷的合金镀层所形成,由于合金镀层(ni-p)中向锡的扩散比镍慢,即使没有形成太厚的阻挡层8,也能防止焊料在高温使用下发生焊料咬合。此外,为了防止阻挡层8丧失磁性,通过使得合金镀层中的磷含有率在内侧区域和外侧区域之间不同,使至少阻挡层8的内侧区域具有磁性,因此可以利用其磁性,例如在产品检查过程中进行磁性分类,或是于将产品存储至带状封装体的封装步骤,或是当产品从封装体中取出并安装在电路板上时,可以根据其磁性稳定产品的位置。

47.另外,在本实施例的所述片式电阻器10的制造方法中,在形成阻挡层8的电解电镀步骤中控制电解电镀装置的电流密度,先以较高的电流密度进行电解电镀,于阻挡层8的内侧区域形成磷含有率为0.5%以下的低磷含量层之后,降低电流密度,在阻挡层8的外侧区域形成磷含有率为较高(约2%~5%)的高磷含量层,因此只需控制电解电镀的电流密度,就可以容易地形成兼具磁性和耐热性的阻挡层8。此外,由于仅需要改变电流密度,阻挡层8可以在一次电镀步骤中形成,与在分別的电镀步骤中形成阻挡层8的情况相比,尽管阻挡层8具有不同的磷含有率,但可以形成具有优异粘附性且不会形成界面的阻挡层8。

48.在上述实施例中,虽然在阻挡层8的内侧区域形成磷含有率为0.5%以下的低磷含量层,以及在阻挡层8的外侧区域形成磷含有率为约2%~5%的高磷含量层,但是通过电解电镀过程中,将电流密度从高电流密度条件逐渐变更到低电流密度条件,阻挡层8中从内侧区域到外侧区域的磷含量可以无止尽地增加。

49.此外,在上述实施例中,虽已将本发明应用于具有电阻器3用作功能组件的片式电阻器进行了说明,但对于具有除了电阻器以外的功能组件,例如电感器、电容器等的芯片零件,也适用于本发明。

50.附图标记说明

51.1 绝缘基板(组件本体)

52.2 表面电极(内部电极)

53.3 电阻器(功能组件)

54.4 保护层

55.5 背面电极(内部电极)

56.6 端面电极(内部电极)

57.7 外部电极

58.8 阻挡层

59.9 外部连接层

60.10 片式电阻器(芯片零件)

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1