可重构晶体管器件的制作方法

可重构晶体管器件

1.相关专利申请

2.本技术要求2019年11月15日提交的第62/935,662号临时专利申请的权益,所述公开通过本发明的整体引用,成为本发明的一部分。

技术领域

3.本发明涉及晶体管,具体涉及射频晶体管结构。

背景技术:

4.通过选择性打开和关闭包括晶体管器件的并联晶体管,硅基数字和模拟集成电路模拟晶体管器件外围的可变总栅极宽度。但是,截止晶体管寄生电容、电感和电阻会影响仍打开的晶体管的工作性能。随着频率和输出功率增加,射频(rf)型场效应晶体管(fet)器件(如rf放大器)的性能下降量也随之增加。相应地,采用fet(包括rf放大器)每一端上的隔离开关来提高工作性能。但是,由于隔离开关的优值适中,性能仅得到相对较小的提高。此外,所述隔离开关的数量级通常至少大于放大器外围的有源器件。因此,需要一种新的晶体管结构,在晶体管器件内的通态晶体管和断态晶体管之间提供紧凑性和相对较高的隔离性,以尽量降低寄生效应(降低晶体管器件的性能)的影响。

技术实现要素:

5.本发明公开了一种可重构晶体管器件,包括一个基板、多个晶体管叉指(设置在基板上方的第一区域中)以及一个变相开关(pcs),所述变相开关包括一个第一变相材料(pcm)块(设置在基板上方的第二区域中),用于将所述多个第一晶体管叉指第一组与第一总线选择性耦合,其中,所述第一pcm块在非晶态下电绝缘,在晶态下导电。热元件设置在所述第一pcm块附近,其中,当第一电流范围内的电流流过所述第一热元件时,所述热元件可将所述pcm块保持在第一温度范围内,直至所述第一pcm块转化为非晶态,当第二电流范围内的电流流过所述第一热元件时,可将所述第一pcm块保持在第二温度范围内,直至所述第一pcm块转化为晶态。

6.在结合附图阅读优选实施例的以下详细说明后,本领域技术人员应理解本发明的范围,并认识到其他方面。

附图说明

7.附图纳入并构成本说明书的一部分,显示了本发明的一些方面以及解释本发明的原理。

8.图1为本发明所述基于变相材料(pcm)的变相开关(pcs)第一实施例的剖视图。

9.图2为本发明所述基于pcm的pcs第二实施例的剖视图。

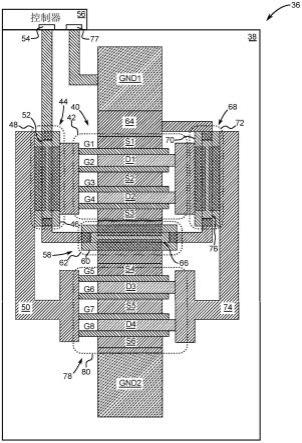

10.图3为根据本发明构造的可重构晶体管器件的一个示例性实施例的布局视图。

11.图4为可重构晶体管器件的最小噪声系数nfmin与频率图,所述可重构晶体管器件

包括四个并联晶体管,每个晶体管均包括用于隔离图3所示可重构晶体管器件等的pcs开关。

12.图5为显示可重构晶体管器件最优γ的史密斯图,所述可重构晶体管器件包括四个并联晶体管,每个晶体管均包括用于隔离图3所示可重构晶体管器件等的pcs开关。

13.图6为可重构晶体管器件的最大增益与频率图,所述可重构晶体管器件包括四个并联晶体管,每个晶体管均包括用于隔离图3所示可重构晶体管器件等的pcs开关。

具体实施方式

14.下文所述实施例代表必要的信息,使本领域技术人员能够实践所述实施例并说明其最佳实践方式。在结合附图阅读以下说明后,本领域技术人员应理解本发明的概念,并认识到本文未具体提及的这些概念的应用。应理解,这些概念和应用均在本发明及所附权利要求的范围内。

15.可以理解的是,虽然术语“第一”、“第二”等在本文中可用于描述各种元件,但这些元件不应受这些术语的限制。这些术语仅用于区分各个元件。例如,在不脱离本发明范围的情况下,可将第一元件称为第二元件,同样,也可将第二元件称为第一元件。在本文中,术语“和/或”包括一个或多个相关所列项目的任何及所有组合。

16.可以理解的是,当提及一个元件(如层、区域或基板)在“另一个元件上”或“延伸到另一个元件上”时,其可直接在其他元件上或直接延伸到其他元件上,或也可存在干预元件。相反,当提及一个元件“直接在另一个元件上”或“直接延伸到另一个元件上”时,则不存在干预元件。同样,可以理解的是,当提及一个元件(如层、区域或基板)“在另一个元件上方”或“延伸到另一个元件上方”时,其可直接在其他元件上方或直接延伸到其他元件上方,或也可存在干预元件。相反,当提及一个元件“直接在另一个元件上方”或“直接延伸到另一个元件上方”时,则不存在干预元件。此外,可以理解的是,当提及一个元件与另一个元件“连接”或“耦合”时,其可与其他元件直接连接或耦合,或也可存在干预元件。相反,当提及一个元件与另一个元件“直接连接”或“直接耦合”时,则不存在干预元件。

[0017]“下方”或“上方”、“上”或“下”、“水平”或“垂直”等相关术语在本文中可用于描述一个元件、层或区域与另一个元件、层或区域的关系(如图中所示)。可以理解的是,除图中所示的方向之外,这些术语及上述内容还旨在包括器件的各个方向。

[0018]

本文所用的术语仅用于说明特定实施例的目的,并不旨在限制本发明。在本文中,除非上下文另有明确说明,否则单数形式“一个(a)”、“一个(an)”和“所述(the)”也包括复数形式。还可以理解的是,在本文中,术语“包括(comprises)”、“包括(comprising)”、“包含(includes)”和/或“包含(including)”规定了存在所述特征、整数、步骤、操作、元件和/或部件,但不排除存在或增加一个或多个其他特征、整数、步骤、操作、元件和/或部件和/或其组合。

[0019]

除非另有定义,否则本文所用的所有术语(包括技术和科学术语)均具有本发明所属领域普通技术人员公知的相同含义。还可以理解的是,除非另有明确定义,否则本文所用的术语应具有与其在本说明书及相关领域背景下的含义一致的含义,而不会在理想化或过于正式的意义上进行解释。

[0020]

图1为本发明所述由变相材料(pcm)12(如硫系变相材料,包括但不限于二氧化钒

(vo2)、碲化锗(gete)和锗锑碲(gst))制成的变相开关(pcs)10的第一示例性实施例的剖视图。pcs 10包括一个由硅或碳化硅等半导体材料制成的基板14。第一半导体触点16和第二半导体触点18横向隔开,并设置在基板14上方。在本示例性实施例中,第一半导体触点16和第二半导体触点18均为氮化镓(gan)高电子迁移率晶体管(hemt)源极触点。但是,第一半导体触点16和第二半导体触点18可以是其他类型的半导体触点,如栅极触点和漏极触点。此外,第一半导体触点16和第二半导体触点18可由砷化镓等其他半导体材料制成。

[0021]

热绝缘层20设置在第一半导体触点16和第二半导体触点18之间的基板14上方。热绝缘层20的热导率在0.1瓦/米-开尔文-0.4瓦/米-开尔文之间。热绝缘层20可由二氧化硅制成,并包括一个用于实现附加绝缘的空气腔。热元件22设置在基板14和热绝缘层20上方。热元件22可由热电半导体材料或用于制造电阻器的欧姆材料制成。此类材料包括但不限于金属和碳化合物。

[0022]

第一介电层24设置在热绝缘层20和热元件22上方。第一介电层24的热导率通常至少为30瓦/米-开尔文。在本示例性实施例中,第一介电层24由氮化硅制成。

[0023]

pcm块12设置在热元件22上方,在本示例性实施例中,pcm块12设置在热元件22上方,pcm块12与热元件22相隔数十纳米-数百纳米。在某些实施例中,pcm块12可直接位于热元件22上。

[0024]

第一金属层段26设置在基板14上方,与第一半导体触点16和pcm块12最左边部分进行电接触。第二金属层段28设置在基板14上方,与第二半导体触点18和pcm块12最右边部分进行电接触,并被pcm块12上方的空隙隔开。在本示例性实施例中,所述空隙在1微米-7微米之间。在某些实施例中,所述空隙在1微米-4微米之间。在其他实施例中,所述空隙在4微米-7微米之间。

[0025]

第二介电层30设置在pcm块12上方的空隙中。第一外部电触点32设置在第一金属层段26上方,并与第一金属层段26和第一半导体触点16进行导电。第二外部电触点34设置在第二金属层段28上方,并与第二金属层段28和第二半导体触点18进行导电。第二介电层30(设置在pcm块12上方的空隙中)将第一外部电触点32和第二外部电触点34进行电隔离。

[0026]

在pcs 10工作时,为了使pcs 10处于断态,通过热元件22驱动电流,使pcm块12的温度从结晶温度tc上升至熔化温度tm,持续大约100纳秒的时间。在这种情况下,熔化温度tm将使pcm块12从晶态转化为非晶态。相反,为了使pcs 10处于通态,通过热元件22驱动电流,将pcm块12的温度保持在结晶温度tc,持续大约1微秒的时间。在这种情况下,结晶温度tc将使pcm块12从非晶态转化为晶态。结晶温度tc和熔化温度tm取决于pcm类型。在某些实施例中,结晶温度tc的范围为100℃-300℃,熔化温度tm的范围为500℃-800℃。

[0027]

图2为本发明所述基于变相材料(pcm)12的变相开关(pcs)10第二实施例的剖视图。在本示例性实施例中,第一pcm块12夹在第一热元件22和基板14之间,热绝缘层20设置热元件22上方。pcs 10第二实施例的操作基本上与图1所示的pcs 10第一实施例的操作相同。

[0028]

图3为根据本发明构造的可重构晶体管器件36的一个示例性实施例的布局视图。可重构晶体管器件36包括一个基板38和多个第一晶体管叉指40(设置在基板38上方的第一区域42中)。第一变相开关(pcs)44包括一个第一变相材料(pcm)块46(设置在基板38上方的第二区域48中),用于将所述多个第一晶体管叉指第一组40与第一总线50选择性耦合,其

中,所述第一pcm块46在非晶态下电绝缘,在晶态下导电。在本示例性实施例中,第一总线50为栅极总线,所述多个第一晶体管叉指第一组40包括栅极叉指g1、g2、g3和g4。第一热元件52设置在第一pcm块46附近,其中,当第一电流范围内的电流流过第一热元件52时,第一热元件52可将第一pcm块46保持在第一温度范围内,直至第一pcm块46转化为非晶态,当第二电流范围内的电流流过第一热元件52时,可将第一pcm块46保持在第二温度范围内,直至第一pcm块46转化为晶态。在一个示例性实施例中,所述第一电流范围为200毫安-500毫安,所述第二电流范围为700毫安-1000毫安。但是,应理解,所述第一电流范围和第二电流范围取决于第一热元件52的实际尺寸和电阻率、薄膜电阻层厚度等。因此,所述第一电流范围和第二电流范围的其他电流强度可分别产生所述第一温度范围和第二温度范围。

[0029]

第一热元件52可与控制器56的一个或多个输出端54耦合,其中,当控制器56在第一持续时间内在一个或多个输出端54产生第一输出电压范围时,在所述第一持续时间内,第一电流范围内的电流流过第一热元件52,当控制器56在第二持续时间内在一个或多个输出端54产生第二输出电压范围时,在所述第二持续时间内,第二电流范围内的电流流过第一热元件52。第一pcs 44可采用图1所示pcs 10第一实施例的结构或图2所示pcs 10第二实施例的结构。

[0030]

可重构晶体管器件36进一步包括一个第二pcs 58,第二pcs 58包括一个第二pcm块60(设置在基板38上方的第三区域62中),用于将所述多个第一晶体管叉指第二组40与第二总线64选择性耦合,其中,第二pcm块60在非晶态下电绝缘,在晶态下导电。在本示例性实施例中,第二总线64为源极总线,所述多个第一晶体管叉指第二组40包括源极叉指s1、s2和s3。

[0031]

第二热元件66设置在第二pcm块60附近,其中,当第一电流范围内的电流流过第二热元件66时,第二热元件66可将第二pcm块60保持在第一温度范围内,直至第二pcm块60转化为非晶态,当第二电流范围内的电流流过第二热元件66时,可将第二pcm块60保持在第二温度范围内,直至第二pcm块60转化为晶态。

[0032]

第二热元件66可与控制器56的一个或多个输出端54耦合,其中,当控制器56在第一持续时间内在一个或多个输出端产生第一输出电压范围时,在所述第一持续时间内,第一电流范围内的电流流过第二热元件66,当控制器56在第二持续时间内在一个或多个输出端54产生第二输出电压范围时,在所述第二持续时间内,第二电流范围内的电流流过第二热元件66。第二pcs 58可采用图1所示pcs 10第一实施例的结构或图2所示pcs 10第二实施例的结构。

[0033]

可重构晶体管器件36进一步包括一个第三pcs 68,第三pcs 68包括一个第三pcm块70(设置在基板38上方的第四区域72中),用于将所述多个第一晶体管叉指第三组40与第三总线74选择性耦合,其中,第三pcm块70在非晶态下电绝缘,在晶态下导电。在本示例性实施例中,第三总线为漏极总线,所述多个第一晶体管叉指第三组40包括漏极叉指d1和d2。

[0034]

第三热元件76设置在所述第三pcm块70附近,其中,当第一电流范围内的电流流过第三热元件76时,第三热元件76可在第一持续时间内将第三pcm块70保持在第一温度范围内,当第二电流范围内的电流流过第三热元件76时,可在第二持续时间内将第三pcm块70保持在第二温度范围内。

[0035]

第三热元件76可与控制器56的一个或多个输出端54耦合,其中,当控制器56在第

一持续时间内在一个或多个输出端54产生第一输出电压范围时,在所述第一持续时间内,第一电流范围内的电流流过第三热元件76,当控制器56在第二持续时间内在一个或多个输出端54产生第二输出电压范围时,在所述第二持续时间内,第二电流范围内的电流流过第三热元件76。第三pcs 68可采用图1所示pcs 10第一实施例的结构或图2所示pcs 10第二实施例的结构。通过gnd1接地,第三热元件与控制器56接地端77形成完整回路,所述接地端可与基板38耦合。

[0036]

可重构晶体管器件36还包括多个第二晶体管叉指78(设置在基板38上方的第四区域80中),其中,所述多个第二晶体管叉指第一组78与第一总线50耦合,所述多个第二晶体管叉指第二组78与第二总线64耦合,所述多个第二晶体管叉指第三组78与第三总线74耦合。在本示例性实施例中,所述多个第二晶体管叉指第一组78包括栅极叉指g5、g6、g7和g8,而所述多个第二晶体管叉指第二组78包括源极叉指s4、s5和s6。可通过gnd2第二接地,将源极叉指s6接地。所述多个第二晶体换叉指第三组78包括漏极叉指d3和d4。

[0037]

源极叉指s3和源极叉指s4是多个第一晶体管叉指40和多个第二晶体管叉指78的相邻源极叉指。第二pcs 58与源极叉指s3和源极叉指s4交叉。在某些实施例中,源极叉指s3和源极叉指s4由第二pcs 58分离,相距40微米-50微米。在其他实施例中,源极叉指s3和源极叉指s4相距30微米-40微米。在其他实施例中,源极叉指s3和源极叉指s4相距20微米-30微米。在其他实施例中,源极叉指s3和源极叉指s4相距1微米-20微米。

[0038]

在某些实施例中,多个第一晶体管叉指40和多个第二晶体管叉指78采用氮化镓技术制成。在某些实施例中,可重构晶体管器件36的开关优值范围为10太赫兹-35太赫兹。在某些实施例中,第一pcs 44、第二pcs 58和第三pcs 68的通态电阻范围均为0.1ω-1.0ω。在其他实施例中,第一pcs 44、第二pcs 58和第三pcs 68的通态电阻范围均为0.1ω-0.5ω。在其他实施例中,第一pcs 44、第二pcs 58和第三pcs 68的通态电阻范围均为0.5ω-1.0ω。在某些实施例中,第一pcs 44、第二pcs 58和第三pcs 68的断态电阻范围均为1000ω-1000000ω。在其他实施例中,第一pcs 44、第二pcs 58和第三pcs 68的断态电阻范围均为1000ω-500000ω。在其他实施例中,第一pcs 44、第二pcs 58和第三pcs 68的断态电阻范围均为500000ω-1000000ω。在某些实施例中,第一pcs 44、第二pcs 58和第三pcs68的断态电容范围均为0.5微微法拉-0.001微微法拉之间。在其他实施例中,第一pcs 44、第二pcs 58和第三pcs 68的断态电容范围均为0.5微微法拉-0.1微微法拉。在其他实施例中,第一pcs 44、第二pcs 58和第三pcs 68的断态电容范围均为0.1微微法拉-0.001微微法拉。

[0039]

图4为可重构晶体管器件的最小噪声系数nfmin与频率(2ghz-12 ghz)图,所述可重构晶体管器件包括四个并联晶体管,每个晶体管均包括用于隔离图3所示可重构晶体管器件36等的pcs开关。当在800微米-200微米的总栅极宽度之间切换时,所述最小噪声系数仅适度下降。

[0040]

图5为显示可重构晶体管器件最优γ的史密斯图,所述可重构晶体管器件包括四个并联晶体管,每个晶体管均包括用于隔离图3所示可重构晶体管器件36等的pcs开关。与非开关隔离晶体管(仅通过打开或关闭晶体管偏置来改变有效栅极宽度)相比,pcs开关所提供的最优γ偏移使可重构晶体管器件的典型隔离技术得到相对重大的改进。

[0041]

图6为可重构晶体管器件的最大增益maxgain与频率范围(2ghz-12 ghz)图,所述可重构晶体管器件包括四个并联晶体管,每个晶体管均包括用于隔离图3所示可重构晶体

管器件等的pcs开关。当在800微米-200微米的总栅极宽度之间切换时,所述最大增益仅适度下降。

[0042]

本领域技术人员应认识到,可对本发明的优选实施例进行改进和修改。所有此类改进和修改均在本文所述概念及所附权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1