一种连接器和印刷线路板总成的制作方法

1.本发明涉及印刷线路板领域,更具体地,特别是指一种连接器和印刷线路板总成。

背景技术:

2.pcb(印刷线路板)设计过程中,高速线部分对于整个板卡的性能影响较大;随着板卡内各种信号速率的增加,对pcb板内的高速走线要求也越来越高。

3.服务器设计中,在机箱大小、客户需求等各方面因素的作用下,对于pcb板卡尺寸,厚度的要求会比较严格,这对于板卡大小,板内走线就会有一定的限制;另一方面,随着cpu(中央处理器)的升级、信号速率的增加,对于高速信号板内布线方面的要求也在增加。目前新平台的cpu对于pcie(计算机和外围设备连接标准扩展)信号有新的要求:高速连接器出pin位置的走线与过孔后的走线不能重叠,即两层的走线不能在同一个方向。但是由于板卡尺寸以及连接器位置是由结构定位的这两方面因素的限制,内层走线向其他方向走是没有空间的。

4.另外连接器两排pin(引脚)之间的距离有限,上排pin的出线如果向下打孔,上排pin的过孔与下排pin之间的距离不满足要求,会造成信号之间的串扰,因此向连接器内打孔也是不允许的。由于板框与连接器位置限制,常规的高速线走线方式都不能满足要求,这种情况在现有技术中也比较常见。此时只能通过使用特殊的制程来解决这个问题:将过孔打在pin上,既能满足过孔到另一排pin脚的距离要求,也能使走线路径顺畅,没有表层内层走线重叠的现象,能满足走线要求。

5.由于板卡常用的为通孔,直接打在pin上的话,后续pin脚上锡会有漏锡现象,因此需要通过pofv工艺用树脂将过孔填平,然后表层进行镀铜,才能使pin脚能满足焊接条件。但pofv工艺制作过程比较复杂,板内的走线线距也要比普通制程的间距要大,对于比较密集的板卡影响较大;另外pofv工艺也会比较贵,同样一张板卡的成本就会提高。

6.针对现有技术中高速信号走线困难、制程大、成本高的问题,目前尚无有效的解决方案。

技术实现要素:

7.有鉴于此,本发明实施例的目的在于提出一种连接器,能够使高速信号正常布线,降低制程,缩减成本。

8.基于上述目的,本发明实施例的第一方面提供了一种连接器,包括:

9.封装主体;

10.引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构与印刷线路板上与两个凸起结构相对应的焊盘对相对设置。

11.在一些实施方式中,连接器包括多个引脚,并且每个引脚的两个凸起结构均处于每个引脚上的相同位置。

12.在一些实施方式中,凹陷结构与印刷线路板上与凹陷结构相对应的高速过孔相对设置。

13.在一些实施方式中,高速过孔位于焊盘对之间。

14.在一些实施方式中,两个凸起结构与焊盘对之间通过焊料电性连接。

15.本发明实施例的第二方面提供了一种印刷线路板总成,包括:

16.印刷线路板;

17.焊盘,成对地设置在印刷线路板上;

18.封装主体;

19.引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构与印刷线路板上与两个凸起结构相对应的焊盘对相对设置。

20.在一些实施方式中,连接器包括多个引脚,并且每个引脚的两个凸起结构均处于每个引脚上的相同位置。

21.在一些实施方式中,凹陷结构与印刷线路板上与凹陷结构相对应的高速过孔相对设置。

22.在一些实施方式中,高速过孔位于焊盘对之间。

23.在一些实施方式中,两个凸起结构与焊盘对之间通过焊料电性连接。

24.本发明具有以下有益技术效果:本发明实施例提供的连接器和印刷线路板总成,通过使用印刷线路板;焊盘,成对地设置在印刷线路板上;封装主体;引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构与印刷线路板上与两个凸起结构相对应的焊盘对相对设置的技术方案,能够使高速信号正常布线,降低制程,缩减成本。

附图说明

25.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

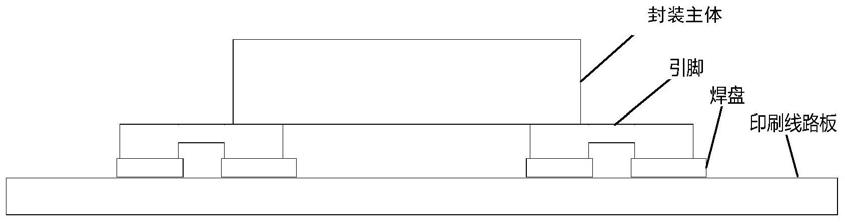

26.图1为本发明提供的连接器的剖面结构图;

27.图2为本发明提供的印刷线路板总成的平面示意图。

具体实施方式

28.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明实施例进一步详细说明。

29.需要说明的是,本发明实施例中所有使用“第一”和“第二”的表述均是为了区分两个相同名称非相同的实体或者非相同的参量,可见“第一”“第二”仅为了表述的方便,不应理解为对本发明实施例的限定,后续实施例对此不再一一说明。

30.基于上述目的,本发明实施例的第一个方面,提出了一种使高速信号正常布线,降低制程,缩减成本的连接器的一个实施例。图1示出的是本发明提供的连接器的第一实施例

的剖面图。

31.所述的连接器,如图1所示包括:

32.封装主体;

33.引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构与印刷线路板上与两个凸起结构相对应的焊盘对相对设置。

34.在一些实施方式中,连接器包括多个引脚,并且每个引脚的两个凸起结构均处于每个引脚上的相同位置。

35.在一些实施方式中,凹陷结构与印刷线路板上与凹陷结构相对应的高速过孔相对设置。

36.在一些实施方式中,高速过孔位于焊盘对之间。

37.在一些实施方式中,两个凸起结构与焊盘对之间通过焊料电性连接。

38.由于目前高速信号速率增加,要求pcb板内的高速走线表层出pin部分的走线与内层的走线不能在同一方向上。常规的连接器引脚在pcb板上的封装为每个pin对应一个长方形的pad(焊盘),焊接之后,连接器引脚整个贴合到pad上。本发明的封装改为一个pin脚对应两个小的长方形pad,参见图1,两个pad之间有一定的间隙。

39.连接器的pin也设计成两端厚中间薄的样子,这样即使中间有过孔,连接器上锡时也不会有漏锡问题。焊接以后,两端厚的pin脚与pcb板上的两个长方形pad贴合,完成上件。

40.此封装的特点在于pcb板上两个小的长方形pad中间可以打高速线过孔,根据不同的布线空间、高速线走向以及连接器位置等各种因素,可以灵活选择过孔与哪边的pad相连,来避免表层走线和内层走线方向重叠,如图2所示(图2中的斜线部分指示焊盘,网格部分指示过孔)。同时过孔也不会对连接器上锡产生影响,不需要额外引入pofv工艺,既能满足信号要求也能节省成本。

41.为生成所需的印刷线路板,本发明首先将连接器封装为一个连接器pin对应两个小的长方形pad,将建好的连接器封装根据结构定位放在pcb板内。然后,综合板内的高速线起始端位置、板型等各种因素规划高速线路径,并根据高速线路径来确定连接器处高速线过孔需要与哪个pad连接才能避免与内层高速线方向重合,完成表层走线。最后,根据layout流程继续后续布线。

42.从上述实施例可以看出,本发明实施例提供的连接器,通过使用印刷线路板;焊盘,成对地设置在印刷线路板上;封装主体;引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构与印刷线路板上与两个凸起结构相对应的焊盘对相对设置的技术方案,能够使高速信号正常布线,降低制程,缩减成本。

43.本发明实施例的第二方面提供了一种印刷线路板总成,包括:

44.印刷线路板;

45.焊盘,成对地设置在印刷线路板上;

46.封装主体;

47.引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构与印刷线路板上与两个凸起结构相对应的

焊盘对相对设置。

48.以上是本发明公开的示例性实施例,但是应当注意,在不背离权利要求限定的本发明实施例公开的范围的前提下,可以进行多种改变和修改。根据这里描述的公开实施例的方法权利要求的功能、步骤和/或动作不需以任何特定顺序执行。此外,尽管本发明实施例公开的元素可以以个体形式描述或要求,但除非明确限制为单数,也可以理解为多个。

49.结合这里的公开所描述的各种示例性逻辑块、模块和电路可以利用被设计成用于执行这里所述功能的下列部件来实现或执行:通用处理器、数字信号处理器(dsp)、专用集成电路(asic)、现场可编程门阵列(fpga)或其它可编程逻辑器件、分立门或晶体管逻辑、分立的硬件组件或者这些部件的任何组合。通用处理器可以是微处理器,但是可替换地,处理器可以是任何传统处理器、控制器、微控制器或状态机。处理器也可以被实现为计算设备的组合,例如,dsp和微处理器的组合、多个微处理器、一个或多个微处理器结合dsp和/或任何其它这种配置。

50.所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本发明实施例公开的范围(包括权利要求)被限于这些例子;在本发明实施例的思路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,并存在如上所述的本发明实施例的不同方面的许多其它变化,为了简明它们没有在细节中提供。因此,凡在本发明实施例的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本发明实施例的保护范围之内。

51.基于上述目的,本发明实施例的第二个方面,提出了一种使高速信号正常布线,降低制程,缩减成本的印刷线路板总成的一个实施例。所述的印刷线路板总成包括:

52.印刷线路板;

53.焊盘,成对地设置在印刷线路板上;

54.封装主体;

55.引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构正对印刷线路板上与两个凸起结构相对应的焊盘对设置。

56.在一些实施方式中,连接器包括多个引脚,并且每个引脚的两个凸起结构均处于每个引脚上的相同位置。

57.在一些实施方式中,凹陷结构正对印刷线路板上与凹陷结构相对应的高速过孔设置。

58.在一些实施方式中,高速过孔位于焊盘对之间。

59.在一些实施方式中,两个凸起结构与焊盘对之间通过焊料电性连接。

60.由于目前高速信号速率增加,要求pcb板内的高速走线表层出pin部分的走线与内层的走线不能在同一方向上。常规的连接器引脚在pcb板上的封装为每个pin对应一个长方形的pad(焊盘),焊接之后,连接器引脚整个贴合到pad上。本发明的封装改为一个pin脚对应两个小的长方形pad,参见图1,两个pad之间有一定的间隙。

61.连接器的pin也设计成两端厚中间薄的样子,这样即使中间有过孔,连接器上锡时也不会有漏锡问题。焊接以后,两端厚的pin脚与pcb板上的两个长方形pad贴合,完成上件。

62.此封装的特点在于pcb板上两个小的长方形pad中间可以打高速线过孔,根据不同

的布线空间、高速线走向以及连接器位置等各种因素,可以灵活选择过孔与哪边的pad相连,来避免表层走线和内层走线方向重叠,如图2所示。同时过孔也不会对连接器上锡产生影响,不需要额外引入pofv工艺,既能满足信号要求也能节省成本。

63.为生成所需的印刷线路板,本发明首先将连接器封装为一个连接器pin对应两个小的长方形pad,将建好的连接器封装根据结构定位放在pcb板内。然后,综合板内的高速线起始端位置、板型等各种因素规划高速线路径,并根据高速线路径来确定连接器处高速线过孔需要与哪个pad连接才能避免与内层高速线方向重合,完成表层走线。最后,根据layout流程继续后续布线。

64.从上述实施例可以看出,本发明实施例提供的印刷线路板总成,通过使用印刷线路板;焊盘,成对地设置在印刷线路板上;封装主体;引脚,电性连接到封装主体,其中引脚包括两端的两个凸起结构和在两个凸起结构之间建立连接的凹陷结构,并且两个凸起结构正对印刷线路板上与两个凸起结构相对应的焊盘对设置的技术方案,能够使高速信号正常布线,降低制程,缩减成本。

65.以上是本发明公开的示例性实施例,但是应当注意,在不背离权利要求限定的本发明实施例公开的范围的前提下,可以进行多种改变和修改。根据这里描述的公开实施例的方法权利要求的功能、步骤和/或动作不需以任何特定顺序执行。此外,尽管本发明实施例公开的元素可以以个体形式描述或要求,但除非明确限制为单数,也可以理解为多个。

66.本领域技术人员还将明白的是,结合这里的公开所描述的各种示例性逻辑块、模块、电路和算法步骤可以被实现为电子硬件、计算机软件或两者的组合。为了清楚地说明硬件和软件的这种可互换性,已经就各种示意性组件、方块、模块、电路和步骤的功能对其进行了一般性的描述。这种功能是被实现为软件还是被实现为硬件取决于具体应用以及施加给整个系统的设计约束。本领域技术人员可以针对每种具体应用以各种方式来实现所述的功能,但是这种实现决定不应被解释为导致脱离本发明实施例公开的范围。

67.应当理解的是,在本文中使用的,除非上下文清楚地支持例外情况,单数形式“一个”旨在也包括复数形式。还应当理解的是,在本文中使用的“和/或”是指包括一个或者一个以上相关联地列出的项目的任意和所有可能组合。上述本发明实施例公开实施例序号仅仅为了描述,不代表实施例的优劣。

68.结合这里的公开所描述的各种示例性逻辑块、模块和电路可以利用被设计成用于执行这里所述功能的下列部件来实现或执行:通用处理器、数字信号处理器(dsp)、专用集成电路(asic)、现场可编程门阵列(fpga)或其它可编程逻辑器件、分立门或晶体管逻辑、分立的硬件组件或者这些部件的任何组合。通用处理器可以是微处理器,但是可替换地,处理器可以是任何传统处理器、控制器、微控制器或状态机。处理器也可以被实现为计算设备的组合,例如,dsp和微处理器的组合、多个微处理器、一个或多个微处理器结合dsp和/或任何其它这种配置。

69.本领域普通技术人员可以理解实现上述实施例的全部或部分步骤可以通过硬件来完成,也可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,上述提到的存储介质可以是只读存储器,磁盘或光盘等。

70.所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本发明实施例公开的范围(包括权利要求)被限于这些例子;在本发明实施例的思

路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,并存在如上所述的本发明实施例的不同方面的许多其它变化,为了简明它们没有在细节中提供。因此,凡在本发明实施例的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本发明实施例的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1