一种晶圆的多层堆叠键合方法与流程

1.本发明属于半导体集成封装技术领域,涉及一种晶圆的多层堆叠键合方法。

背景技术:

2.目前,无论是2.5d tsv硅转接基板集成还是储器芯片的3维tsv堆叠均采用的是单芯片堆叠工艺,组装效率低。晶圆键合是晶圆级芯片尺寸封装(wlcsp)的一种,是将整张晶圆封装测试后再切割成单颗ic芯片。在存储器芯片的3维堆叠或者2.5d tsv硅转接基板集成中采用晶圆级键合工艺将会有效提高组装效率。然而,往往能采用晶圆级键合的tsv硅转接基板或者储器晶圆都属于薄晶圆,其易碎且具有柔性,因此在作业过程中通常需采用临时键合材料将晶圆键合到载体上。带有临时键合材料及载片的晶圆在经历金属键合时会涉及真空以及高低温环境,往往会致使晶圆外围部分区域临时键合胶发生变性,此时将无法顺利将变性区域的载体与晶圆顺利分开,造成碎片。

技术实现要素:

3.本发明的目的在于克服上述现有技术中,采用临时键合材料将晶圆键合到载体上容易导致晶圆碎片的缺点,提供一种晶圆的多层堆叠键合方法及多层晶圆结构。

4.为了达到上述目的,本发明采用以下技术方案予以实现:

5.一种晶圆的多层堆叠键合方法,包括如下步骤:

6.步骤1)选择需要键合的晶圆层数;

7.步骤2)分别对每一层晶圆的正面依次进行再布线和凸点制备;

8.步骤3)将第一层晶圆正面的凸点与第二层晶圆正面的凸点进行金属键合;

9.步骤4)在第二层晶圆的背面依次进行tsv露头、再布线、介质层制备、金属化层制备和背面凸点制备;

10.步骤5)将第二层晶圆的背面凸点与第三层晶圆的正面凸点进行金属键合,之后对第三层晶圆的背面依次进行tsv露头、再布线、介质层制备、金属化层制备和背面凸点制备;

11.步骤6)依据需要键合的晶圆层数,按照步骤4)和步骤5)的操作制备后续晶圆层数,即除第一层和第二层外,剩余晶圆层中的相邻两个晶圆层,前一晶圆的背面凸点和后一晶圆的正面凸点进行金属键合,之后对后一晶圆的背面依次进行tsv露头、再布线、介质层制备、金属化层制备和背面凸点制备,直至完成晶圆的多层堆叠键合。

12.优选地,凸点制备时,凸点为cu凸点、au凸点或snag凸点;

13.金属键合时,当cu凸点和cu凸点键合时,键合温度为380~450℃,键合时间为60~90min,键合压强为10~30mpa;

14.当cu凸点和snag凸点键合时,键合温度为240~280℃;键合时间为15~60min,键合压强为0.1~10mpa;

15.当au凸点和au凸点键合时,键合温度为300~400℃,键合时间为30min~90min,键合压强为10~30mpa。

16.优选地,tsv露头包括依次对晶圆进行背面减薄、刻蚀和化学机械抛光。

17.优选地,tsv露头后,tsv的直径为5~30μm,tsv的深度为50~400μm。

18.优选地,再布线具体操作为依次进行光刻、电镀和湿法刻蚀;

19.再布线层数为1~4层。

20.优选地,光刻具体是对晶圆依次进行涂胶、曝光和显影;

21.光刻胶的涂覆厚度为5~35μm。

22.优选地,介质层为pi胶、氧化硅、氮化硅或碳化硅;

23.当介质层为pi胶时,pi胶的厚度为5~30μm。

24.优选地,步骤4~步骤6)中,金属化层制备的具体操作为:在介质层的上表面,从下至上依次制备粘附层、阻挡层和润湿层;

25.粘附层为cr、ti、ti-w或v;阻挡层为ti、ni、cu、pd、pt或ti-w;润湿层为cu、ni、pd或au;

26.粘附层的厚度为0.1~0.5μm,阻挡层的厚度为0.1~2μm,润湿层的厚度为0.5~5μm。

27.优选地,步骤5)中,相邻两个晶圆键合时,前一层晶圆的正面凸点材料与后一层晶圆的背面凸点材料一致。

28.与现有技术相比,本发明具有以下有益效果:

29.本发明公开了一种晶圆的多层堆叠键合方法,通过以下键合顺序的提出:第一层、第二层晶圆正面工艺-第一层、第二层晶圆键合-一侧晶圆减薄及背面工艺-另一侧晶圆减薄及背面工艺-第三层晶圆正面工艺及第二层与第三层晶圆键合-第三层晶圆减薄及背面工艺,为薄晶圆的多层键合提出了解决方案。本发明方法不需要额外增加载片就能进行多层晶圆的键合,根据键合晶圆自身相互的承载作用,逐层增加键合晶圆的层数,规避了因临时键合胶变性难解开而裂片的风险。此外,对比单芯片堆叠,本发明方法显著提高了组装效率。本发明方法是一种高效的多层晶圆级同质或异质高密度集成方法,应用前景和市场潜力非常广阔,具有重要的战略意义和社会效益。

附图说明

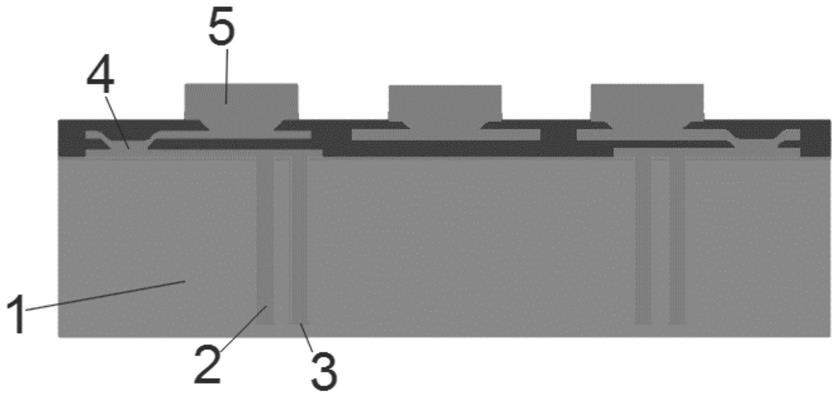

30.图1为带tsv结构的第二、第三、第四、第五层晶圆正面工艺结束后的结构;

31.图2为不带tsv结构的第一层晶圆正面工艺结束后的结构;

32.图3通过cu-sn金属键合工艺完成第一层晶圆正面与第二层晶圆正面的凸点键合;

33.图4为第二层晶圆背面tsv露头、再布线以及凸点制备后的2层晶圆键合结构;

34.图5为三层晶圆键合后的结构图;

35.图6为多层(≥5)晶圆键合后结构示意图;

36.图7为本发明方法的工艺流程图。

37.其中:1-硅衬底;2-tsv;3-钝化层;4-rdl;5-铜柱;6-凸点。

具体实施方式

38.下面结合附图对本发明做进一步详细描述:

39.实施例1

40.在本实施例中所用晶圆为4m异步sram(静态存储器)晶圆,最终为3层sram晶圆键合产品,如图5所示。3层sram晶圆键合方法包括以下步骤:过程如图7所示,

41.步骤1、第一层晶圆仅在正面进行再布线及凸点制备,将pad引出,正面再布线为3层,凸点为电镀snag,高度3μm;

42.第二层晶圆和第三层晶圆首先完成正面再布线及凸点制备,再布线层数为3层,正面凸点为电镀cu,高度5μm;

43.步骤2、第一层晶圆正面snag凸点与第二层晶圆正面cu凸点进行金属键合,键合温度260℃,时间30min,凸点开口率为1.5%,键合压力为5000n;通过cu-sn金属键合工艺完成第一层晶圆正面与第二层晶圆正面的凸点键合,结构如图3所示。键合压力根据凸点有效焊接面积大小或凸点开口率而定。

44.步骤3、第二层晶圆背面进行tsv露头,(tsv露头具体为依次进行背面减薄-刻蚀-cmp),tsv直径为30μm,深度为150μm;

45.步骤4、对第二层tsv露头后的晶圆背面进行再布线层制备,即依次通过光刻(光刻具体为依次进行涂胶、曝光和显影)、电镀、湿法刻蚀完成再布线层制备,再布线层层数为3层,电镀的是铜线条,光刻胶型号为azp4620,光刻胶的旋涂厚度为10μm,湿法刻蚀后线条厚度为5μm;

46.步骤5、第二层晶圆背面的介质层制备,介质层为pi胶,型号为jsr5100,介质层的厚度为5μm;

47.第二层晶圆背面的金属化层制备,金属化层从下至上依次包括粘附层、阻挡层和润湿层,金属化层中,粘附层为0.3μm的cr,阻挡层为0.1μm的ti,润湿层为0.5μm的pd;

48.步骤6、第二层晶圆背面凸点制备,凸点为电镀snag,高度3μm;结构如图4所示;

49.步骤7、第二层晶圆背面snag凸点与第三层晶圆正面cu凸点进行金属键合,键合温度280℃,时间20min,凸点开口率为5%,键合压力为10kn;

50.步骤8、与步骤4和步骤5类似,完成第三层晶圆背面再布线层、介质层、ubm层(金属化层),金属化层从下至上依次包括粘附层、阻挡层和润湿层,粘附层为0.2μm的ti,阻挡层为1.5μm的ti,润湿层为3μm的cu;最后再进行第三层晶圆背面凸点制备,凸点为电镀cu,高度为5μm;最终晶圆结构如图5所示。

51.实施例2

52.除以下内容外,其余内容同实施例1。

53.tsv直径为5μm,深度为50μm;

54.键合温度240℃,键合时间60min,凸点开口率为3.5%,键合压力为6000n;

55.正面再布线为2层,背面再布线层数为4层。

56.步骤5中,第二层晶圆背面的金属化层中,粘附层为0.5μm的ti,阻挡层为1μm的cu,润湿层为2μm的ni;

57.步骤8中,第三层晶圆背面的金属化层中,粘附层为0.1μm的ti,阻挡层为2μm的cu,润湿层为5μm的cu;

58.实施例3

59.在本实施例中所用晶圆为4m异步sram(静态存储器)晶圆,最终为5层sram晶圆键合产品,如图6所示,制备流程如图7所示。

60.步骤1、第一层晶圆仅在正面进行再布线及凸点制备,将pad引出,正面再布线为2层,凸点为电镀cu,高度3μm;

61.第二层晶圆和第三层晶圆首先完成正面再布线及凸点制备,再布线层数为3层,正面凸点为电镀cu,高度5μm;

62.步骤2、第一层晶圆正面cu凸点与第二层晶圆正面cu凸点进行金属键合,键合温度400℃,键合时间90min,凸点开口率为2%,键合压力为20kn;通过cu-cu金属键合工艺完成第一层晶圆正面与第二层晶圆正面的凸点键合,结构如图3所示。键合压力根据凸点有效焊接面积大小或凸点开口率而定。

63.步骤3、第二层晶圆背面进行tsv露头,(tsv露头具体为依次进行背面减薄-刻蚀-cmp),tsv直径为15μm,深度为200μm;

64.步骤4、对第二层tsv露头后的晶圆背面进行再布线层制备,即依次通过光刻(光刻具体为依次进行涂胶、曝光和显影)、电镀、湿法刻蚀完成再布线层制备,再布线层层数为3层,电镀的是铜线条,光刻胶型号为azp4620,光刻胶的旋涂厚度为10μm,湿法刻蚀后线条厚度为5μm;

65.步骤5、第二层晶圆背面的介质层制备,介质层为pi胶,型号为jsr5100,介质层的厚度为5μm;

66.第二层晶圆背面的金属化层制备,金属化层从下至上依次包括粘附层、阻挡层和润湿层,金属化层中,粘附层为0.1μm的ti-w,阻挡层为0.4μm的pd,润湿层为2μm的au;

67.步骤6、第二层晶圆背面凸点制备,凸点为电镀cu,高度3μm;

68.步骤7、第二层晶圆背面cu凸点与第三层晶圆正面cu凸点进行金属键合,键合温度450℃,时间60min,凸点开口率为5%,键合压力为10kn;

69.步骤8、与步骤4和步骤5类似,完成第三层晶圆背面再布线层、介质层、ubm层(金属化层),金属化层从下至上依次包括粘附层、阻挡层和润湿层,粘附层为0.4μm的v,阻挡层为2μm的pt,润湿层为4μm的ni;再进行第三层晶圆背面凸点制备,凸点为电镀cu,高度为5μm;

70.步骤9、与步骤4~8类似,完成第四层和第五层晶圆背面再布线层、介质层、ubm层(金属化层),金属化层从下至上依次包括粘附层、阻挡层和润湿层,粘附层为0.25μm的cr,阻挡层为0.3μm的ni,润湿层为1.5μm的ni;再进行第五层晶圆背面凸点制备,凸点为电镀cu,高度为5μm。

71.实施例4

72.除以下内容外,其余内容同实施例3。

73.步骤2)中,键合温度380℃,键合时间80min,凸点开口率为2%,键合压力为20kn。

74.实施例5

75.除以下内容外,其余内容与实施例1相同。

76.凸点均为电镀au;

77.步骤2)中,au-au键合的条件为:键合温度350℃,键合时间40min,凸点开口率为1.5%,键合压力为10kn;

78.步骤7)中,au-au键合的条件为:键合温度400℃,键合时间30min,凸点开口率为2%,键合压力为25kn。

79.实施例6

80.除以下内容外,其余内容同实施例5。

81.步骤2)中,au-au键合的条件为:键合温度300℃,键合时间90min,凸点开口率为1.5%,键合压力为30kn。

82.需要说明的是,上述实施例中光刻胶的型号为azp4620(该胶为正性光刻胶)或其它类型的正性光刻胶和负性光刻胶。金属化层也可以为其它可达到粘附作用、阻挡作用和润湿作用的材料,如粘附层可为cr,ti,ti-w,v等;阻挡层可为ti,ni,cu,pd,pt,ti-w等;润湿层可为cu,ni,pd等。

83.综上所述,本发明方法无须额外增加临时键合载片,通过键合晶圆相互承载作用逐层键合的晶圆键合方法:第一层、第二层晶圆正面工艺-第一层、第二层晶圆键合-一侧晶圆减薄及背面工艺-另一侧晶圆减薄及背面工艺-第三层晶圆正面工艺及第二层与第三层晶圆键合-第三层晶圆减薄及背面工艺。本发明针对单芯片堆叠键合存在的效率低、晶圆级堆叠键合带载片易破坏晶圆完整性的问题,创新性的提出一种多层薄晶圆键合方法,通过以下键合顺序的提出:第一层、第二层晶圆正面工艺-第一层、第二层晶圆键合-一侧晶圆减薄及背面工艺-另一侧晶圆减薄及背面工艺-第三层晶圆正面工艺及第二层与第三层晶圆键合-第三层晶圆减薄及背面工艺

……

,为薄晶圆的多层键合提出了解决方案。

84.以上内容仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明权利要求书的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1