光电二极管阵列检测器的制作方法

1.本实用新型涉及半导体功率器件,特别涉及一种光电二极管阵列检测器。

背景技术:

2.纺织机纺织加工过程中的对象是各种纤维或纱线,属于柔性物体,其受外力作用后容易变形。因此纺织机的发展倾向于使用非接触式测量来检测加工过程中的参量的变化,例如光电检测。光电检测对灵敏度有较高的要求,需要对光电二极管阵列检测器的布局进行大量的设计工作,申请人在前期设计了一种变长度条形单元阵列的光电二极管阵列检测器,具有较好的稳定性,但在不同产品的应用过程中发现,在暗光下其存在灵敏度降低的问题。

技术实现要素:

3.本实用新型的目的在于提供增强光灵敏性的光电二极管阵列检测器。

4.为实现上述技术目的,本实用新型采用如下技术方案:

5.一种光电二极管阵列检测器,包括并行排列的奇数个条形光电二极管,其中单个光电二极管组成为:低掺杂的n型半导体基底上沉积高掺杂p型半导体,高掺杂p型半导体外环相隔一段距离沉积高掺杂n型半导体;所述高掺杂p型半导体的上贴附二氧化硅薄膜;所述奇数个条形光电二极管从中间到两边与光电二极管阵列检测器底边夹角依次减小,变化范围为 90

°

~76.5

°

。

6.作为本实用新型的进一步改进,相邻条形光电二极管夹角的差值呈等差数列。

7.作为本实用新型的进一步改进,所述光电二极管阵列检测器呈轴对称结构。

8.作为本实用新型的进一步改进,所述低掺杂的n型半导体、高掺杂p型半导体、高掺杂 n型半导体上铺设金属电极层,金属电极层在高掺杂p型半导体近外环处设有第一断层;金属电极层在高掺杂p型半导体中部设有第二断层。

9.作为本实用新型的进一步改进,所述二氧化硅薄膜贴附于第二断层处。

10.作为本实用新型的进一步改进,所述第一断层内沉积碳纳米层。

11.作为本实用新型的进一步改进,所述碳纳米层向外环延伸至接触高掺杂n型半导体。

12.作为本实用新型的进一步改进,所述金属电极层为al。

13.本实用新型的光电二极管阵列检测器增加了高掺杂p型半导体的受光面,利用二氧化硅收光膜增强其光响应,并调整了条形光电二极管的布局使其总长度增加,相对增加了受光面积,使其在维持原有电气性能的基础上增强了暗光下的灵敏性。

附图说明

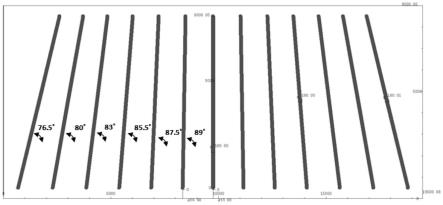

14.图1为光电二极管阵列检测器平面结构示意图。

15.图2为图1a处断面结构示意图。

16.图3为高掺杂p型半导体平面结构示意图。

具体实施方式

17.如图1~3所示的光电二极管阵列检测器,包括并行排列的奇数个条形光电二极管,其中单个光电二极管组成为:低掺杂的n型半导体基底1上沉积高掺杂p型半导体2,高掺杂p型半导体2外环相隔一段距离沉积高掺杂n型半导体3;所述高掺杂p型半导体2的上贴附二氧化硅薄膜7;所述奇数个条形光电二极管从中间到两边与光电二极管阵列检测器底边夹角依次减小,变化范围为90

°

~76.5

°

。

18.进一步的,光电二极管阵列检测器呈轴对称结构,相邻条形光电二极管夹角的差值呈等差数列。如图3所示,13个条形光电二极管与底边的夹角从左到右依次为76.5

°

,80

°

,83

°

, 85.5

°

,87.5

°

,89

°

,90

°

,89

°

,87.5

°

,85.5

°

,83

°

,80

°

,76.5

°

,差值从两边向中间依次为3.5

°

,3

°

,2.5

°

,2

°

,1.5

°

,1

°

,呈等差数列。

19.低掺杂的n型半导体1、高掺杂p型半导体2、高掺杂n型半导体3上铺设金属电极层6,金属电极层6在高掺杂p型半导体1近外环处设有第一断层,第一断层内沉积碳纳米层5,碳纳米层5向外环延伸至接触高掺杂n型半导体3。金属电极层6在高掺杂p型半导体2中部设有第二断层,二氧化硅薄膜7贴附于第二断层处。

20.本实施例中,金属电极层6为al。

21.本实施例的光电二极管阵列检测器反向击穿电压bvr=50v,暗电流id=5na,正向压降 vf=1v,光谱响应范围430~1100nm。

技术特征:

1.一种光电二极管阵列检测器,包括并行排列的奇数个条形光电二极管,其中单个光电二极管组成为:低掺杂的n型半导体基底上沉积高掺杂p型半导体,高掺杂p型半导体外环相隔一段距离沉积高掺杂n型半导体;其特征在于,所述高掺杂p型半导体的上贴附二氧化硅薄膜;所述奇数个条形光电二极管从中间到两边与光电二极管阵列检测器底边夹角依次减小,变化范围为90

°

~76.5

°

。2.根据权利要求1所述的一种光电二极管阵列检测器,其特征在于,相邻条形光电二极管夹角的差值呈等差数列。3.根据权利要求1所述的光电二极管阵列检测器,其特征在于,所述光电二极管阵列检测器呈轴对称结构。4.根据权利要求1所述的光电二极管阵列检测器,其特征在于,所述低掺杂的n型半导体、高掺杂p型半导体、高掺杂n型半导体上铺设金属电极层,金属电极层在高掺杂p型半导体近外环处设有第一断层;金属电极层在高掺杂p型半导体中部设有第二断层。5.根据权利要求4所述的光电二极管阵列检测器,其特征在于,所述二氧化硅薄膜贴附于第二断层处。6.根据权利要求4所述的光电二极管阵列检测器,其特征在于,所述第一断层内沉积碳纳米层。7.根据权利要求6所述的光电二极管阵列检测器,其特征在于,所述碳纳米层向外环延伸至接触高掺杂n型半导体。8.根据权利要求4所述的光电二极管阵列检测器,其特征在于,所述金属电极层为al。

技术总结

本实用新型涉及光电二极管阵列检测器,包括并行排列的奇数个条形光电二极管,其中单个光电二极管组成为:低掺杂的N型半导体基底上沉积高掺杂P型半导体,高掺杂P型半导体外环相隔一段距离沉积高掺杂N型半导体;所述高掺杂P型半导体的上贴附二氧化硅薄膜;所述奇数个条形光电二极管从中间到两边与光电二极管阵列检测器底边夹角依次减小,变化范围为90

技术研发人员:崔峰敏

受保护的技术使用者:傲迪特半导体(南京)有限公司

技术研发日:2021.12.31

技术公布日:2022/7/25

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1