一种异质结电池及其制备方法与流程

1.本发明涉及光伏电池技术领域,具体涉及一种异质结电池及其制备方法。

背景技术:

2.异质结电池综合了晶体硅电池与薄膜电池的优势,具有结构简单、工艺温度低、钝化效果好、开路电压高、温度特性好、双面发电等优点,是高转换效率硅基太阳能电池的热点方向之一。然而,现有异质结电池中的非晶硅虽然钝化效果好,但是由于寄生光吸收和导电性差,成为制约异质结电池的转换效率提高的因素。

3.因此,现有异质结电池的制备方法有待改进。

技术实现要素:

4.本发明要解决的技术问题在于,克服现有技术中的异质结电池因寄生光吸收和导电性差,难以提高异质结电池的转换效率的问题。

5.为了解决上述技术问题,本发明提供一种异质结电池的制备方法,包括:提供半导体衬底层;在所述半导体衬底层的至少一侧表面形成隧穿介质膜,所述隧穿介质膜中具有若干微孔;在所述隧穿介质膜背离所述半导体衬底层的一侧表面形成掺杂半导体层。

6.可选的,形成所述隧穿介质膜的步骤包括:在所述半导体衬底层的至少一侧表面形成初始介质膜;对所述初始介质膜进行退火处理,使初始介质膜形成所述隧穿介质膜。

7.可选的,形成所述初始介质膜的工艺包括氧化工艺,所述氧化工艺在热氧炉中进行。

8.可选的,所述氧化工艺的参数包括:采用的气体包括氧气,氧气的浓度为1slm-1000slm,温度为650℃-970℃,氧化时间为5分钟-180分钟。

9.可选的,在所述氧化工艺中,采用的温度为800℃,氧化时间为35分钟。

10.可选的,所述退火处理的参数包括:温度为600℃-950℃,时间为1分钟-80分钟。

11.可选的,在所述退火处理中,采用的温度为750℃,退火时间为40分钟。

12.可选的,所述隧穿介质膜的厚度为1nm-10nm。

13.可选的,所述隧穿介质膜的材料包括氧化硅。

14.可选的,所述微孔的直径为1nm-500nm。

15.可选的,所述微孔均匀分布。

16.可选的,所述微孔的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比为1%-30%。

17.可选的,在所述半导体衬底层的至少一侧表面形成隧穿介质膜的步骤包括:在所述半导体衬底层的一侧表面形成第一隧穿介质膜;在所述半导体衬底层的另一侧表面形成第二隧穿介质膜;在所述隧穿介质膜背离所述半导体衬底层的一侧表面掺杂半导体层的步骤包括:在所述第一隧穿介质膜背离所述半导体衬底层的一侧表面形成第一掺杂半导体层;在所述第二隧穿介质膜背离所述半导体衬底层的一侧表面形成第二掺杂半导体层。

18.可选的,所述第一掺杂半导体层的厚度为5nm-15nm;所述第二掺杂半导体层的厚度为5nm-15nm。

19.可选的,所述第一掺杂半导体层的导电类型为p型,形成所述第一掺杂半导体层的工艺为等离子体化学气相沉积工艺,形成所述第一掺杂半导体层的参数包括:采用的气体包括硅烷、氢气和乙硼烷,硅烷的流量为1sccm-10000sccm,氢气的流量为0.1slm-50slm,乙硼烷的流量为1sccm-8000sccm,腔室压强为1mbar-1000mbar,温度为50℃-300℃。

20.可选的,所述第二掺杂半导体层的导电类型为n型,形成所述第二掺杂半导体层的工艺为等离子体化学气相沉积工艺,形成所述第二掺杂半导体层的参数包括:采用的气体包括硅烷、氢气和磷烷,硅烷的流量为1sccm-10000sccm,氢气的流量为0.1slm-50slm,磷烷的流量为1sccm-8000sccm,腔室压强为1mbar-1000mbar,温度为50℃-300℃。

21.可选的,还包括:在所述掺杂半导体层背离所述半导体衬底层的一侧形成栅线;形成所述栅线之后,进行光注入退火处理,所述光注入退火处理包括依次进行的第一温区光注入退火处理至第n温区光注入退火处理,n为大于或等于1的整数;第一温区光注入退火处理至第n温区光注入退火处理的温度为100℃-250℃。

22.可选的,n为等于或大于8的整数,第一温区退火处理至第三温区退火处理的温度为138℃-142℃,第四温区退火处理至第六温区退火处理的温度为155℃-175℃,第六温区退火处理至第n温区退火处理的温度为145℃-155℃。

23.本发明还提供一种异质结电池,包括半导体衬底层;位于所述半导体衬底层至少一侧表面的隧穿介质膜,所述隧穿介质膜中具有若干微孔;位于所述隧穿介质膜背离所述半导体衬底层的一侧表面的掺杂半导体层。

24.可选的,所述隧穿介质膜的厚度为1nm-10nm。

25.可选的,所述隧穿介质膜的材料包括氧化硅。

26.可选的,所述微孔的直径为1nm-500nm。

27.可选的,所述微孔的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比为1%-30%。

28.可选的,所述隧穿介质膜包括:位于所述半导体衬底层的一侧表面的第一隧穿介质膜;位于所述半导体衬底层的另一侧表面的第二隧穿介质膜;所述掺杂半导体层包括:位于所述第一隧穿介质膜背离所述半导体衬底层的一侧表面的第一掺杂半导体层;位于所述第二隧穿介质膜背离所述半导体衬底层的一侧表面的第二掺杂半导体层。

29.可选的,所述第一掺杂半导体层的厚度为5nm-15nm;所述第二掺杂半导体层的厚度为5nm-15nm。

30.本发明技术方案,具有如下优点:

31.本发明提供的异质结电池的制备方法,在所述半导体衬底层的至少一侧表面形成隧穿介质膜,所述隧穿介质膜可以钝化所述半导体衬底层,从而提高开路电压;所述隧穿介质膜中具有若干微孔,所述隧穿介质膜具有隧穿特性,能使得载流子隧穿过所述隧穿介质膜,其次,所述隧穿介质膜中的微孔能提供载流子迁移的通道,这样提高了载流子的运输能力,从而提高短路电流,提高所述异质结电池的导电性;所述隧穿介质膜替换现有技术中的异质结电池的非晶硅本征层,相比于本征非晶硅,隧穿介质膜的寄生光吸收很小,会促进更多的光进入基体,有利于提高短路电流,因此提高了异质结电池的转换效率。

附图说明

32.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

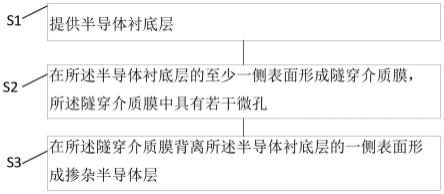

33.图1本发明一实施例提供的异质结电池的制备方法的流程图;

34.图2至图5为本发明一实施例提供的异质结电池制备过程的结构示意图。

35.附图标识中:

36.1-半导体衬底层,2-微孔,201-第一隧穿介质膜,202-第二隧穿介质膜,301-第一掺杂半导体层,302-第二掺杂半导体层,401-第一透明导电膜,402-第二透明导电膜。

具体实施方式

37.下面将结合附图对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.在本发明的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

39.此外,下面所描述的本发明不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

40.本实施例提供一种异质结电池的制备方法,参考图1,包括以下步骤:

41.s1:提供半导体衬底层;

42.s2:在所述半导体衬底层的至少一侧表面形成隧穿介质膜,所述隧穿介质膜中具有若干微孔;

43.s3:在所述隧穿介质膜背离所述半导体衬底层的一侧表面形成掺杂半导体层。

44.下面参考图2至图5对该异质结电池的制备方法进行详细的介绍。

45.参考图2,提供半导体衬底层1。

46.本实施例中,以所述半导体衬底层1为硅衬底作为示例,具体的可以为单晶硅衬底。在其他实施例中,所述半导体衬底层还可以选择其他半导体材料。

47.所述制备方法还包括使所述半导体衬底层1的两侧表面形成绒面,所述绒面为低反射率的金字塔绒面,形成绒面之后进行清洗处理,清洗处理使用的清洗液包括koh溶液,koh溶液的浓度为1%-10%,清洗时间范围为1min-60min,清洗温度范围为5℃-80℃。

48.参考图3,在所述半导体衬底层1的至少一侧表面形成隧穿介质膜,所述隧穿介质膜中具有若干微孔2。

49.具体的,对绒面进行清洗处理之后,形成隧穿介质膜。

50.所述隧穿就是在量子力学的观点下的隧穿,也就是当隧穿介质膜的厚度小于一定厚度时候,载流子能穿过微孔2之间的隧穿介质膜,隧穿介质膜的势能大于粒子的总能量。

形成所述隧穿介质膜的步骤包括:在所述半导体衬底层1的至少一侧表面形成初始介质膜;对所述初始介质膜进行退火处理,使初始介质膜形成所述隧穿介质膜。

51.形成所述隧穿介质膜的工艺包括氧化工艺,所述氧化工艺在热氧炉中进行。

52.在一个实施例中,所述氧化工艺的参数包括:采用的气体包括氧气,氧气的浓度为1slm-1000slm,例如500slm;温度为650℃-970℃,例如700℃;氧化时间为5分钟-180分钟,例如30分钟。

53.所述氧化工艺中,若氧气的浓度低于1slm,则氧化所述半导体衬底层的速率过于慢;若氧气的浓度高于1000slm,则氧化速率过快导致难以控制氧化所述半导体衬底层的速率。

54.所述氧化工艺中,若温度低于650℃,则氧化所述半导体衬底层的速率过于慢;若温度高于970℃,则氧化速率过快导致难以控制氧化所述半导体衬底层的速率。

55.所述氧化工艺中,若氧化时间低于5分钟,则氧化所述半导体衬底层不充分,初始介质膜的厚度均一性较差;若氧化时间高于180分钟,则会过度氧化所述半导体衬底层,导致形成的初始介质膜过厚,不利于在后续退火处理中形成微孔。

56.在一个实施例中,在所述氧化工艺中,采用的温度为800℃,氧化时间为35分钟。

57.本实施例中,所述氧化工艺使在所述半导体衬底层的至少一侧表面形成初始介质膜,具体的,所述初始介质膜为氧化膜,当所述半导体衬底层的材料为硅,所述初始介质膜的材料为氧化硅。在其他实施例中,所述初始介质膜的材料还可以是能提供一定钝化效果的其他氧化物材料。

58.在进行所述氧化工艺之后,还包括:对所述初始介质膜进行退火处理,使初始介质膜形成所述隧穿介质膜。所述退火处理的目的是使所述初始介质膜转化为具有微孔2的隧穿介质膜。

59.在一个实施例中,所述退火处理在热氧炉中进行,进一步的,所述退火处理和所述氧化工艺在同一个热氧炉中进行,这样可以简化工艺;当然也可以分开在不同的热氧炉中进行。

60.在另一个实施例中,所述退火处理在高温炉内进行。

61.在一个实施例中,所述退火处理的参数包括:温度为600℃-950℃,例如800℃;时间为1分钟-80分钟,例如50分钟。

62.在所述退火处理中,若温度低于600℃,则形成微孔的直径较小,导致载流子隧穿所述隧穿介质膜的效果不明显;若温度高于950℃,则形成的微孔的直径过大,导致所述隧穿介质膜钝化所述半导体衬底层的效果不明显,进而提高开路电压的效果不明显。

63.在所述退火处理中,若时间低于1分钟,则形成微孔的直径较小,导致载流子隧穿所述隧穿介质膜的效果不明显;若时间超过80分钟,则形成的微孔的直径过大,导致所述隧穿介质膜钝化所述半导体衬底层的效果不明显,进而提高开路电压的效果不明显。

64.在一个具体的实施例中,在所述退火工艺中,采用的温度为750℃,退火时间为40分钟。

65.所述隧穿介质膜用于对半导体衬底层的表面进行钝化,减少半导体衬底层表面的缺陷。所述隧穿介质膜替换现有技术中的异质结电池的非晶硅本征层,相比于本征非晶硅,所述隧穿介质膜的寄生光吸收降低了1%-30%,促进了更多的光进入基体,使短路电流提

高了1%-10%。

66.在一个实施例中,所述隧穿介质膜的厚度为1nm-10nm,例如5nm;若所述隧穿介质膜的厚度小于1nm,形成所述异质结电池的转换效率低于0.05%,则所述隧穿介质膜钝化所述半导体衬底层的效果不明显;若所述隧穿介质膜的厚度大于10nm,形成所述异质结电池的转换效率低于0.05%,则会导致载流子隧穿所述隧穿介质膜的效果不明显。

67.本实施例中,所述隧穿介质膜的材料包括氧化硅,在其他实施例中,所述隧穿介质膜的材料还可以是其他材料。

68.所述隧穿介质膜不仅可以钝化所述半导体衬底层的表面,而且所述隧穿介质膜中的微孔可以使载流子在传输过程中不存在阻碍有利于载流子更好的传输。

69.在一个实施例中,所述微孔2的直径大小为1nm-500nm,例如200nm,所述微孔2使载流子传输的效果更好。若所述微孔的直径小于1nm,则会导致载流子运输效果不明显,进而导致提高短路电流效果不明显;若所述微孔的直径大于500nm,则会导致所述隧穿介质膜钝化所述半导体衬底层效果不明显,进而导致提高开路电压效果不明显。

70.在一个实施例中,所述微孔均匀分布,所述微孔均匀分布可以使载流子传输的效果更好;在其他实施例中,所述微孔不均匀分布。

71.在一个实施例中,所述微孔2的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比为1%-30%,若所述微孔的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比小于1%,则会导致载流子运输效果不明显进而提高短路电流效果不明显;若所述微孔的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比大于30%,则会导致所述隧穿介质膜钝化所述半导体衬底层效果不明显而提高开路电压效果不明显。

72.继续参考图3,在所述半导体衬底层1的至少一侧表面形成隧穿介质膜的步骤包括:在所述半导体衬底层1的一侧表面形成第一隧穿介质膜201;在所述半导体衬底层1的另一侧表面形成第二隧穿介质膜202。

73.具体的,所述第一隧穿介质膜201的厚度为1nm-10nm,例如5nm;若所述第一隧穿介质膜201的厚度小于1nm,则所述隧穿介质膜钝化所述半导体衬底层的效果不明显;若所述第一隧穿介质膜201的厚度大于10nm,则会导致载流子隧穿所述隧穿介质膜的效果不明显。

74.本实施例中,所述第一隧穿介质膜201的材料包括氧化硅,在其他实施例中,所述第一隧穿介质膜的材料还可以是其他材料。

75.具体的,所述第二隧穿介质膜202的厚度为1nm-10nm,例如5nm;若所述第二隧穿介质膜202的厚度小于1nm,则所述隧穿介质膜钝化所述半导体衬底层的效果不明显;若所述第二隧穿介质膜202的厚度大于10nm,则会导致载流子隧穿所述隧穿介质膜的效果不明显。

76.本实施例中,所述第二隧穿介质膜202的材料包括氧化硅,在其他实施例中,所述第二隧穿介质膜的材料还可以是其他材料。

77.参考图4,在所述隧穿介质膜背离所述半导体衬底层的一侧表面掺杂半导体层,形成所述掺杂半导体层的步骤包括:在所述第一隧穿介质膜背离所述半导体衬底层的一侧表面形成第一掺杂半导体层301;在所述第二隧穿介质膜背离所述半导体衬底层的一侧表面形成第二掺杂半导体层302。

78.在一个实施例中,所述第一掺杂半导体层301的厚度为5nm-15nm,例如10nm;所述第二掺杂半导体层302的厚度为5nm-15nm,例如3nm。

79.在一个实施例中,所述第一掺杂半导体层301的导电类型为p型,形成所述第一掺杂半导体层301的工艺为等离子体化学气相沉积工艺,形成所述第一掺杂半导体层301的参数包括:采用的气体包括硅烷、氢气和乙硼烷,硅烷的流量为1sccm-10000sccm,氢气的流量为0.1slm-50slm,乙硼烷的流量为1sccm-8000sccm,腔室压强为1mbar-1000mbar,温度为50℃-300℃。

80.在一个具体的实施例中,氢气与硅烷的流量比为1:50;在其他实施例中,所述氢气与硅烷的流量比还可以是其他数值。

81.在一个实施例中,乙硼烷的流量可根据具体的掺杂要求设定。在一个实施例中,所述第二掺杂半导体层302的导电类型为n型,形成所述第二掺杂半导体层302的工艺为等离子体化学气相沉积工艺,形成所述第二掺杂半导体层302的参数包括:采用的气体包括硅烷、氢气和磷烷,硅烷的流量为1sccm-10000sccm,氢气的流量为0.1slm-50slm,磷烷的流量为1sccm-8000sccm,腔室压强为1mbar-1000mbar,温度为50℃-300℃。在一个实施例中,只在所述半导体衬底的一侧形成一层隧穿介质膜,所述隧穿介质膜位于所述第一掺杂半导体层朝向所述半导体衬底的一侧,所述第一掺杂半导体层导电类型为p型,所述隧穿介质膜位于异质结电池的pn结面时,载流子的的运输效果更好。

82.在一个实施例中,只在所述半导体衬底的一侧形成一层隧穿介质膜,所述隧穿介质膜位于所述第二掺杂半导体层朝向所述半导体衬底的一侧,所述第二掺杂半导体层导电类型为n型。

83.参考图5,在所述第一掺杂半导体层301背离所述半导体衬底层1的一侧形成第一透明导电膜401,在所述第二掺杂半导体层302背离所述半导体衬底层1的一侧形成第二透明导电膜402,形成所述第一透明导电膜401和所述第二透明导电膜402的工艺包括等物理气相沉积工艺,所述第一透明导电膜401的厚度为100nm-150nm,所述第二透明导电膜402的厚度为100nm-150nm。

84.所述制备方法还包括:形成第一透明导电膜401和所述第二透明导电膜402之后,在所述掺杂半导体层背离所述半导体衬底层1的一侧形成栅线(图中未示出)。

85.具体的,在所述第一透明导电膜401背离所述半导体衬底层1的一侧形成第一栅线;在所述第二透明导电膜402背离所述半导体衬底层1的一侧形成第二栅线。

86.在一个实施例中,所述第一栅线包括第一细栅线和第一主栅线,所述第一细栅线的数量为70根-105根,所述第一主栅线的数量为5根-12根,所述第二栅线包括第二细栅线和第二主栅线,所述第二细栅线的数量为70根-105根,所述第二主栅线的数量为5根-12根。

87.形成所述第一栅线和所述第二栅线之后,进行光注入退火处理,所述光注入退火处理包括依次进行的第一温区光注入退火处理至第n温区光注入退火处理,n为大于或等于1的整数;第一温区光注入退火处理至第n温区光注入退火处理的温度为100℃-250℃。

88.在一个实施例中,n为等于或大于8的整数,第一温区退火处理至第三温区退火处理的温度为138℃-142℃,第四温区退火处理至第六温区退火处理的温度为155℃-175℃,第六温区退火处理至第n温区退火处理的温度为145℃-155℃,所述第六温区至第n温区的温度递减。

89.在一个实施例中,相邻温区的温度差异在10℃以内,符合温区的温度波动的要求。

90.在一个实施例中,第一温区退火处理至第三温区退火处理用于使银浆中有机物的

充分挥发;第四温区退火处理至第六温区退火处理的目的是为了使银浆固化到所述第一掺杂半导体层表面或第二掺杂半导体层表面;第六温区退火处理至第n温区退火处理的目的是为了使银浆缓慢固化,有利于提高所述异质结电池的稳定性。

91.对进行光注入退火处理之后的异质结电池进行测试,具体的,对所述异质结电池的电性能进行测试,测试所使用的仪器包括电压测试机;所述电性能包括所述异质结电池的转换效率(eta)、开路电压(uoc)、短路电流(isc)、填充因子(ff)、串联电阻(rs)、并联电阻(rsh)、漏电流(irev2)等。

92.在一个实施例中,所述异质结电池的转换效率(eta)为23%-25%,开路电压(uoc)为743mv-743mv,比如743mv,短路电流(isc)为10a-11a,比如10.6a;填充因子(ff)为83%-84%,比如83.5%;串联电阻(rs)为0.0014欧姆-0.0021欧姆(不同设备测试得到的数值范围稍有区别,此为halm测试结果);漏电电流(irev2)为0.0013a-0.0015a,比如0.0013a。

93.本实施例还提供了一种异质结电池,参考图5,包括:

94.半导体衬底层1;

95.位于所述半导体衬底层1至少一侧表面的隧穿介质膜,所述隧穿介质膜中具有若干微孔;

96.位于所述隧穿介质膜背离所述半导体衬底层的一侧表面的掺杂半导体层。

97.在一个实施例中,所述隧穿介质膜的厚度为1nm-10nm,例如5nm;若所述隧穿介质膜的厚度小于1nm,则所述隧穿介质膜钝化所述半导体衬底层的效果不明显;若所述隧穿介质膜的厚度大于10nm,则会导致载流子隧穿所述隧穿介质膜的效果不明显。

98.本实施例中,所述隧穿介质膜的材料包括氧化硅,在其他实施例中,所述隧穿介质膜的材料还可以是其他材料。

99.所述微孔用于使载流子更好的传输。

100.在一个实施例中,所述微孔2的直径大小为1nm-500nm,例如200nm,所述微孔2使载流子传输的效果更好。若所述微孔的直径小于1nm,则会导致载流子运输效果不明显进而提高短路电流效果不明显;若所述微孔的直径大于500nm,则会导致所述隧穿介质膜钝化所述半导体衬底层效果不明显,而提高开路电压效果不明显。

101.在一个实施例中,所述微孔均匀分布,所述微孔均匀分布可以使载流子传输的效果更好;在其他实施例中,所述微孔不均匀分布。

102.在一个实施例中,所述微孔2的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比为1%-30%,若所述微孔的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比小于1%,则会导致载流子运输效果不明显进而提高短路电流效果不明显;若所述微孔的表面积与所述半导体衬底层背离所述隧穿介质膜的面积比大于30%,则会导致所述隧穿介质膜钝化所述半导体衬底层效果不明显而提高开路电压效果不明显。

103.继续参考图5,所述隧穿介质膜包括:位于所述半导体衬底层1的一侧表面的第一隧穿介质膜201;位于所述半导体衬底层的另一侧表面的第二隧穿介质膜202。

104.具体的,所述第一隧穿介质膜201的厚度为1nm-10nm,例如5nm;若所述第一隧穿介质膜201的厚度小于1nm,则所述隧穿介质膜钝化所述半导体衬底层的效果不明显;若所述第一隧穿介质膜201的厚度大于10nm,则会导致载流子隧穿所述隧穿介质膜的效果不明显。

105.本实施例中,所述第一隧穿介质膜201的材料包括氧化硅,在其他实施例中,所述

第一隧穿介质膜的材料还可以是其他材料。

106.具体的,所述第二隧穿介质膜202的厚度为1nm-10nm,例如5nm;若所述第二隧穿介质膜202的厚度小于1nm,则所述隧穿介质膜钝化所述半导体衬底层的效果不明显;若所述第二隧穿介质膜202的厚度大于10nm,则会导致载流子隧穿所述隧穿介质膜的效果不明显。

107.本实施例中,所述第二隧穿介质膜202的材料包括氧化硅,在其他实施例中,所述第二隧穿介质膜的材料还可以是其他材料。

108.所述异质结电池还包括:位于所述第一隧穿介质膜201背离所述半导体衬底层1的一侧表面的第一掺杂半导体层301;位于所述第二隧穿介质膜202背离所述半导体衬底层的一侧表面的第二掺杂半导体层302,所述第一掺杂半导体层301的导电类型为p型,所述第二掺杂半导体层302的导电类型为n型。

109.在一个实施例中,所述第一掺杂半导体层301的厚度为5nm-15nm,例如3nm;所述第二掺杂半导体层302的厚度为5nm-15nm,例如3nm。

110.所述异质结电池还包括:在所述第一掺杂半导体层301背离所述半导体衬底层1的第一透明导电膜401,在所述第二掺杂半导体层302背离所述半导体衬底层1的第二透明导电膜402,所述第一透明导电膜401的厚度为100nm-150nm,所述第二透明导电膜402的厚度为100nm-150nm。

111.所述异质结电池还包括:在所述掺杂半导体层背离所述半导体衬底层1的一侧的栅线(图中未示出)。

112.具体的,在所述第一透明导电膜401背离所述半导体衬底层1的一侧的第一栅线,在所述第二透明导电膜402背离所述半导体衬底层1的一侧的第二栅线。

113.在一个实施例中,所述第一栅线包括第一细栅线和第一主栅线,所述第一细栅线的数量为70根-105根,所述第一主栅线的数量为5根-12根,所述第二栅线包括第二细栅线和第二主栅线,所述第二细栅线的数量为70根-105根,所述第二主栅线的数量为5根-12根。

114.显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1