一种三相桥式全控整流触发驱动电路的制作方法

1.本实用新型涉及一种驱动电路领域,更具体地说,涉及一种三相桥式全控整流触发驱动电路。

背景技术:

2.电力电子技术是一种以功率半导体器件为硬件基础,由电力技术、电子技术、 现代控制技术交叉形成的技术平台。

3.整流是电力电子变流技术的一种,它将交流电变换成直流电。在三相整流的输入侧为三相交流电源。以晶闸管作为半导体开关的三相整流技术被称为三相相控整流。以晶闸管为开关器件的相控整流系统,因其高效率,允许温升大、寿命长,小巧轻便,触发方便等特点,被广泛应用于工业与社会的各个领域,如电力、电镀电解、电化学、钢铁和电气轨道机车等。

4.三相桥式全控整流系统中,生成触发脉冲的装置扮演着十分重要的角色,这是因为触发脉冲的质量直接影响到直流侧输出的质量,甚至会影响整个整流系统的稳定。随着电子技术的发展,采用微处理器作为控制核心的全数字触发器已经逐渐发展起来。虽然它具有集成度高、智能化、可编程等特点。但在大功率整流控制中存在较强的电磁干扰问题,微控制器由于其内部结构和控制逻辑复杂,极易受到外界的电磁干扰,出现控制错误、死机等故障,对系统的可靠性和稳定性带来较大的安全隐患;另外触发驱动器主要通过微处理器的控制算法实现,故对微处理器的运算能力有较高的要求,一定程度上增加了触发电路的成本。

技术实现要素:

5.本实用新型为了克服现有技术中存在的传统的驱动电路稳定性较低的问题,现提供具有高稳定性的一种三相桥式全控整流触发驱动电路。

6.本实用新型的一种三相桥式全控整流触发驱动电路,一种三相桥式全控整流触发驱动电路,包括线电压u

ac

、线电压u

ab

、线电压u

bc

、线电压检测模块、相位调节触发模块、触发脉冲宽度锁定模块、多窄脉冲触发驱动模块和晶闸管模块,所述的线电压u

ac

、线电压u

ab

和线电压u

bc

分别与线电压检测模块的输入端电性连接,所述的线电压检测模块的输出端与相位调节触发模块的输入端电性连接,所述的相位调节触发模块的输出端与触发脉冲宽度锁定模块的输入端电性连接,所述的触发脉冲宽度锁定模块的输出端与多窄脉冲触发驱动模块的输入端电性连接,所述的多窄脉冲触发驱动模块的输出端与晶闸管的输入端电性连接。

7.所述的晶闸管模块包括晶闸管vt6

‑

vt1、晶闸管vt1

‑

vt2、晶闸管vt2

‑

vt3、晶闸管vt3

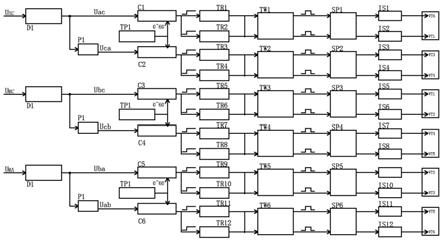

‑

vt4、晶闸管vt4

‑

vt5和晶闸管vt5

‑

vt6。

8.所述的线电压检测模块主要由3路差分放大电路及3路反向放大电路组成。其中3路差分放大电路分别将uac、ubc、uba正弦信号线性缩小;3路反向放大电路分别将缩小后的

线电压进行180

°

相位反向操作。通过差分放大及反向放大电路后得到uac、ubc、uba、uca、ucb、uab六路60

°

相位差正弦分量,分别作为晶闸管vt6

‑

vt1、vt1

‑

vt2、vt2

‑

vt3、vt3

‑

vt4、vt4

‑

vt5、vt5

‑

vt6触发基准信号。

9.所述的相位调节触发模块主要包括触发相位调节电路、比较触发电路、触发复位电路组成。其中触发相位调节电路主要通过调节触发电平来实现触发相位调节;比较触发电路是将前级线电压检测模块输入的6路正弦交流分量与触发电平比较,当小于触发电平时触发驱动输出,从而通过触发相位调节电路、比较触发电路进行触发控制,实现直流侧的调压和调功。另外由于比较触发后电平将长时间保持触发电平状态(即无法在60

°

内完成复位),造成滞后60

°

基准信号对同个晶闸管触发失败(如uac触发vt6

‑

vt1后ubc触发vt1

‑

vt2将失败),故所述的触发复位电路需要完成两个功能:a、对各路基准信号完成双路晶闸管触发输出;b、将触发后的电平信号实现自动复位。

10.所述的触发脉冲宽度锁定模块首先接收相位调节触发模块发送的触发信号,通过上升沿的触发及模块电路调理,将触发脉冲调制成固定脉宽信号,从而确定后级触发驱动时机及时间宽度,提升触发可靠性和稳定性。

11.所述的多窄脉冲触发驱动模块主要由多窄脉冲发生电路、隔离驱动电路组成,多窄脉冲发生电路接收前级固定脉宽信号,在固定脉宽时间内发送多个窄脉冲信号,从而避免单次触发失败的缺陷,确保被驱动晶闸管的可靠触发。所述的隔离驱动电路负责电气隔离,保证强弱电的电气隔离。

12.所述的三相桥式全控整流触发驱动电路通过功能模块划分及处理,将复杂的控制逻辑进行拆分、分级处理。通过线电压检测模块完成6路线电压检测,通过相位调节触发模块捕捉触发时刻及触发时段,通过多窄脉冲触发驱动模块在触发时段内多次发送触发信号,从而保证对6路晶闸管的可靠、稳定触发,从而实现可靠的整流、调压、调功功能。

13.作为优选,所述的线电压检测模块包括差分放大电路d1、差分放大电路d2、差分放大电路d3、反向放大电路p1、反向放大电路p2和反向放大电路p3,所述的线电压u

ac

与差分放大电路d1的输入端电性连接,所述的差分放大电路d1的一号输出端可得电压u

ac

,所述的差分放大电路d1的二号输出端与反向放大电路p1的输入端电性连接,所述的反向放大电路p1的输出端可得电压u

ca

,所述的电压u

ac

和电压u

ca

分别与相位调节触发模块的输入端电性连接;所述的线电压u

bc

与差分放大电路d2的输入端电性连接,所述的差分放大电路d2的一号输出端可得电压u

bc

,所述的差分放大电路d2的二号输出端与反向放大电路p2的输入端电性连接,所述的反向放大电路p2的输出端可得电压u

cb

,所述的电压u

bc

和电压u

cb

分别与相位调节触发模块的输入端电性连接;所述的线电压u

ba

与差分放大电路d3的输入端电性连接,所述的差分放大电路d3的一号输出端可得电压u

ba

,所述的差分放大电路d3的二号输出端与反向放大电路p3的输入端电性连接,所述的反向放大电路p3的输出端可得电压u

ab

,所述的电压u

ba

和电压u

ab

分别与相位调节触发模块的输入端电性连接。

14.作为优选,所述的相位调节触发模块包括触发相位调节电路tp1、触发相位调节电路tp2、触发相位调节电路tp3、比较触发电路c1、比较触发电路c2、比较触发电路c3、比较触发电路c4、比较触发电路c5、比较触发电路c6、触发复位电路tr1、触发复位电路tr2、触发复位电路tr3、触发复位电路tr4、触发复位电路tr5、触发复位电路tr6、触发复位电路tr7、触发复位电路tr8、触发复位电路tr9、触发复位电路tr10、触发复位电路tr11和触发复位电路

tr12,所述的比较触发电路c1的输入端与电压u

ac

电性连接,所述的比较触发电路c1的输出端分别与触发复位电路tr1的输入端和触发复位电路tr2的输入端电性连接,所述的比较触发电路c2的输入端与电压u

ca

电性连接,所述的比较触发电路c2的输出端分别与触发复位电路tr3的输入端和触发复位电路tr4的输入端电性连接,所述的触发相位调节电路tp1的输出端分别与比较触发电路c1的输入端和比较触发电路c2的输入端电性连接;所述的比较触发电路c3的输入端与电压u

bc

电性连接,所述的比较触发电路c3的输出端分别与触发复位电路tr5的输入端和触发复位电路tr6的输入端电性连接,所述的比较触发电路c4的输入端与电压u

cb

电性连接,所述的比较触发电路c4的输出端分别与触发复位电路tr7的输入端和触发复位电路tr8的输入端电性连接,所述的触发相位调节电路tp2的输出端分别与比较触发电路c3的输入端和比较触发电路c4的输入端电性连接;所述的比较触发电路c5的输入端与电压u

ba

电性连接,所述的比较触发电路c5的输出端分别与触发复位电路tr9的输入端和触发复位电路tr10的输入端电性连接,所述的比较触发电路c6的输入端与电压u

ab

电性连接,所述的比较触发电路c6的输出端分别与触发复位电路tr11的输入端和触发复位电路tr12的输入端电性连接,所述的触发相位调节电路tp3的输出端分别与比较触发电路c5的输入端和比较触发电路c6的输入端电性连接。

15.作为优选,所述的触发脉冲宽度锁定模块包括触发脉冲宽度锁定电路tw1、触发脉冲宽度锁定电路tw2、触发脉冲宽度锁定电路tw3、触发脉冲宽度锁定电路tw4、触发脉冲宽度锁定电路tw5和触发脉冲宽度锁定电路tw6,所述的触发复位电路tr1的输出端和触发复位电路tr2的输出端分别与触发脉冲宽度锁定电路tw1的一号输入端和二号输入端电性连接;所述的触发复位电路tr3的输出端和触发复位电路tr4的输出端分别与触发脉冲宽度锁定电路tw2的一号输入端和二号输入端电性连接;所述的触发复位电路tr5的输出端和触发复位电路tr6的输出端分别与触发脉冲宽度锁定电路tw3的一号输入端和二号输入端电性连接;所述的触发复位电路tr7的输出端和触发复位电路tr8的输出端分别与触发脉冲宽度锁定电路tw4的一号输入端和二号输入端电性连接;所述的触发复位电路tr9的输出端和触发复位电路tr10的输出端分别与触发脉冲宽度锁定电路tw5的一号输入端和二号输入端电性连接;所述的触发复位电路tr11的输出端和触发复位电路tr12的输出端分别与触发脉冲宽度锁定电路tw6的一号输入端和二号输入端电性连接。

16.作为优选,所述的多窄脉冲触发驱动模块包括多窄脉冲发生电路sp1、多窄脉冲发生电路sp2、多窄脉冲发生电路sp3、多窄脉冲发生电路sp4、多窄脉冲发生电路sp5、多窄脉冲发生电路sp6、隔离驱动电路is1、隔离驱动电路is2、隔离驱动电路is3、隔离驱动电路is4、隔离驱动电路is5、隔离驱动电路is6、隔离驱动电路is7、隔离驱动电路is8、隔离驱动电路is9、隔离驱动电路is10、隔离驱动电路is11和隔离驱动电路is12,所述的触发脉冲宽度锁定电路tw1的一号输出端和二号输出端分别与多窄脉冲发生电路sp1的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp1的一号输出端和二号输出端分别与隔离驱动电路is1的输入端和隔离驱动电路is1的输入端电性连接;所述的触发脉冲宽度锁定电路tw2的一号输出端和二号输出端分别与多窄脉冲发生电路sp2的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp2的一号输出端和二号输出端分别与隔离驱动电路is3的输入端和隔离驱动电路is4的输入端电性连接;所述的触发脉冲宽度锁定电路tw3的一号输出端和二号输出端分别与多窄脉冲发生电路sp3的一号输入端和二号输入端

电性连接,所述的多窄脉冲发生电路sp3的一号输出端和二号输出端分别与隔离驱动电路is5的输入端和隔离驱动电路is6的输入端电性连接;所述的触发脉冲宽度锁定电路tw4的一号输出端和二号输出端分别与多窄脉冲发生电路sp4的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp4的一号输出端和二号输出端分别与隔离驱动电路is7的输入端和隔离驱动电路is8的输入端电性连接;所述的触发脉冲宽度锁定电路tw5的一号输出端和二号输出端分别与多窄脉冲发生电路sp5的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp5的一号输出端和二号输出端分别与隔离驱动电路is9的输入端和隔离驱动电路is10的输入端电性连接;所述的触发脉冲宽度锁定电路tw6的一号输出端和二号输出端分别与多窄脉冲发生电路sp6的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp6的一号输出端和二号输出端分别与隔离驱动电路is11的输入端和隔离驱动电路is12的输入端电性连接。

17.作为优选,所述的晶闸管模块包括晶闸管vt6

‑

vt1、晶闸管vt1

‑

vt2、晶闸管vt2

‑

vt3、晶闸管vt3

‑

vt4、晶闸管vt4

‑

vt5和晶闸管vt5

‑

vt6,所述的晶闸管vt6

‑

vt1的tv6引脚与隔离驱动电路is1的输出端电性连接,所述的晶闸管vt6

‑

vt1的tv1引脚与隔离驱动电路is2的输出端电性连接;所述的晶闸管vt3

‑

vt4的tv3引脚与隔离驱动电路is3的输出端电性连接,所述的晶闸管vt3

‑

vt4的tv4引脚与隔离驱动电路is4的输出端电性连接;所述的晶闸管vt1

‑

vt2的tv1引脚与隔离驱动电路is5的输出端电性连接,所述的晶闸管vt1

‑

vt2的tv2引脚与隔离驱动电路is6的输出端电性连接;所述的晶闸管vt4

‑

vt5的tv4引脚与隔离驱动电路is7的输出端电性连接,所述的晶闸管vt4

‑

vt5的tv5引脚与隔离驱动电路is8的输出端电性连接;所述的晶闸管vt2

‑

vt3的tv2引脚与隔离驱动电路is9的输出端电性连接,所述的晶闸管vt2

‑

vt3的tv3引脚与隔离驱动电路is10的输出端电性连接;所述的晶闸管vt5

‑

vt6的tv5引脚与隔离驱动电路is11的输出端电性连接,所述的晶闸管vt5

‑

vt6的tv6引脚与隔离驱动电路is12的输出端电性连接。

18.作为优选,所述的线电压检测模块的电路结构包括排插j3、电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r6、电阻r7、电阻r8、电阻r9、运放芯片u1b和运放芯片u1a,所述的排插j3的1引脚与电阻r1的一端电性连接,所述的电阻r1的另一端与电阻r2的一端电性连接,所述的电阻r2的另一端分别与运放芯片u1a的2引脚和电阻r5的一端电性连接,所述的排插j3的2引脚与电阻r3的一端电性连接,所述的电阻r3的另一端与电阻r4的一端电性连接,所述的电阻r4的另一端与运放芯片u1a的3引脚电性连接,所述的电阻r5的另一端与运放芯片u1a的1引脚电性连接,所述的电阻r6的一端与运放芯片u1a的3引脚电性连接,所述的电阻r6的另一端与电阻r7的一端电性连接,所述的电阻r7的另一端与运放芯片u1b的5引脚电性连接,所述的运放芯片u1b的6引脚分别与电阻r8的一端和电阻r9的一端电性连接,所述的电阻r8的另一端与运放芯片u1a的1引脚电性连接,所述的电阻r9的另一端与运放芯片u1b的7引脚电性连接。

19.作为优选,所述的相位调节触发模块的电路结构包括电阻r10、电阻r12、电阻r13、电阻r14、电阻r15、电阻r16、电阻r17、可调电阻r11、电容c1、电容c2、电容c3、二极管d1、二极管d2、二极管d3、二极管d4、运放芯片u1c和运放芯片u7a,所述的电容c1的一端与电阻r10的一端电性连接并接+5v,所述的电容c1的另一端与电阻r12的一端电性连接并接地,所述的电阻r10的另一端与可调电阻r11的1引脚电性连接,所述的可调电阻r11的2引脚与电阻

r12的另一端电性连接,所述的可调电阻r11的3引脚与运放芯片u1c的10引脚电性连接,所述的运放芯片u1c的4引脚接+5v,所述的运放芯片u1c的11引脚接地,所述的运放芯片u1c的9引脚和运放芯片u1c的11引脚分与电阻r14的一端电性连接,所述的电阻r14的另一端分别与运放芯片u7a的3引脚和电阻r15的一端电性连接,所述的电阻r15的另一端分别与电阻r16的一端、电容c2的一端、电容c3的一端和电阻r17的一端电性连接,所述的电阻r16的另一端与运放芯片u7a的1引脚电性连接,所述的运放芯片u7a的2引脚与运放芯片u1a的1引脚电性连接,所述的电阻r17的另一端接+8v,所述的电容c2的另一端分别与二极管d1的正极和二极管d2负极电性连接,所述的电容c3的另一端分别与二极管d3的负极和二极管d4正极电性连接,所述的二极管d2的正极和二极管d3的正极分别接地,所述的二极管d1的负极和二极管d4的负极分别与触发脉冲宽度锁定模块的输入端电性连接。

20.作为优选,所述的触发脉冲宽度锁定模块的电路结构包括控制芯片u9、电阻r17、电阻r18、电阻r19、电阻r20、电阻r21、电阻r22、电阻r23、电阻r24、电容c4、电容c5、电容c6和电容c7,所述的控制芯片u9的1引脚与电容c4的一端电性连接,所述的控制芯片u9的2引脚分别与电阻r17的一端和电容c4的另一端电性连接,所述的电阻r17的另一端与电阻r18的一端电性连接并接+8v,所述的电阻r18的另一端分别与控制芯片u9的3引脚和控制芯片u9的5引脚电性连接,所述的控制芯片u9的4引脚分别与电阻r19的一端和二极管d1的负极电性连接,所述的电阻r19的另一端接地,所述的控制芯片u9的15引脚与电容c5的一端电性连接,所述的控制芯片u9的14引脚分别与电阻r20的一端和电容c5的另一端电性连接,所述的电阻r20的另一端与电阻r21的一端电性连接并接+8v,所述的电阻r21的另一端分别与控制芯片u9的13引脚和控制芯片u9的11引脚电性连接,所述的控制芯片u9的12引脚分别与电阻r22的一端和二极管d4的负极电性连接,所述的电阻r22的另一端接地,所述的控制芯片u9的8引脚接地,所述的控制芯片u9的6引脚与电阻r23的一端电性连接,所述的控制芯片u9的10引脚与电阻r24的一端电性连接,所述的电阻r23的另一端和电阻r24的另一端分别与多窄脉冲触发驱动模块的输入端电性连接,所述的控制芯片u9的16引脚分别与电容c6的一端和电容c7的一端电性连接并接+8v,所述的电容c6的另一端和电容c7的另一端分别接地。

21.作为优选,所述的多窄脉冲触发驱动模块的电路结构包括控制芯片u10、控制芯片u11、电阻r25、电阻r26、电阻r27、电阻r28、电阻r29、电阻r30、电阻r31、电阻r32、电阻r33、电阻r34、电阻r35、电阻r36、电阻r37、电阻r38、电容c6、电容c7、电容c8、电容c9、电容c10、电容c11、电容c12、电容c13、电容c14、电容c15、二极管d5、二极管d6、二极管d7、二极管d8、二极管d9、二极管d10、mos管m1、mos管m2、变压器pt1、变压器pt2、排插j9和排插j10,所述的控制芯片u10的1引脚接地,所述的控制芯片u10的2引脚分别与控制芯片u10的6引脚、电阻r26的一端、二极管d5的负极和电容c6的一端电性连接,所述的电容c6的另一端接地,所述的控制芯片u10的7引脚分别与二极管d5的正极、电阻r26的另一端和电阻r25的一端电性连接,所述的控制芯片u10的4引脚与电阻r24的另一端电性连接,所述的电阻r25的另一端分别与控制芯片u10的8引脚、电容c7的一端、电容c8的一端和电阻r27的一端电性连接并接+8v,所述的电容c7的另一端和电容c8的另一端分别接地,所述的控制芯片u10的3引脚分别与电阻r27的另一端和电阻r31的一端电性连接,所述的电阻r31的另一端与mos管m1的1引脚电性连接,所述的mos管m1的2引脚接地,所述的mos管m1的3引脚分别与二极管d4的正极和变压器pt1的2引脚电性连接,所述的二极管d4的负极与电阻r28的一端电性连接,所述的

电阻r28的另一端分别与变压器pt1的1引脚、电容c9的一端和电容c10的一端电性连接并接+8v,所述的电容c9的另一端和电容c10的另一端分别接地,所述的变压器pt1的3引脚分别与二极管d7的正极、电阻r29的一端、电阻r30的一端和排插j9的2引脚电性连接,所述的变压器pt1的4引脚与二极管d6的正极电性连接,所述的二极管d6的负极分别与二极管d7的负极、电阻r29的另一端、电阻r30的另一端和排插j9的1引脚电性连接;所述的控制芯片u11的1引脚接地,所述的控制芯片u11的2引脚分别与控制芯片u11的6引脚、电阻r33的一端、二极管d8的负极和电容c11的一端电性连接,所述的电容c11的另一端接地,所述的控制芯片u11的7引脚分别与二极管d8的正极、电阻r33的另一端和电阻r32的一端电性连接,所述的控制芯片u11的4引脚与电阻r23的另一端电性连接,所述的电阻r32的另一端分别与控制芯片u11的8引脚、电容c12的一端、电容c13的一端和电阻r34的一端电性连接并接+8v,所述的电容c12的另一端和电容c13的另一端分别接地,所述的控制芯片u11的3引脚分别与电阻r34的另一端和电阻r38的一端电性连接,所述的电阻r38的另一端与mos管m2的1引脚电性连接,所述的mos管m2的2引脚接地,所述的mos管m2的3引脚分别与二极管d4的正极和变压器pt1的2引脚电性连接,所述的二极管d4的负极与电阻r35的一端电性连接,所述的电阻r35的另一端分别与变压器pt2的1引脚、电容c14的一端和电容c15的一端电性连接并接+8v,所述的电容c14的另一端和电容c15的另一端分别接地,所述的变压器pt2的3引脚分别与二极管d10的正极、电阻r36的一端、电阻r37的一端和排插j10的2引脚电性连接,所述的变压器pt2的4引脚与二极管d9的正极电性连接,所述的二极管d9的负极分别与二极管d10的负极、电阻r36的另一端、电阻r37的另一端和排插j10的1引脚电性连接。

22.所述的线电压检测模块将uac线电压通过d1差分放大电路进行信号缩小,再通过p1反向器后得到两路相位差180

°

电压信号uac、uca;同理通过线电压ubc、uba通过差分电路及反向器得到ubc、ucb、uba、uab线电压信号(电路结构同uac)。通过线电压检测模块可获得uac、ubc、uba、uca、ucb、uab六路依次滞后60

°

正弦分量,作为作为晶闸管vt6

‑

vt1、vt1

‑

vt2、vt2

‑

vt3、vt3

‑

vt4、vt4

‑

vt5、vt5

‑

vt6触发基准信号。

23.所述的相位调节触发模块中tp1进行触发相位调节,通过c1比较触发电路1的比较功能对uac的正弦信号与tp1触发相位调节电平进行比较,当uac电压小于tp1触发相位电平时,c1比较触发电路输出高电平,tr1触发复位1和tr2触发复位2接收高电平后产生上升沿跳变分别用于vt6、vt1触发信号,并立即复位为低电平,目的是避免与来自其他触发高电平冲突,例如来自ubc触发的vt1,来自uab触发的vt6。同理获得ubc、uba、uca、ucb、uab触发复位信号,分别用于触发vt1

‑

vt2、vt2

‑

vt3、vt3

‑

vt4、vt4

‑

vt5、vt5

‑

vt6。

24.所述的脉冲宽度锁定模块,tw1接收tr1触发复位1和tr2触发复位2上升沿信号后,输出脉冲宽度固定为0.6ms驱动时间,用于后级驱动vt6、vt1。同理tw2和tw3获得vt2、vt3、vt4、vt5的脉冲驱动时间。

25.所述的多窄脉冲触发驱动模块通过sp1多窄脉冲发生电路接收tw1触发脉冲宽度锁定电路发出的固定脉宽信号,在固定脉冲时间内(0.6ms)生成多个窄脉冲信号,并通过is1和is2隔离驱动,通过多次窄脉冲驱动晶闸管门极vt6、vt1。同理可获得vt2、vt3、vt4、vt5的驱动信号。

26.其中控制芯片u9的型号为:hef4538b;控制芯片u10和控制芯片u11的型号都为:ne555d;mos管m1和mos管m1都为n型mos管。

27.本实用新型具有以下有益效果:抗干扰能力强,控制简单可靠,电路结构功能分级模块化,成本低廉。

附图说明

28.附图1为本实用新型的电路结构框图。

29.附图2为本实用新型的线电压检测模块的电路原理图。

30.附图3为本实用新型的相位调节触发模块的电路原理图。

31.附图4为本实用新型的触发脉冲宽度锁定模块的电路原理图。

32.附图5为本实用新型的多窄脉冲触发驱动模块的电路原理图。

具体实施方式

33.下面通过实施例,并结合附图,对本实用新型的技术方案作进一步具体的说明。

34.实施例:根据附图1、附图2、附图3、附图4和附图5进行进一步说明,本例的一种三相桥式全控整流触发驱动电路,包括线电压u

ac

、线电压u

ab

、线电压u

bc

、线电压检测模块、相位调节触发模块、触发脉冲宽度锁定模块、多窄脉冲触发驱动模块和晶闸管模块,所述的线电压u

ac

、线电压u

ab

和线电压u

bc

分别与线电压检测模块的输入端电性连接,所述的线电压检测模块的输出端与相位调节触发模块的输入端电性连接,所述的相位调节触发模块的输出端与触发脉冲宽度锁定模块的输入端电性连接,所述的触发脉冲宽度锁定模块的输出端与多窄脉冲触发驱动模块的输入端电性连接,所述的多窄脉冲触发驱动模块的输出端与晶闸管的输入端电性连接。

35.所述的线电压检测模块包括差分放大电路d1、差分放大电路d2、差分放大电路d3、反向放大电路p1、反向放大电路p2和反向放大电路p3,所述的线电压u

ac

与差分放大电路d1的输入端电性连接,所述的差分放大电路d1的一号输出端可得电压u

ac

,所述的差分放大电路d1的二号输出端与反向放大电路p1的输入端电性连接,所述的反向放大电路p1的输出端可得电压u

ca

,所述的电压u

ac

和电压u

ca

分别与相位调节触发模块的输入端电性连接;所述的线电压u

bc

与差分放大电路d2的输入端电性连接,所述的差分放大电路d2的一号输出端可得电压u

bc

,所述的差分放大电路d2的二号输出端与反向放大电路p2的输入端电性连接,所述的反向放大电路p2的输出端可得电压u

cb

,所述的电压u

bc

和电压u

cb

分别与相位调节触发模块的输入端电性连接;所述的线电压u

ba

与差分放大电路d3的输入端电性连接,所述的差分放大电路d3的一号输出端可得电压u

ba

,所述的差分放大电路d3的二号输出端与反向放大电路p3的输入端电性连接,所述的反向放大电路p3的输出端可得电压u

ab

,所述的电压u

ba

和电压u

ab

分别与相位调节触发模块的输入端电性连接。

36.所述的相位调节触发模块包括触发相位调节电路tp1、触发相位调节电路tp2、触发相位调节电路tp3、比较触发电路c1、比较触发电路c2、比较触发电路c3、比较触发电路c4、比较触发电路c5、比较触发电路c6、触发复位电路tr1、触发复位电路tr2、触发复位电路tr3、触发复位电路tr4、触发复位电路tr5、触发复位电路tr6、触发复位电路tr7、触发复位电路tr8、触发复位电路tr9、触发复位电路tr10、触发复位电路tr11和触发复位电路tr12,所述的比较触发电路c1的输入端与电压u

ac

电性连接,所述的比较触发电路c1的输出端分别与触发复位电路tr1的输入端和触发复位电路tr2的输入端电性连接,所述的比较触发电路

c2的输入端与电压u

ca

电性连接,所述的比较触发电路c2的输出端分别与触发复位电路tr3的输入端和触发复位电路tr4的输入端电性连接,所述的触发相位调节电路tp1的输出端分别与比较触发电路c1的输入端和比较触发电路c2的输入端电性连接;所述的比较触发电路c3的输入端与电压u

bc

电性连接,所述的比较触发电路c3的输出端分别与触发复位电路tr5的输入端和触发复位电路tr6的输入端电性连接,所述的比较触发电路c4的输入端与电压u

cb

电性连接,所述的比较触发电路c4的输出端分别与触发复位电路tr7的输入端和触发复位电路tr8的输入端电性连接,所述的触发相位调节电路tp2的输出端分别与比较触发电路c3的输入端和比较触发电路c4的输入端电性连接;所述的比较触发电路c5的输入端与电压u

ba

电性连接,所述的比较触发电路c5的输出端分别与触发复位电路tr9的输入端和触发复位电路tr10的输入端电性连接,所述的比较触发电路c6的输入端与电压u

ab

电性连接,所述的比较触发电路c6的输出端分别与触发复位电路tr11的输入端和触发复位电路tr12的输入端电性连接,所述的触发相位调节电路tp3的输出端分别与比较触发电路c5的输入端和比较触发电路c6的输入端电性连接。

37.所述的触发脉冲宽度锁定模块包括触发脉冲宽度锁定电路tw1、触发脉冲宽度锁定电路tw2、触发脉冲宽度锁定电路tw3、触发脉冲宽度锁定电路tw4、触发脉冲宽度锁定电路tw5和触发脉冲宽度锁定电路tw6,所述的触发复位电路tr1的输出端和触发复位电路tr2的输出端分别与触发脉冲宽度锁定电路tw1的一号输入端和二号输入端电性连接;所述的触发复位电路tr3的输出端和触发复位电路tr4的输出端分别与触发脉冲宽度锁定电路tw2的一号输入端和二号输入端电性连接;所述的触发复位电路tr5的输出端和触发复位电路tr6的输出端分别与触发脉冲宽度锁定电路tw3的一号输入端和二号输入端电性连接;所述的触发复位电路tr7的输出端和触发复位电路tr8的输出端分别与触发脉冲宽度锁定电路tw4的一号输入端和二号输入端电性连接;所述的触发复位电路tr9的输出端和触发复位电路tr10的输出端分别与触发脉冲宽度锁定电路tw5的一号输入端和二号输入端电性连接;所述的触发复位电路tr11的输出端和触发复位电路tr12的输出端分别与触发脉冲宽度锁定电路tw6的一号输入端和二号输入端电性连接。

38.所述的多窄脉冲触发驱动模块包括多窄脉冲发生电路sp1、多窄脉冲发生电路sp2、多窄脉冲发生电路sp3、多窄脉冲发生电路sp4、多窄脉冲发生电路sp5、多窄脉冲发生电路sp6、隔离驱动电路is1、隔离驱动电路is2、隔离驱动电路is3、隔离驱动电路is4、隔离驱动电路is5、隔离驱动电路is6、隔离驱动电路is7、隔离驱动电路is8、隔离驱动电路is9、隔离驱动电路is10、隔离驱动电路is11和隔离驱动电路is12,所述的触发脉冲宽度锁定电路tw1的一号输出端和二号输出端分别与多窄脉冲发生电路sp1的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp1的一号输出端和二号输出端分别与隔离驱动电路is1的输入端和隔离驱动电路is1的输入端电性连接;所述的触发脉冲宽度锁定电路tw2的一号输出端和二号输出端分别与多窄脉冲发生电路sp2的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp2的一号输出端和二号输出端分别与隔离驱动电路is3的输入端和隔离驱动电路is4的输入端电性连接;所述的触发脉冲宽度锁定电路tw3的一号输出端和二号输出端分别与多窄脉冲发生电路sp3的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp3的一号输出端和二号输出端分别与隔离驱动电路is5的输入端和隔离驱动电路is6的输入端电性连接;所述的触发脉冲宽度锁定电路tw4的一号输出端和

二号输出端分别与多窄脉冲发生电路sp4的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp4的一号输出端和二号输出端分别与隔离驱动电路is7的输入端和隔离驱动电路is8的输入端电性连接;所述的触发脉冲宽度锁定电路tw5的一号输出端和二号输出端分别与多窄脉冲发生电路sp5的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp5的一号输出端和二号输出端分别与隔离驱动电路is9的输入端和隔离驱动电路is10的输入端电性连接;所述的触发脉冲宽度锁定电路tw6的一号输出端和二号输出端分别与多窄脉冲发生电路sp6的一号输入端和二号输入端电性连接,所述的多窄脉冲发生电路sp6的一号输出端和二号输出端分别与隔离驱动电路is11的输入端和隔离驱动电路is12的输入端电性连接。

39.所述的晶闸管模块包括晶闸管vt6

‑

vt1、晶闸管vt1

‑

vt2、晶闸管vt2

‑

vt3、晶闸管vt3

‑

vt4、晶闸管vt4

‑

vt5和晶闸管vt5

‑

vt6,所述的晶闸管vt6

‑

vt1的tv6引脚与隔离驱动电路is1的输出端电性连接,所述的晶闸管vt6

‑

vt1的tv1引脚与隔离驱动电路is2的输出端电性连接;所述的晶闸管vt3

‑

vt4的tv3引脚与隔离驱动电路is3的输出端电性连接,所述的晶闸管vt3

‑

vt4的tv4引脚与隔离驱动电路is4的输出端电性连接;所述的晶闸管vt1

‑

vt2的tv1引脚与隔离驱动电路is5的输出端电性连接,所述的晶闸管vt1

‑

vt2的tv2引脚与隔离驱动电路is6的输出端电性连接;所述的晶闸管vt4

‑

vt5的tv4引脚与隔离驱动电路is7的输出端电性连接,所述的晶闸管vt4

‑

vt5的tv5引脚与隔离驱动电路is8的输出端电性连接;所述的晶闸管vt2

‑

vt3的tv2引脚与隔离驱动电路is9的输出端电性连接,所述的晶闸管vt2

‑

vt3的tv3引脚与隔离驱动电路is10的输出端电性连接;所述的晶闸管vt5

‑

vt6的tv5引脚与隔离驱动电路is11的输出端电性连接,所述的晶闸管vt5

‑

vt6的tv6引脚与隔离驱动电路is12的输出端电性连接。

40.所述的线电压检测模块的电路结构包括排插j3、电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r6、电阻r7、电阻r8、电阻r9、运放芯片u1b和运放芯片u1a,所述的排插j3的1引脚与电阻r1的一端电性连接,所述的电阻r1的另一端与电阻r2的一端电性连接,所述的电阻r2的另一端分别与运放芯片u1a的2引脚和电阻r5的一端电性连接,所述的排插j3的2引脚与电阻r3的一端电性连接,所述的电阻r3的另一端与电阻r4的一端电性连接,所述的电阻r4的另一端与运放芯片u1a的3引脚电性连接,所述的电阻r5的另一端与运放芯片u1a的1引脚电性连接,所述的电阻r6的一端与运放芯片u1a的3引脚电性连接,所述的电阻r6的另一端与电阻r7的一端电性连接,所述的电阻r7的另一端与运放芯片u1b的5引脚电性连接,所述的运放芯片u1b的6引脚分别与电阻r8的一端和电阻r9的一端电性连接,所述的电阻r8的另一端与运放芯片u1a的1引脚电性连接,所述的电阻r9的另一端与运放芯片u1b的7引脚电性连接。

41.所述的相位调节触发模块的电路结构包括电阻r10、电阻r12、电阻r13、电阻r14、电阻r15、电阻r16、电阻r17、可调电阻r11、电容c1、电容c2、电容c3、二极管d1、二极管d2、二极管d3、二极管d4、运放芯片u1c和运放芯片u7a,所述的电容c1的一端与电阻r10的一端电性连接并接+5v,所述的电容c1的另一端与电阻r12的一端电性连接并接地,所述的电阻r10的另一端与可调电阻r11的1引脚电性连接,所述的可调电阻r11的2引脚与电阻r12的另一端电性连接,所述的可调电阻r11的3引脚与运放芯片u1c的10引脚电性连接,所述的运放芯片u1c的4引脚接+5v,所述的运放芯片u1c的11引脚接地,所述的运放芯片u1c的9引脚和运

放芯片u1c的11引脚分与电阻r14的一端电性连接,所述的电阻r14的另一端分别与运放芯片u7a的3引脚和电阻r15的一端电性连接,所述的电阻r15的另一端分别与电阻r16的一端、电容c2的一端、电容c3的一端和电阻r17的一端电性连接,所述的电阻r16的另一端与运放芯片u7a的1引脚电性连接,所述的运放芯片u7a的2引脚与运放芯片u1a的1引脚电性连接,所述的电阻r17的另一端接+8v,所述的电容c2的另一端分别与二极管d1的正极和二极管d2负极电性连接,所述的电容c3的另一端分别与二极管d3的负极和二极管d4正极电性连接,所述的二极管d2的正极和二极管d3的正极分别接地,所述的二极管d1的负极和二极管d4的负极分别与触发脉冲宽度锁定模块的输入端电性连接。

42.所述的触发脉冲宽度锁定模块的电路结构包括控制芯片u9、电阻r17、电阻r18、电阻r19、电阻r20、电阻r21、电阻r22、电阻r23、电阻r24、电容c4、电容c5、电容c6和电容c7,所述的控制芯片u9的1引脚与电容c4的一端电性连接,所述的控制芯片u9的2引脚分别与电阻r17的一端和电容c4的另一端电性连接,所述的电阻r17的另一端与电阻r18的一端电性连接并接+8v,所述的电阻r18的另一端分别与控制芯片u9的3引脚和控制芯片u9的5引脚电性连接,所述的控制芯片u9的4引脚分别与电阻r19的一端和二极管d1的负极电性连接,所述的电阻r19的另一端接地,所述的控制芯片u9的15引脚与电容c5的一端电性连接,所述的控制芯片u9的14引脚分别与电阻r20的一端和电容c5的另一端电性连接,所述的电阻r20的另一端与电阻r21的一端电性连接并接+8v,所述的电阻r21的另一端分别与控制芯片u9的13引脚和控制芯片u9的11引脚电性连接,所述的控制芯片u9的12引脚分别与电阻r22的一端和二极管d4的负极电性连接,所述的电阻r22的另一端接地,所述的控制芯片u9的8引脚接地,所述的控制芯片u9的6引脚与电阻r23的一端电性连接,所述的控制芯片u9的10引脚与电阻r24的一端电性连接,所述的电阻r23的另一端和电阻r24的另一端分别与多窄脉冲触发驱动模块的输入端电性连接,所述的控制芯片u9的16引脚分别与电容c6的一端和电容c7的一端电性连接并接+8v,所述的电容c6的另一端和电容c7的另一端分别接地。

43.所述的多窄脉冲触发驱动模块的电路结构包括控制芯片u10、控制芯片u11、电阻r25、电阻r26、电阻r27、电阻r28、电阻r29、电阻r30、电阻r31、电阻r32、电阻r33、电阻r34、电阻r35、电阻r36、电阻r37、电阻r38、电容c6、电容c7、电容c8、电容c9、电容c10、电容c11、电容c12、电容c13、电容c14、电容c15、二极管d5、二极管d6、二极管d7、二极管d8、二极管d9、二极管d10、mos管m1、mos管m2、变压器pt1、变压器pt2、排插j9和排插j10,所述的控制芯片u10的1引脚接地,所述的控制芯片u10的2引脚分别与控制芯片u10的6引脚、电阻r26的一端、二极管d5的负极和电容c6的一端电性连接,所述的电容c6的另一端接地,所述的控制芯片u10的7引脚分别与二极管d5的正极、电阻r26的另一端和电阻r25的一端电性连接,所述的控制芯片u10的4引脚与电阻r24的另一端电性连接,所述的电阻r25的另一端分别与控制芯片u10的8引脚、电容c7的一端、电容c8的一端和电阻r27的一端电性连接并接+8v,所述的电容c7的另一端和电容c8的另一端分别接地,所述的控制芯片u10的3引脚分别与电阻r27的另一端和电阻r31的一端电性连接,所述的电阻r31的另一端与mos管m1的1引脚电性连接,所述的mos管m1的2引脚接地,所述的mos管m1的3引脚分别与二极管d4的正极和变压器pt1的2引脚电性连接,所述的二极管d4的负极与电阻r28的一端电性连接,所述的电阻r28的另一端分别与变压器pt1的1引脚、电容c9的一端和电容c10的一端电性连接并接+8v,所述的电容c9的另一端和电容c10的另一端分别接地,所述的变压器pt1的3引脚分别与二极

管d7的正极、电阻r29的一端、电阻r30的一端和排插j9的2引脚电性连接,所述的变压器pt1的4引脚与二极管d6的正极电性连接,所述的二极管d6的负极分别与二极管d7的负极、电阻r29的另一端、电阻r30的另一端和排插j9的1引脚电性连接;所述的控制芯片u11的1引脚接地,所述的控制芯片u11的2引脚分别与控制芯片u11的6引脚、电阻r33的一端、二极管d8的负极和电容c11的一端电性连接,所述的电容c11的另一端接地,所述的控制芯片u11的7引脚分别与二极管d8的正极、电阻r33的另一端和电阻r32的一端电性连接,所述的控制芯片u11的4引脚与电阻r23的另一端电性连接,所述的电阻r32的另一端分别与控制芯片u11的8引脚、电容c12的一端、电容c13的一端和电阻r34的一端电性连接并接+8v,所述的电容c12的另一端和电容c13的另一端分别接地,所述的控制芯片u11的3引脚分别与电阻r34的另一端和电阻r38的一端电性连接,所述的电阻r38的另一端与mos管m2的1引脚电性连接,所述的mos管m2的2引脚接地,所述的mos管m2的3引脚分别与二极管d4的正极和变压器pt1的2引脚电性连接,所述的二极管d4的负极与电阻r35的一端电性连接,所述的电阻r35的另一端分别与变压器pt2的1引脚、电容c14的一端和电容c15的一端电性连接并接+8v,所述的电容c14的另一端和电容c15的另一端分别接地,所述的变压器pt2的3引脚分别与二极管d10的正极、电阻r36的一端、电阻r37的一端和排插j10的2引脚电性连接,所述的变压器pt2的4引脚与二极管d9的正极电性连接,所述的二极管d9的负极分别与二极管d10的负极、电阻r36的另一端、电阻r37的另一端和排插j10的1引脚电性连接。

44.以上所述仅为本实用新型的具体实施例,但本实用新型的结构特征并不局限于此,任何本领域的技术人员在本实用新型的领域内,所作的变化或修饰皆涵盖在本实用新型的专利范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1