高速高分辨率数字控制振荡器及其方法与流程

[0001]

本公开大体上涉及数字控制振荡器;更明确地说,本公开涉及高速高分辨率数字控制振荡器。

背景技术:

[0002]

一数字控制振荡器(digitally-controlled oscillator,dco)依据一控制命令(control word)输出某一振荡频率的一振荡信号;举例而言,该振荡频率是由该控制命令来决定。当该控制命令改变时,该振荡频率相应地改变。一dco的速度是依据“该控制命令”与“该振荡频率的一相对应变化”之间的一延迟时间而被估量;该延迟时间愈短,代表该速度愈快。一dco的分辨率是依据该控制命令的一最小变化量所对应的该振荡频率的一变化量的量来决定;该振荡频率的增变化量愈少,代表该分辨率愈高。一dco通常包含于一闭回路中,其中该控制命令是按一反馈方式而决定,以使该振荡信号的一时序跟随一参考时序。该闭回路可以是一锁相回路,或一时钟数据回复回路。一高速dco能使该闭回路得以较快地跟上该参考时序。一高分辨率dco能使该振荡信号的时序得以较准确地跟随该参考时序。通常而言,本领域需要的是一高速高分辨率dco。

[0003]

一dco包含一核心电路与一调整网络(tuning network)。该核心电路是一主动电路,可以维持一振荡状态;该调整网络可以调整一振荡频率。环形振荡器(ring oscillator)是一种常见形态,用来实现该核心电路,这是因为环形振荡器在实体布局上是紧实的(compact)。当利用由cmos(互补式金属氧化物半导体)工艺所制造的单片(monolithic)集成电路来实现一dco时,该dco会受工艺、电压与温度(process,voltage,temperature,pvt)的变化影响,从而该dco的振荡频率会随着pvt变化而有明显的差异。若该dco是基于一环形振荡器形态,由pvt变化所带来的差异问题通常需要严肃以对。在另一方面,一高分辨率dco需要一具有精细调整能力的频率调整网络(a frequency-tuning network of a fine granularity),因此,该频率调整网络不仅需要具有一大调整范围以涵盖由pvt变化所造成的dco振荡频率的大幅差异,也需要具有精细调整能力,这通常要借助于一高度复杂调整网络。然而,一高度复杂调整网络通常不适用于高速应用,这是因为一较复杂的网络通常较慢。此外,一高速电路易有较多噪声(tends to be noisier)。因此,一高速高分辨率环形振荡器形态的dco通常很难设计,也很难满足一低噪声要求。

[0004]

本技术领域需要的是一环形振荡器形态的dco具有高速高分辨率的特性。

技术实现要素:

[0005]

依据本公开的一实施例,一种数字控制振荡器包含:一环形振荡器,包括多个增益级,该多个增益级按一带有一负反馈的一环形形态而串接在一起,以依据一供应节点的一供应电压输出一振荡信号至一级间节点(inter-stage node);一低速数字至模拟转换器(digital-to-analog converter,dac),用来输出一供应电流至该供应节点,以依据一粗调控制命令(coarse control word)确定该供应电压;一变容器阵列,用来依据一控制电压数

组(control voltage array)提供一电容性负载给该级间节点;以及一高速dac阵列,用来依据一细调控制命令输出该控制电压数组。

[0006]

依据本公开的一实施例,一种方法包含下列步骤:使用多个增益级按一环形形态串接在一起以形成一环形振荡器,该环形振荡器用来输出一振荡信号;使用一低速数字至模拟转换器(dac),以依据一粗调控制命令控制该环形振荡器的一供应电压;使用受控于一控制电压数组的一变容器阵列,以于该环形振荡器的一级间节点提供一电容性负载;使用一高速dac阵列,以依据一细调控制命令来确定该控制电压数组;随着一启动程序,调整该粗调控制命令,使得该振荡信号的一振荡频率趋近一目标值;以及依据该振荡信号的一时序误差的一检测结果,按一闭回路方式调整该细调控制命令。

[0007]

有关本发明的特征、实作与技术效果,兹配合附图作优选实施例详细说明如下。

附图说明

[0008]

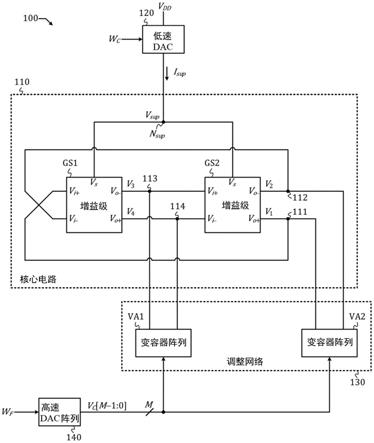

图1依据本公开的一实施例显示一数字控制振荡器的功能方框图。

[0009]

图2显示一增益级的一示范性实施例的示意图。

[0010]

图3显示一低速数字至模拟转换器的一示范性实施例的示意图。

[0011]

图4显示一变容器阵列的示意图。

[0012]

图5显示一高速数字至模拟转换器阵列的一示范性实施例的功能方框图。

[0013]

图6显示一高速数字至模拟转换器的一示范性实施例的示意图;以及

[0014]

图7依据本公开的一实施例显示一方法的一流程图。

[0015]

符号说明

[0016]

100 数字控制振荡器

[0017]

110 核心电路

[0018]

120 ls dac(低速数字至模拟转换器)

[0019]

130 调整网络

[0020]

140 hs dac array(高速dac阵列)

[0021]

n

sup 供应节点

[0022]

v

sup 供应电压

[0023]

i

sup 供应电流

[0024]

w

c 粗调控制命令

[0025]

w

f 细调控制命令

[0026]

v

c

[m-1:0] m维控制电压数组

[0027]

m 大于一的整数

[0028]

gs1 第一增益级

[0029]

gs2 第二增益级

[0030]

v

i+ 第一输入引脚

[0031]

v

i- 第二输入引脚

[0032]

v

o+ 第一输出引脚

[0033]

v

o- 第二输出引脚

[0034]

v

s 源极引脚

[0035]

111、112 第一对级间节点

[0036]

113、114 第二对级间节点

[0037]

v1、v

2 第一对振荡电压

[0038]

v3、v

4 第二对振荡电压

[0039]

va1 第一变容器阵列

[0040]

va2 第二变容器阵列

[0041]

200 增益级

[0042]

210 差分对

[0043]

211、212 pmos晶体管对

[0044]

220 再生负载

[0045]

221、222 nmos晶体管对

[0046]

300 dac(数字至模拟转换器)

[0047]

301 第一pmos晶体管

[0048]

302 第二pmos晶体管

[0049]

303 串接电阻

[0050]

304 分流电容

[0051]

308 低通滤波器

[0052]

309 nmos晶体管所实现的一电流源

[0053]

310、320、330 多个开关电流单元

[0054]

311、321、331 nmos晶体管所实现的电流源

[0055]

312、322、332 nmos晶体管所实现的开关

[0056]

n

s1 加总节点

[0057]

i

s1 加总电流

[0058]

v

301 偏压

[0059]

v

302 滤波后偏压

[0060]

v

b0 栅极偏压

[0061]

i

309 固定电流

[0062]

i

310

、i

320

、i

330 多个可控电流

[0063]

w

c

[0]、w

c

[1]、w

c

[2] 粗调控制命令

[0064]

v

b1 栅极偏压

[0065]

v

dd1 第一电源供应节点

[0066]

v

dd2 第二电源供应节点

[0067]

400 变容器阵列

[0068]

401、402 节点

[0069]

410 第一变容器对

[0070]

420 第二变容器对

[0071]

430 第三变容器对

[0072]

411、421、431 第一变容器

[0073]

412、422、432 第二变容器

[0074]

v

c

[0]、v

c

[1]、v

c

[2] 控制电压

[0075]

+ 正极

[0076]

- 负极

[0077]

500 dac阵列

[0078]

510 解码器

[0079]

521、522、523 多个hs dac

[0080]

w

f0

[n-1:0]、w

f1

[n-1:0]、w

f2

[n-1:0] 已解码的n位元命令

[0081]

n 大于一的整数

[0082]

600 dac(数字至模拟转换器)

[0083]

601 电阻

[0084]

610、620、630 开关电流单元

[0085]

v

b2 栅极偏压

[0086]

w

fi

[0]、w

fi

[1]、w

fi

[2] 已解码命令

[0087]

i

610

、i

620

、i

630 电流

[0088]

n

s2 加总节点

[0089]

i

s2 加总电流

[0090]

v

c

[i] 输出电压

[0091]

611、621、631 pmos晶体管所实现的电流源

[0092]

612、622、632 pmos晶体管所实现的开关

[0093]

700 流程图

[0094]

710~760 步骤

具体实施方式

[0095]

本公开是针对数字控制振荡器。尽管本说明书公开了本公开的多个实施例可视为实施本发明的优选范例,但本发明可通过多种方式被实施,不限于后述的特定范例,也不限于用来实现所述特定范例的技术特征的特定方式。在其它例子中,已知细节未被显示或说明,以避免妨碍呈现本公开的观点。

[0096]

本技术领域技术人员可了解本公开所使用的与微电子相关的用语及基本概念,像是“电压”、“电流”、“cmos(互补式金属氧化物半导体)”、“nmos(n通道金属氧化物半导体)晶体管”、“pmos(p通道金属氧化物半导体)晶体管”、“电阻”、“电容”、“变容器”、“电阻值”、“电容值”、“电流源”、“偏压”、“节点”、“放大器”、“增益”、“共源极”、“源极随耦器”、“转导”、“负载”、“串联(series)”、“分流(shunt)”、“时钟”、“频率”、“环形振荡器”、“数字至模拟转换器”、“二极管连接式(diode-wired)”、“电流镜”、“再生负载”、“差分对”以及“负反馈”。与这些微电子的用语及基本概念类似者对本领域技术人员而言是显而易知的,故于此不再赘述。本领域技术人员当能识别nmos晶体管的符号,并能识别该符号的“源极”、“栅极”、与“漏极”。

[0097]

本公开是以一工程角度来呈现。举例而言,“x等于y”表示“x与y之间的差异小于一指定工程公差值(specified engineering tolerance)”;“x甚小于y”表示“x除以y会小于一工程公差值”;以及“x为零”表示“x小于一指定工程公差值”。

[0098]

本公开中,一信号可以是一电压或一电流,用来代表一特定信息。

[0099]

一逻辑信号是一种双态信号。该双态信号具有一高态与一低态。本文中,当一逻辑信号的电平高于(低于)属于该逻辑信号的一特定跳变点时,该逻辑信号被称为处于该高态(低态)。按逻辑信号的上下文的文意,“(该逻辑信号)x为高”是指“(该逻辑信号)x处于该高态”。

[0100]

一“时钟”是于一高态与一低态之间循环往复的一逻辑信号。

[0101]

本公开中,“v

dd”表示一电源供应节点。为便于说明,“v

dd”也可表示提供给该电源供应节点的一电源供应电压,也就是说,“v

dd

为0.9v”表示“位于该电源供应节点v

dd

的电源供应电压为0.9v”。由于一电路可能具有多个电源供应节点,它们可能具有相同或不同电压,因此一数字下标基于不同目的会被附加上去;举例而言,“v

dd1”表示一第一电源供应节点,“v

dd2”表示一第二电源供应节点,“v

dd3”表示一第三电源供应节点。值得注意的是,虽然“v

dd1”、“v

dd2”与“v

dd3”可能是不同电压,但不必然为不同电压。

[0102]

依据本公开的一实施例,图1显示一数字控制振荡器(digitally-controlled oscillator,dco)100的示意图。dco 100包含:一核心电路110,包含多个增益级,该多个增益级按一带有一负反馈的一环形形态而串接在一起,以依据一供应节点n

sup

的一供应电压v

sup

维持一振荡状态;一低速(low-speed,ls)数字至模拟转换器(digital-to-analog converter,dac)120,用来输出一供应电流i

sup

至该供应节点n

sup

,以依据一粗调控制命令(coarse control word)w

c

确定该供应电压v

sup

;一调整网络130,包含多个变容器阵列,用来依据一m维控制电压数组(m-dimensional control voltage array)v

c

[m-1:0]提供一电容性负载给该核心电路110,其中m为大于一的整数;以及一高速(high-speed,hs)dac阵列140,用来依据一细调控制命令(fine control word)w

f

输出该m维控制电压数组v

c

[m-1:0]。本说明书中,一总线标记(bus notation)用于v

c

[m-1:0]以表示v

c

[0]、v

c

[1]、v

c

[2]、

…

、v

c

[m-1]的集合(collection)。

[0103]

于一非限制性的例子中,核心电路110包含两个增益级,该两个增益级包括一第一增益级gs1与一第二增益级gs2;调整网络130包含两个变容器阵列,该两个变容器阵列包含一第一变容器阵列va1与一第二变容器阵列va2。该第一增益级gs1于第一对级间节点(inter-stage nodes)111、112分别接收第一对振荡电压v1、v2,并于第二对级间节点113、114分别输出第二对振荡电压v3、v4。该第一增益级gs2于第二对级间节点113、114分别接收第二对振荡电压v3、v4,并于第一对级间节点111、112分别输出第一对振荡电压v1、v2。该第一电容器阵列va1在该第二对级间节点113、114提供一电容性负载。该第二电容器阵列va2在该第一对级间节点111、112提供一电容性负载。多个增益级(例如:增益级gs1、gs2)按一带有负反馈的环形形态而串接在一起,以形成一环形振荡器并能维持振荡;这属于已知技术,故在此不予详述。

[0104]

于dco 100中,v1、v2、v3与v4为同一振荡频率的振荡电压,v1、v2、v3与v4的任一个可称为dco 100的一振荡信号。

[0105]

增益级gs1、gs2可由相同的功能方块来表示,每一个都包含一第一输入引脚“v

i+”、一第二输入引脚“v

i-”、一第一输出引脚“v

o+”、一第二输出引脚“v

o-”以及一源极引脚“v

s”。增益级gs1经由其“v

s”与“v

i+”与“v

i-”引脚分别接收v

sup

、v1与v2,并经由其“v

o-”与“v

o+”引脚分别输出v3与v4。增益级gs2经由其“v

s”与“v

i+”与“v

i-”引脚分别接收v

sup

、v3与v4,并经由其

“

v

o+”与“v

o-”引脚分别输出v1与v2。

[0106]

图2显示一示范性的增益级200的示意图,其可作为增益级gs1与gs2的每一个的实施例。增益级200包含:一差分对210,包括一对pmos(p通道金属氧化物半导体)晶体管211、212,其分别用来依据通过引脚“v

s”所确立的一偏压状态,从引脚“v

i+”与“v

i-”接收输入以及输出输出至引脚“v

o-”与“v

o+”;以及一再生负载220,包括一对nmos晶体管221、222按一交错耦合形态被配置。再生负载220是用来确立一负电阻值的一负载,从而确定一“右半平面极点”,其可开始一振荡运行(用于核心电路110,其一实施例为增益级200),此时差分对210是用来提供一增益,并维持该振荡运行。图2的内部连接像是“pmos晶体管211的源极、栅极与漏极分别连接至引脚v

s

、v

i+

与v

o-”,对本领域技术人员而言是不言自明的,因此细节在此省略。增益级200的延迟是由差分对210的转导值与在引脚“v

o-”与“v

o+”(across pins“v

o-”and“v

o+”,跨引脚“v

o-”and“v

o+”)的一负载电容值来决定;差分对210的转导值愈高,在引脚“v

o-”与“v

o+”的电容性负载就能愈快地被充电/放电,从而该延迟就愈短;另一方面,在引脚“v

o-”与“v

o+”的负载电容值愈大,该电容性负载被充电/放电的速度就愈慢,从而该延迟就愈长。

[0107]

如图1所示,核心电路110的一振荡频率是由增益级gs1、gs2的一延迟来决定。增益级gs1(gs2)是由它的一转导值以及在级间节点113(111)、114(112)的一电容值来决定。增益级gs1(gs2)的转导值,是由ls dac 120依据该粗调控制命令w

c

提供至该供应节点n

sup

的该供应电流i

sup

来调整,且在级间节点113(111)与114(112)的该负载电容值,是由受控于v

c

[m-1:0]的变容器阵列va1(va2)的电容值来调整,v

c

[m-1:0]是由该细调控制命令w

f

来决定。一较大(较小)供应电流i

sup

以及一较高(较低)供应电压v

sup

导致增益级gs1与gs2的一较大(较小)转导值以及一较高(较低)振荡频率。随着一启动程序,该转导值通过调整该粗调控制命令w

c

而被调整,以使该振荡频率趋近一目标值,这有效地消除工艺与电压的变化对于振荡频率的影响;之后,该粗调控制命令w

c

被固定(frozen),且该负载电容值被该细调控制命令w

f

按一闭回路方式(例如:按一锁相回路或数据回复回路)调整,从而该振荡信号的时序跟随一参考信号的时序。该转导值的调整发生于该启动程序时,且不取决于(not subject to)一高速要求。然而,抑制该供应电流i

sup

中的噪声是极需的,否则增益级gs1与gs2的延迟会受该噪声所造成的有感变化的影响。由于低速的本质,ls dac 120可采用低通滤波技术(其使得该电路减速,但在这情形下是可接受的),以抑制该供应电流i

sup

中的噪声。在另一方面,该负载电容值的调整是以一闭回路方式被执行,且取决于一高速要求。hs dac阵列140是按一方式被设计,此方式使得v

c

[m-1:0]以较快的方式去适应,同样的道理适用于变容器阵列va1、va2。

[0108]

图3显示一dac 300的示意图,可作为ls dac 120的一实施例。dac 300包含:通过nmos晶体管309所实现的一电流源,用来依据一栅极偏压v

b0

输出一固定电流i

309

至一加总节点n

s1

;多个开关电流单元包含310、320、330,用来依据w

c

[0]、w

c

[1]、w

c

[2]等等的控制,分别输出多个可控电流包含i

310

、i

320

、i

330

至该加总节点n

s1

;一第一pmos(p通道金属氧化物半导体)晶体管301,按一二极管连接式形态(diode-wired topology)被设置,以将从该加总节点n

s1

所接收的一加总电流i

s1

,转换成一偏压v

301

;一低通滤波器308,包含一串接电阻(series resistor)303与一分流电容(shunt capacitor)304,用来滤波该偏压v

301

以产生一滤波后偏压v

302

;以及一第二pmos晶体管302,用来依据该滤波后偏压v

302

输出该供应电流

i

sup

至图1的节点n

sup

。开关电流单元310(320、330)包含通过nmos晶体管311(321、331)所实现的一电流源,以及包含通过nmos晶体管312(322、332)所实现的一开关,其中nmos晶体管311(321、331)是由另一栅极偏压v

b1

所控制,nmos晶体管312(322、332)是由w

c

[0](w

c

[1]、w

c

[2])所控制。当w

c

[0](w

c

[1]、w

c

[2])为高,开关电流单元310(320、330)是处于一“开启”状态,且i

310

(i

320

、i

330

)是依据该栅极偏压v

b1

以确立。当w

c

[0](w

c

[1]、w

c

[2])为低,开关电流单元310(320、330)是处于一“关闭”状态,且i

310

(i

320

、i

330

)为零。w

c

[0]、w

c

[1]、w

c

[2]等等全为逻辑信号,共同地形成该粗调控制命令w

c

,因此,该加总电流i

s1

受控于w

c

。于一实施例中,“v

dd1”与“v

dd2”短路在一起,因此具有同样的电位;pmos晶体管301、302形成一电流镜,从而该供应电流i

sup

是依据一系数而与i

s1

成比例,其中该系数是由pmos晶体管302的w/l(宽长比)与pmos晶体管301的w/l之间的比例来决定。低通滤波器308帮忙滤净v

302

,从而滤净i

sup

。除了对低通滤波器308而言,dac 300是一典型的电流模式dac电路,其对本领域技术人员而言是不言自明的,故在此不予详述。

[0109]

值得注意的是,二极管连接式pmos晶体管301是“电流至电压转换器”的一范例,因它将二极管连接式pmos晶体管301当作一负载,以将电流i

s1

转换成电压v

301

。于一替代实施例中(未显示于图),该二极管连接式pmos晶体管301由一电阻取代,该电阻也可作为一负载。

[0110]

pmos晶体管302的配置是按一“共源极放大器”形态,其中一较高(较低)电压v

302

会导致一较小(较大)电流i

sup

。于一替代实施例中(未显示于图),pmos晶体管302由一nmos晶体管取代,并按一“源极随耦器”形态而被配置;于此替代实施例中,当该滤波后偏压v

302

上升(下降),供应电流i

sup

增加(减少),因此需要对w

c

[0]、w

c

[1]、w

c

[2]等等做一逻辑反转处理,否则对应w

c

的变化的电流i

sup

的改变方向会是相反的,基于nmos晶体管的该替代实施例可用来过滤供应噪声(v

dd1

),并提供一较干净的电源v

dd2

至该gs1/gs2级。

[0111]

一般而言,当温度升高时,一半导体电路的速度会变慢,dco 100并不例外。为了补偿因温度升高所导致的振荡速度变慢,当温度升高时,会需要一较高的供应电流i

sup

。于一实施例中,栅极偏压v

b0

与v

b1

是使用一ptat(正比于绝对温度(proportional to absolute temperature))电压产生器而被确立,从而电流i

309

与电流i

310

、i

311

、i

312

等等以及电流i

s1

与i

sup

会在温度升高时上升。这有效地减少dco 100的振荡频率因温度漂移所产生的漂移量。ptat电压产生器属于现有技术,因此细节在此不予详述。

[0112]

图4显示一变容器阵列400的示意图,其可作为电容器阵列va1与va2的每一个的实施例。电容器阵列400包含:多个变容器对,包含一第一变容器对410、一第二变容器对420、一第三变容器对430等等,分别受控于v

c

[0]、v

c

[1]、v

c

[2]等等,是按一并联形态被配置,以实现横跨两个节点401、402的一可调电容器。当作为va1(va2)的实施例时,该两个节点401、402对应节点113(111)与114(112)。这里所说的v

c

[0]、v

c

[1]、v

c

[2]等等是控制电压,共同地形成v

c

[m-1:0]。变容器对410(420、430)包含:一第一变容器411(421、431)带有一正极与一负极,该正极与该负极分别以“+”与“-”来标示,且分别连接至节点401以及v

c

[0](v

c

[1]、v

c

[2]);以及一第二变容器412(422、432)带有一正极与一负极,该正极与该负极分别以“+”与“-”来标示,且分别连接至节点402以及v

c

[0](v

c

[1]、v

c

[2])。一变容器是一电容器,其电容值由其正极与负极之间的一电压差来决定。随着控制电压v

c

[0](v

c

[1]、v

c

[2])上升(下降),变容器411(421、431)的电容值与变容器412(422、432)的电容值均会减少(增加),在节

点401、402的变容器对410(420、430)的总电容会减少(增加);因此,变容器阵列400的总电容值会减少(增加),且核心电路110的振荡频率上升(下降)。

[0113]

图5显示一dac阵列500的一功能方框图,其可作为hs dac阵列140的一实施例。hs dac阵列500包含:一解码器510,用来接收该细调控制命令w

f

,并输出多个已解码命令w

f0

、w

f1

、w

f2

等等;以及多个hs(高速)dac 521、522、523等等,分别用来依据已解码命令w

f0

、w

f1

、w

f2

等等来输出v

c

[0]、v

c

[1]、v

c

[2]等等。这里所说的w

f0

、w

f1

与w

f2

都是n位元命令(n-bit words),且分别以总线标记(bus notation)w

f0

[n-1:0]、w

f1

[n-1:0]与w

f2

[n-1:0]来表示,其中n为大于一的整数。解码器510解码w

f

,以产生w

f0

、w

f1

、w

f2

等等的总和,如下式所示:

[0114]

w

f

=w

f0

+w

f1

+w

f2

+

…

≡∑

i

w

fi

ꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

[0115]

于一第一实施例中,一温度计码被采用,从而w

f0

、w

f1

与w

f2

等等的值都是介于0与n之间,且由下列式子决定:

[0116][0117]

上式中,i=0、1、2等等,且w

fi

是依据下式以总线标记w

fi

[n-1:0]来表示:

[0118][0119]

上式中,j=0、1、2、

…

、n-1。本例中,mod(.)表示一模数操作;举例而言,mod(5,2)表示“5mod 2”,是等于1。

[0120]

举例而言,在n为4的情形下,依据式(2)、(3)所得到的表如下所示:

[0121]

w

f

w

f2

w

f2

[1:0]w

f1

w

f1

[1:0]w

f0

w

f0

[1:0]000000000000100000000001000120000000000200113000000000030111400000000004111150000010001411116000002001141111700000301114111180000041111411119100014111141111102001141111411111130111411114111112411114111141111

[0122]

于一替代实施例中,一二进位码被采用,从而w

f0

、w

f1

与w

f2

等等的值都是介于0与2

n-1

之间,且由下列式子决定:

[0123][0124]

上式中,i=0、1、2等等,且w

fi

是依据一二进位表示法以总线标记w

fi

[n-1:0]来表示。

[0125]

举例而言,在n为3的情形下,依据式(4)以及二进位表示法所得到的表如下所示:

[0126]

w

f

w

f2

w

f2

[2:0]w

f1

w

f1

[2:0]w

f0

w

f0

[2:0]0000000000000100000000100120000000020103000000003011400000000410050000100141006000020104100700003011410080000410041009100141004100102010410041001130114100410012410041004100

[0127]

值得注意的是,w

fi

[0]、w

fi

[1]、w

fi

[2]等等都是逻辑信号。

[0128]

图6显示一dac 600的示意图,其可作为hs dac 521、522、523等等的任一个的实施例。dac 600包含:多个开关电流单元610、620、630等等,用来分别依据w

fi

[0]、w

fi

[1]、w

fi

[2]等等,输出电流i

610

、i

620

、i

630

等等至一加总节点n

s2

,以形成一加总电流i

s2

;以及一电阻601,用来提供一负载给该加总节点n

s2

,以及将该加总电流i

s2

转换为一输出电压v

c

[i]。当dac 600作为hs dac 521(522、523)的实施例,v

c

[i]代表v

c

[0](v

c

[1]、v

c

[2]),此时w

fi

[0]代表w

f0

[0](w

f1

[0]、w

f2

[0]),w

fi

[1]代表w

f0

[1](w

f1

[1]、w

f2

[1]),w

fi

[2]代表w

f0

[2](w

f1

[2]、w

f2

[2])。开关电流单元610(620、630)包含一电流源与一开关,该电流源是由pmos晶体管611(621、631)来实现,其受控于一栅极偏压v

b2

,该开关由pmos晶体管612(622、632)来实现,其受控于w

fi

[0](w

fi

[1]、w

fi

[2])。当w

fi

[0](w

fi

[1]、w

fi

[2])为高,开关电流单元610(620、630)是处于一“关闭”状态,且i

610

(i

620

、i

630

)为零;当w

fi

[0](w

fi

[1]、w

fi

[2])为低,开关电流单元610(620、630)是处于一“开启”状态,且i

610

(i

620

、i

630

)是依据该栅极偏压v

b2

而确立。dac 600的速度是决定于电阻601与节点n

s2

的一寄生电容值。为了具有一高速特性,实施者可选用具有一小电阻值的电阻601。

[0129]

尽管图1显示两个变容器阵列(亦即:va1与va2)用于调整网络130,然此仅为范例,非实施限制。举例而言,若移除变容器阵列va2而保留变容器阵列va1,dco 100仍能运行;然而,若移除va2而保留va1,该两个增益级gs1与gs2会有不同负载,从而该振荡电压v1与v2的波形会与该振荡电压v3与v4的波形不同,这可能或可能不会成为问题,取决于dco 100的应

用。

[0130]

随着一启动程序,一粗调调整程序便可被执行,其中dco 100的一振荡信号(亦即:v1、v2、v3与v4的其中之一)的振荡频率被检测并与一目标值作比较。举例而言,通过使用一计数器,可检测一振荡信号的振荡频率。若该振荡频率高于(低于)该目标值,该粗调控制命令w

c

会被减量(增量)以减少(增加)该供应电流i

sup

,从而降低(提高)该供应电压v

sup

,并使得该振荡频率降低(上升)。该粗调调整程序会重复多次,以调整该振荡频率,使其趋近该目标值;然后,该粗调控制命令w

c

会被固定(frozen),且一细调调整程序会按一闭回路方式被执行,其中该振荡信号的一时序误差会被检测,且该细调控制命令w

c

会依据该时序误差而被调整。若dco 100用于一锁相回路,该时序误差是介于该振荡信号的时序与一参考时钟的时序之间的差异,且能被检测,例如被一时间至数字转换器(time-to-digital converter)检测。若dco 100是用于一时钟数据回复回路,该振荡信号的时序误差是该振荡信号的时序与根植于(embedded in)一数据信号的一时序之间的差异,且能被检测,例如被一二进位相位检测器检测。“锁相回路”、“时间至数字转换器”、“时钟数据回复回路”与“二进位相位检测器”均是本领域的现有技术,故在此不予详述。若该时序误差为正(负),这表示该振荡信号的时序是早于(迟于)预期,该细调控制命令w

f

被增量(减量)以降低(提高)v

c

[m-1:0]的电压,从而增加(减少)调整网络130的电容值,使得该振荡信号变慢(加快)。该细调控制命令w

f

依据上述方式被调整,从而最小化该振荡信号的时序与该参考时钟的时序(或根植于该数据信号的时序)之间的差异。

[0131]

dco 100的一振荡频率是由该粗调控制命令w

c

与该细调控制命令w

f

共同控制。w

c

被称为“粗调”控制命令以及w

f

被称为“细调”控制命令是一种相对概念的说明方式,也就是说,w

c

改变一单位所对应的振荡频率的改变量显著大于w

f

改变一单位所对应的振荡频率的改变量。于非限制的范例中,当w

c

被设至最小(亦即:0)时,dco 100的一振荡频率约是10ghz;w

c

是一6位元命令(按二进位表示法);由w

c

的一增量变化所导致的该振荡频率的增量改变约是50mhz;w

c

的一总调整范围约是3.2ghz;w

f

是一8位元命令(按二进位表示法);由w

f

的一增量变化所导致的该振荡频率的增量改变约是1mhz;以及w

f

的一总调整范围约是250mhz。通过使用粗调控制与细调控制的组合,可以实现一广范围高分辨率的调整。然而,当用于一闭回路时,w

c

被固定,仅有w

f

被适应性地调整。这让从属于w

c

的调整电路具有低噪声的特性(因为没有高速操作需求(high-speed requirement)),并让从属于w

f

的调整电路较快,但不会造成太多噪声(因为只涵盖一小调整范围)。据此,dco 100能同时具有高速、高分辨率与低噪声等特性。

[0132]

ls dac 120被称为“低速”而hs dac阵列140被称为“高速”是一种相对概念的说明方式,也就是说hs dac阵列140是实质地快于ls dac 120。于非限制性的范例中,w

c

的改变与dco 100的振荡频率的一相对应改变之间的一时间差约为10μs,w

f

的改变与dco 100的振荡频率的一相对应改变之间的一时间差约为1ns,换言之,hs dac阵列140约比ls dac 120快千倍。

[0133]

如图7的流程图700所示,依据本公开的一实施例的一方法包含:(step 710)使用多个增益级按一环形形态串接在一起以形成一环形振荡器,该环形振荡器用来输出一振荡信号;(step 720)使用一低速数字至模拟转换器(dac),以依据一粗调控制命令控制该环形振荡器的一供应电压;(step 730)使用受控于一控制电压数组的一变容器阵列,以于该环

形振荡器的一级间节点提供一电容性负载;(step 740)使用一高速dac阵列,以依据一细调控制命令来确定该控制电压数组;(step 750)随着一启动程序,调整该粗调控制命令,使得该振荡信号的一振荡频率趋近一目标值;以及(step 760)依据该振荡信号的一时序误差的一检测结果,按一闭回路方式调整该细调控制命令。

[0134]

虽然本发明的实施例如上所述,然而所述实施例并非用来限定本发明,本技术领域技术人员可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均可能属于本发明所寻求的专利保护范围,换言之,本发明的专利保护范围须视本说明书的权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1