信号接收器以及信号收发装置的制作方法

1.本发明涉及一种信号接收器,且特别是涉及一种信号接收器以及信号收发装置,可防止产生不必要的漏电流。

背景技术:

2.在公知常识中,在信号生发装置中,当信号接收器的电源被关闭不执行动作,而信号发射器还处于工作状态下,在信号接收器与信号发射器的连接路径间,可能产生不期望的导通路径而产生漏电电流的发生。值得注意的是,这个漏电电流的现象会造成不必要的耗电,还可能使电子装置中电路组件造成损坏。

技术实现要素:

3.本发明是针对一种信号接收器以及信号收发装置,可防止产生不必要的漏电流。

4.根据本发明的实施例,信号接收器包括终端开关对、第一电阻、第二电阻以及下拉电路。终端开关对接收操作电源。终端开关对具有共同控制端。第一电阻耦接在第一信号输入端与共同控制端间。第二电阻耦接在第二信号输入端与共同控制端间。下拉电路耦接在共同控制端与参考电压端间。下拉电路依据信号接收器的启用状态或断电状态,以决定是否下拉共同控制端上的第一控制电压至参考电压。

5.根据本发明的实施例,信号收发装置包括信号发射器以及信号接收器。信号接收器包括终端开关对、第一电阻、第二电阻以及下拉电路。终端开关对接收操作电源。终端开关对具有共同控制端。第一电阻耦接在第一信号输入端与共同控制端间。第二电阻耦接在第二信号输入端与共同控制端间。下拉电路耦接在共同控制端与参考电压端间。下拉电路依据信号接收器的启用状态或断电状态,以决定是否下拉共同控制端上的第一控制电压至参考电压。信号接收器通过第一信号输入端以及第二信号输入端耦接至信号发射器。

6.根据上述,本发明的信号接收器依据信号接收器的启用状态或断电状态,以决定是否下拉共同控制端上的第一控制电压至参考电压,可防止产生不必要的漏电流。

附图说明

7.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

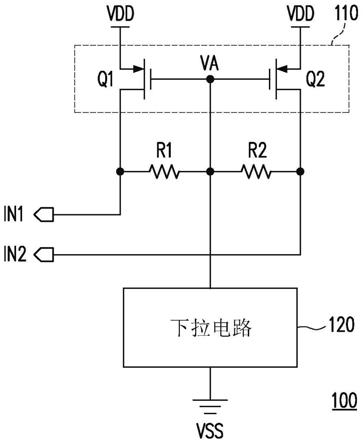

8.图1示出本发明一实施例的信号接收器的示意图;

9.图2示出本发明一实施例的信号接收器的实施方式示意图;

10.图3示出本发明一实施例的信号收发装置的示意图;

11.图4示出本发明一实施例的下拉电路的实施方式示意图。

12.附图标号说明

13.100、200、302:信号接收器;

14.110、210、310:终端开关对;

15.120、220、320、400:下拉电路;

16.301:信号发射器;

17.vdd、vdd1、vdd2:操作电源;

18.vss:参考电压;

19.va:第一控制电压;

20.vb:第二控制电压;

21.q1:第一晶体管;

22.q2:第二晶体管;

23.r1、r2、r3、r4、rc、rt1、rt2:电阻;

24.in1:第一信号输入端;

25.in2:第二信号输入端;

26.sw:开关;

27.lg:逻辑电路;

28.pdb:电源启闭状态信号。

具体实施方式

29.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在图式和描述中用来表示相同或相似部分。

30.请参照图1,图1示出本发明一实施例的信号接收器的示意图。信号接收器100包括终端开关对110、电阻r1、电阻r2以及下拉电路120。终端开关对110耦接至操作电源vdd,并且终端开关对具有共同控制端(提供第一控制电压va的端点)。电阻r1耦接在第一信号输入端in1与共同控制端间。电阻r2耦接在第二信号输入端in2与共同控制端间。下拉电路120耦接在共同控制端与参考电压端(提供参考电压vss的端点)间。并且,下拉电路120依据信号接收器100的启用状态或断电状态,以决定是否下拉共同控制端上的第一控制电压va至参考电压vss。举例而言,参考电压vss可为接地电压,但不以此为限。

31.在本实施例中,终端开关对110包括第一晶体管q1以及第二晶体管q2,但不以此为限。第一晶体管q1可具有第一端接收操作电源vdd。第一晶体管的控制端可耦接至共同控制端,并且第一晶体管q1的第二端可耦接至电阻r1。第二晶体管q2可具有第一端接收操作电源vdd。第二晶体管q2的控制端可耦接至共同控制端,并且第二晶体管q2的第二端可耦接至电阻r2。举例而言,第一晶体管q1或第二晶体管q2可为p型金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet),但不以此为限。在本实施例中,信号接收器100可通过第一信号输入端in1和第二信号输入端in2耦接至信号发射器(图未示)。

32.需要说明的是,在动作细节上,假设在信号发射器为启用状态,信号接收器100由启用状态切换至断电状态时,下拉电路120可因为信号接收器100的断电状态而被关闭。在此时,第一控制电压va由第一信号输入端in1和第二信号输入端in2上的电压所主导。基于信号发射器为启用状态,第一信号输入端in1和第二信号输入端in2的其中之一可以具有相对高的电平,并可通过电阻r1或电阻r2被提供至共同控制端而拉高第一控制电压va。以第一晶体管q1与第二晶体管q2为p型金属氧化物半导体场效晶体管为例,被拉高的第一控制

电压va可使第一晶体管q1与第二晶体管q2被截止。因此,终端开关对110则可依据共同控制端上的第一控制电压va被断开。由上述的说明可以得知,虽然信号发射器为启用状态,信号接收器100也不会产生漏电路径而发生漏电流的现象,从而避免了不必要的耗电与电路组件的损坏。

33.附带一提的,在信号接收器100为启用状态时,下拉电路120被启用,并可下拉共同控制端上第一控制电压va至参考电压vss。基于等于参考电压vss的第一控制电压va,第一晶体管q1与第二晶体管q2可被导通。也就是说,终端开关对110可依据共同控制端上的第一控制电压va被导通。因此,在信号发射器同时为启用状态下信号接收器100可通过第一信号输入端in1及第二信号输入端in2,正常地接收信号发射器所发送的信号。

34.以下请参照图2,图2示出本发明一实施例的信号接收器的实施方式示意图。信号接收器200可包括终端开关对210、电阻r1、电阻r2、电阻r3、电阻r4以及下拉电路220。

35.在本实施例中,电阻r3耦接在第一晶体管q1耦接电阻r1的路径间。电阻r4耦接在第二晶体管q2耦接电阻r2的路径间。举例而言,电阻r3及电阻r4可为50欧姆,以达到阻抗匹配的效果,避免信号的反射,但不以此为限。

36.在电路设计上,下拉电路220可包括开关sw以及逻辑电路lg。开关sw可耦接在共同控制端与参考电压端间,并且开关sw受控于第二控制电压vb。举例而言,开关sw可为n型金属氧化物半导体场效晶体管,但不以此为限。并且,逻辑电路lg可为与门(and gate),并且逻辑电路lg所执行的逻辑运算为与逻辑运算,但不以此为限。如此一来,逻辑电路lg接收电源启闭状态信号pdb以及操作电源vdd。逻辑电路lg针对电源启闭状态信号pdb以及操作电源vdd进行逻辑运算以产生第二控制电压vb。

37.具体而言,当信号接收器200为断电状态时,电源启闭状态信号pdb以及操作电源vdd均为低电平。此时,逻辑电路lg可使得第二控制电压vb为低电平,并通过为低电平的第二控制电压vb使得开关sw被断开。也就是说,下拉电路120因为信号接收器200的断电状态而被关闭。并且,第一信号输入端in1和第二信号输入端in2可分别通过电阻r1或电阻r2被提供至共同控制端而产生第一控制电压va。值得注意的是,由于信号发射器为启用状态,代表第一信号输入端in1和第二信号输入端in2为高电平,从而第一控制电压va可立刻获得高电平。接着,第一晶体管q1与第二晶体管q2依据共同控制端上的第一控制电压va被截止,终端开关对210可被断开。因此,虽然信号发射器为启用状态,也不会产生漏电路径而发生漏电流的现象,从而避免了不必要的耗电与电路组件的损坏。

38.另外,当信号接收器200为启用状态时,电源启闭状态信号pdb以及操作电源vdd均为高电平。此时,逻辑电路lg可使得第二控制电压vb为高电平,并通过为高电平的第二控制电压vb使开关sw被导通。也就是说,下拉电路220因为信号接收器200的启用状态而被启用。并且,下拉电路220可下拉共同控制端上第一控制电压va至参考电压vss。以第一晶体管q1与第二晶体管q2为p型金属氧化物半导体场效晶体管为例,被下拉的第一控制电压va可使第一晶体管q1与第二晶体管q2被导通。因此,终端开关对210可依据共同控制端上的第一控制电压va被导通。由上述的说明可以得知,当信号发射器200为启用状态时,信号接收器200可通过第一信号输入端in1及第二信号输入端in2,正常地接收信号发射器的信号。

39.再者,下拉电路220可更包括电阻rc。电阻rc耦接在开关sw的控制端(提供第二控制电压vb的端点)以及参考电压端(提供参考电压vss的端点)间。电阻rc可用以避免开关sw

的控制端浮接(floating)。

40.在本实施例中,为了避免在正常模式(信号接收器200以及信号发射器均被启用)下对信号发射器的输出端产生影响,电阻r1、r2的电阻值可以相对大于电阻r3、r4的电阻值。以电阻r3、r4的电阻值均为50欧姆为范例,电阻r1、r2的电阻值例如可以为120千欧姆。

41.以下请参照图3,图3示出本发明一实施例的信号收发装置的示意图。信号收发装置300可包括信号发射器301以及信号接收器302。关于信号接收器302的描述,可参考图1以及图2的说明,在此不多加赘述。图3与图2的差异在于,信号接收器302可通过第一信号输入端in1或第二信号输入端in2耦接至信号发射器401。值得注意的是,为了方便说明,信号发射器401经过简化为电阻rt1以及电阻rt2。举例而言,在本实施例中,第一信号输入端in1或第二信号输入端in2可分别通过电阻rt1或电阻rt2耦接至操作电源vdd1。并且,在本实施例中,信号接收器402的终端开关对410可耦接至操作电源vdd2,并且逻辑电路lg可接收电源启闭状态信号pdb以及操作电源vdd2进行逻辑运算以产生第二控制电压vb。

42.在本实施例中,在动作细节上,假设在信号发射器401为启用状态时,信号接收器402由启用状态切换至断电状态时,下拉电路420可因为信号接收器402的断电状态而被关闭。在此时,第一控制电压va由第一信号输入端in1和第二信号输入端in2上的电压所主导。基于信号发射器为启用状态,第一信号输入端in1和第二信号输入端in2的其中之一可以具有相对高的电平,并可通过电阻r1或电阻r2被提供至共同控制端而拉高第一控制电压va。以第一晶体管q1与第二晶体管q2为p型金属氧化物半导体场效晶体管为例,被拉高的第一控制电压va可使第一晶体管q1与第二晶体管q2被截止。因此,终端开关对410则可依据共同控制端上的第一控制电压va被断开。由上述的说明可以得知,虽然信号发射器401为启用状态,也不会产生漏电路径而发生漏电流的现象,从而避免了不必要的耗电与电路组件的损坏。

43.以下请参照图1及图4,图4示出本发明一实施例的下拉电路的实施方式示意图。下拉电路400可包括开关sw以及逻辑电路lg。开关sw可耦接在共同控制端与参考电压端间,并且开关sw受控于第二控制电压vb。在本实施例中,开关sw可为p型金属氧化物半导体场效晶体管,但不以此为限。并且,逻辑电路lg可为与非门(nand gate),并且逻辑运算为与非逻辑运算,但不以此为限。如此一来,逻辑电路lg接收电源启闭状态信号pdb以及操作电源vdd。逻辑电路lg针对电源启闭状态信号pdb以及操作电源vdd进行逻辑运算以产生第二控制电压vb。

44.具体而言,当信号接收器100为断电状态时,电源启闭状态信号pdb以及操作电源vdd均为低电平。此时,逻辑电路lg可使得第二控制电压vb为高电平,并通过为高电平的第二控制电压vb使得开关sw被断开。并且,第一信号输入端in1和第二信号输入端in2可分别通过电阻r1或电阻r2被提供至共同控制端而产生第一控制电压va。接着,第一晶体管q1与第二晶体管q2依据共同控制端上的第一控制电压va被截止,终端开关对110可被断开。因此,虽然信号发射器为启用状态,也不会产生漏电路径而发生漏电流的现象,从而避免了不必要的耗电与电路组件的损坏。

45.另外,当信号接收器100为启用状态时,电源启闭状态信号pdb以及操作电源vdd均为高电平。此时,逻辑电路lg可使得第二控制电压vb为低电平,并通过为低电平的低电平的第二控制电压vb使开关sw被导通。也就是说,下拉电路400因为信号接收器100的启用状态

而被启用。并且,下拉电路400可下拉共同控制端上第一控制电压va至参考电压vss。以第一晶体管q1与第二晶体管q2为p型金属氧化物半导体场效晶体管为例,被下拉的第一控制电压va可使第一晶体管q1与第二晶体管q2被导通。因此,终端开关对110可依据共同控制端上的第一控制电压va被导通。由上述的说明可以得知,当信号发射器100为启用状态时,信号接收器100可通过第一信号输入端in1及第二信号输入端in2,正常地接收信号发射器的信号。

46.再者,下拉电路400可更包括电阻rc。电阻rc耦接在开关sw的控制端(提供第二控制电压vb的端点)以及操作电源端(提供操作电源vdd的端点)vdd间。电阻rc可用以避免开关sw的控制端浮接。

47.根据上述,本发明的信号接收器以及信号收发装置,在信号发射器为启用状态下,信号接收器的下拉电路依据信号接收器的启用状态或断电状态,以决定是否下拉共同控制端上的第一控制电压至参考电压。如此一来,当信号发射器为启用状态时,信号接收器不会产生漏电路径而发生漏电流的现象,从而避免了不必要的耗电与电路组件的损坏。

48.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1