相位内插装置及其时钟信号选择器的制作方法

1.本发明涉及一种相位内插装置及其时钟信号选择器,特别是涉及一种在时钟信号进行切换时,可防止产生不必要的假信号(glitch)。

背景技术:

2.请参照图1,图1示出的公知技术中,执行时钟信号切换动作的波形图。其中,例如在相位内插装置的技术领域中,常需要在相位不相同的时钟信号间进行切换。在图1中,当选中时钟信号mxclk需由选择时钟信号clk《0》切换为时钟信号clk《1》时,公知技术领域常根据时钟信号clk《0》发生转态点的时间点t1以作为执行时钟信号切换动作的设定时间点。在这样的条件下,在公知技术领域中,可能因为执行时钟信号切换动作的选择器的瞬时效应,使得在时间点t1、t2间,部分的时钟信号clk《0》通过选择器以在选中时钟信号mxclk上产生假信号gs,并可能造成相位内插装置的执行动作发生异常。

技术实现要素:

3.本发明是针对一种相位内插装置及其时钟信号选择器,可避免在时钟信号切换动作中产生假信号。

4.根据本发明的实施例,时钟信号选择器包括选择器以及选择信号产生器。选择器接收不同相位的多个时钟信号。选择器根据选择信号以选择时钟信号的其中之一以产生选中时钟信号。选择信号产生器耦接选择器,产生选择信号。其中,当选择器由选择第一时钟信号为选中时钟信号,变更为选择第二时钟信号为选中时钟信号时,选择信号产生器根据第一时钟信号以及第二时钟信号中相位较落后者的转态点以产生设定时间点,并根据设定时间点来产生选择信号。

5.根据本发明的实施例,相位内插装置包括n级选择器、选择信号产生器以及内插运算电路。n级选择器的每一者接收具有不同相位的多个时钟信号。n级选择器分别接收n个选择信号,分别根据n个选择信号以分别产生具有不同相位的n级选中时钟信号,n为大于1的整数。其中第i级选中时钟信号的相位超前第i+1级选中时钟信号的相位,i为小于n的正整数。选择信号产生器用以产生n个选择信号,其中选择信号产生器根据第i+m级的选中时钟信号以产生第i级的选择信号,其中m大于或等于1。内插运算电路针对n级选中时钟信号中的其中之二进行内插运算,以产生输出时钟信号。

6.根据上述,本发明的时钟信号选择器根据执行时中信号切换动作的第一时钟信号以及第二时钟信号中相位较落后者的转态点来设定执行时钟信号切换动作的设定时机点,并经此以防止时钟信号切换动作中,因第一时钟信号、第二时钟信号转态未完成而发生假信号,避免相位内插装置产生物动作的现象。

附图说明

7.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部

分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

8.图1示出的公知技术中,执行时钟信号切换动作的波形图;

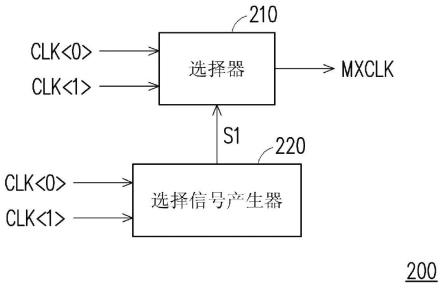

9.图2示出本发明实施例的时钟信号选择器的示意图;

10.图3a、3b示出的本发明实施例的时钟信号选择器的动作波形图;

11.图4示出本发明另一实施例的相位内插装置的示意图;

12.图5a至图5c示出本发明实施例的相位内插装置的动作波形图;

13.图6示出本发明另一实施例的相位内插装置的示意图。

14.附图标号说明

15.200:时钟信号选择器;

16.210、411~413、611~613:选择器;

17.220:选择信号产生器;

18.400、600:相位内插装置;

19.420、620:选择信号产生器;

20.430、630:内插运算电路;

21.clk《0》~clk《3》:时钟信号;

22.gs:假信号;

23.m1~m3、mxclk:选中时钟信号;

24.mxclk选中时钟信号;

25.out:输出时钟信号;

26.s1、s2、sel:选择信号;

27.t1~t5:时间点;

28.v1、v2、v3:电压值。

具体实施方式

29.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在图式和描述中用来表示相同或相似部分。

30.请参照图2,图2示出本发明实施例的时钟信号选择器的示意图。时钟信号选择器200包括选择器210以及选择信号产生器220。选择器210接收不同相位的多个时钟信号clk《0》以及clk《1》。选择器210并根据选择信号s1以选择时钟信号clk《0》以及clk《1》的其中之一以产生选中时钟信号mxclk。选择信号产生器220耦接至选择器210,并用以产生选择信号s1。在本实施例中,当选择器210由选择时钟信号clk《0》为选中时钟信号mxclk,变更为选择时钟信号clk《1》为选中时钟信号mxclk时,或者,当选择器210由选择时钟信号clk《1》为选中时钟信号mxclk,变更为选择时钟信号clk《0》为选中时钟信号mxclk时,选择信号产生器220可根据时钟信号clk《0》以及时钟信号clk《1》中相位较落后者的转态点以产生设定时间点,并根据所述设定时间点来产生选择信号s1。

31.在本实施例中,时钟信号clk《0》的相位可超前时钟信号clk《1》的相位。在实施细节中,请同步参照图3a、3b示出的本发明实施例的时钟信号选择器的动作波形图。在图3a中,当时钟信号选择器200要使选中时钟信号mxclk由时钟信号clk《0》切换为时钟信号clk《1》时(相位前进模式),选择信号产生器220可根据时钟信号clk《0》的转态点(时间点t2)的

一延迟时间后的时间点来作为设定时间点,例如以时钟信号clk《1》的转态点来作为设定时间点。在本实施例中,选择信号产生器220可根据相位较落后的时钟信号clk《1》转态至高电压值的时间点t3来做为设定时间点。选择信号产生器220通过使选择信号s1在设定时间点(时间点t3)前为第一电压值v1,并使选择信号s1在设定时间点(时间点t3)后为第二电压值v2。选择器210可根据为第一电压值v1的选择信号s1,以在设定时间点(时间点t3)前选择时钟信号clk《0》来产生选中时钟信号mxclk,并在设定时间点(时间点t3)后,根据为第二电压值v2的选择信号s1来选择时钟信号clk《1》以产生选中时钟信号mxclk。

32.在此可以发现,在选择信号s1发生电压值变换的设定时间点上,时钟信号clk《0》以及clk《1》均已转态至稳定的电压值。因此,在设定时间点上执行时钟信号clk《0》以及clk《1》间的切换动作,可以使选中时钟信号mxclk不会产生假信号。

33.在图3b中,当时钟信号选择器200在相位后退模式下时,时钟信号选择器200使选中时钟信号mxclk由时钟信号clk《1》切换为时钟信号clk《0》时,选择信号产生器220可根据时钟信号clk《1》的转态点(时间点t4)来作为设定时间点。选择信号产生器220通过使选择信号s1在设定时间点(时间点t4)前为第二电压值v2,并使选择信号s1在设定时间点(时间点t4)后为第一电压值v1。选择器210可根据为第二电压值v2的选择信号s1,以在设定时间点(时间点t4)前选择时钟信号clk《1》来产生选中时钟信号mxclk,并在设定时间点(时间点t4)后,根据为第一电压值v1的选择信号s1来选择时钟信号clk《0》以产生选中时钟信号mxclk。

34.在此可以发现,同样的,在选择信号s1发生电压值变换的设定时间点上,时钟信号clk《0》以及clk《1》均已转态至稳定的电压值。因此,在设定时间点上执行时钟信号clk《0》以及clk《1》间的切换动作,可以使选中时钟信号mxclk不会产生假信号。

35.在本实施例的另一实施方式中,选择信号产生器220可以不将设定时间点设定在时间点t4上,而可以根据相位相对落后的时钟信号clk《1》的转态点(时间点t4)的一延迟时间后的时间点(例如时间点t5)来作为设定时间点。也可使选中时钟信号mxclk不会产生假信号。

36.附带一提的,第一电压值v1以及第二电压值v2可以分别是不同的逻辑值。且第一电压值v1以及第二电压值v2不相同,但第一电压值v1以及第二电压值v2的大小关系并没有一定的限定。在本发明其他实施例中,第一电压值v1也可以大于第二电压值v2。

37.此外,本发明实施例中的选择器210也可接收三个或三个以上的时钟信号。选择器210并可针对多个时钟信号的其中之二进行选择上的切换,并产生选中时钟信号mxclk。其中,选择信号产生器220可以根据被选择的第一时钟信号以及第二时钟信号中相位较落后者的转态点以产生设定时间点,并产生选择信号s1。选择器210则可根据选择信号s1来选择第一时钟信号以及第二时钟信号以产生mxclk。在这样的实施方式中,选择器210可根据分别对应多个时钟信号的选择信号s1的多个电压值来执行时钟信号的选择动作。此外,选择信号s1也可以利用数字的方式来实施,也就是说,选择信号s1可以为具有多个位的数字信号。选择信号s1可具有多个逻辑值,以分别对应多个时钟信号。

38.此外,本发明实施例中的选择器210可以通过本领域的普通技术人员所熟知的多路复用器电路来实施,没有特别的规定。选择信号产生器220则可以利用数字电路来实施,例如,选择信号产生器220可设置正反器(例如d型正反器)来进行时钟信号clk《0》、clk《1》

的转态点的检测,并根据检测结果来产生选择信号。

39.以下请参照图4,图4示出本发明另一实施例的相位内插装置的示意图。相位内插装置400包括多级选择器411~413、选择信号产生器420以及内插运算电路430。选择器411~413的每一者均接收时钟信号clk《0》~clk《3》,其中,时钟信号clk《0》~clk《3》依序具有一相位差。其中第一级的时钟信号clk《0》的相位超前第二级的时钟信号clk《1》,第二级的时钟信号clk《1》的相位则超前第三级的时钟信号clk《2》,第三级的时钟信号clk《2》的相位则超前第四级的时钟信号clk《3》。选择器411~413分别接收选择信号s1、s2、s2,并分别产生选中时钟信号m1~m3。

40.选择信号产生器420用以产生选择信号s1、s2。其中选择信号产生器420根据第2级的选中时钟信号m2以产生第1级的选择信号s1,并根据第3级的选中时钟信号m3以产生第2级的选择信号s2。值得一提的,第3级(最后一级)的选择器413根据前一级的(第2级)的选择信号s2来产生第3级的选中时钟信号m3。

41.选择器411、412分别产生的选中时钟信号m1、m2可提供给内插运算电路430。内插运算电路430用以针对选中时钟信号m1、m2执行内插运算,以产生输出时钟信号out。

42.附带一提的,本发明实施例的内插运算电路430可应用本领域的普通技术人员所熟知的任一时钟信号的内插电路来实施,没有特殊的限定。此外,本实施例中选择器411~413的数量以及时钟信号clk《0》~clk《3》的数量,都只是为了方便说明所提出的范例,并不用以限缩本发明的范畴。设计者可根据实际需求来变更选择器411~413的数量以及时钟信号clk《0》~clk《3》的数量,没有固定的限制。

43.在动作细节上,请同步参照图4、图5a至图5c,其中图5a至图5c示出本发明实施例的相位内插装置的动作波形图。在图5a以及图5b中,在相位前进模式下,相位内插装置500中的选择器411~413由分别选择时钟信号clk《0》、clk《1》、clk《2》以分别作为选中时钟信号m1~m3,变更为分别选择时钟信号clk《1》、clk《2》、clk《3》以分别作为选中时钟信号m1~m3。此时,在图5a中,针对选择器411,选择信号产生器420可根据选择器412产生的选中时钟信号m2来产生选择信号s1。基于此时选择器412产生的选中时钟信号m2等于时钟信号clk《1》,因此,选择信号产生器420可设定时钟信号clk《1》的转态点(时间点t3)为设定时间点,并根据这个设定时间点来产生选择信号s1。细节上,选择信号产生器420可在时间点t3前使选择信号s1为第一电压值v1,并在时间点t3后使选择信号s1为第二电压值v2。如此一来,在时间点t3前,选择器411可根据为第一电压值v1的选择信号s1来选择时钟信号ck《0》为选中时钟信号m1,并在时间点t3后,根据为第二电压值v2的选择信号s1来选择时钟信号ck《1》为选中时钟信号m1。

44.在另一方面,在图5b中,针对选择器412,选择信号产生器420可根据选择器413产生的选中时钟信号m3来产生选择信号s2。基于此时选择器413产生的选中时钟信号m3等于时钟信号clk《2》,因此,选择信号产生器420可设定时钟信号clk《2》的转态点(时间点t4)为设定时间点,并根据这个设定时间点来产生选择信号s2。细节上,选择信号产生器420可在时间点t4前使选择信号s2为第三电压值v3,并在时间点t4后使选择信号s2为第四电压值v4如此一来,在时间点t4前,选择器412可根据为第三电压值v3的选择信号s2来选择时钟信号ck《1》为选中时钟信号m2,并在时间点t4后,根据为第四电压值v4的选择信号s2来选择时钟信号ck《2》为选中时钟信号m2。

45.上述的第一电压值v1至第四电压值v4也可通过不同的第一逻辑值至第四逻辑值来实施。

46.另外,在图5c中,在相位后退模式下,相位内插装置400中的选择器411~413由分别选择时钟信号clk《1》、clk《2》、clk《3》以分别作为选中时钟信号m1~m3,变更为分别选择时钟信号clk《0》、clk《1》、clk《2》以分别作为选中时钟信号m1~m3。其中,针对选择器411,选择信号产生器420可根据选择器412产生的选中时钟信号m2来产生选择信号s1。基于此时选择器412产生的选中时钟信号m2等于时钟信号clk《2》,因此,选择信号产生器420可设定时钟信号clk《2》的转态点(时间点t4)为设定时间点,并根据这个设定时间点来产生选择信号s1。细节上,选择信号产生器420可在时间点t4前使选择信号s1为第二电压值v2,并在时间点t4后使选择信号s1为第一电压值v1。如此一来,在时间点t4前,选择器411可根据为第二电压值v2的选择信号s1来选择时钟信号ck《1》为选中时钟信号m1,并在时间点t4后,根据为第一电压值v1的选择信号s1来选择时钟信号ck《0》为选中时钟信号m1。

47.在上述的说明中,时钟信号clk《0》~clk《3》间的切换动作,都是在时钟信号转态并维持在稳定的电压值下才执行,故切换动作中,可使选中时钟信号上不会产生假信号的现象。

48.以下请参照图6,图6示出本发明另一实施例的相位内插装置的示意图。相位内插装置600包括多级的选择器611~613、选择信号产生器620以及内插运算电路630。选择器611~613的每一者均接收具有不同相位的时钟信号clk《0》~clk《3》。其中第一级的时钟信号clk《0》的相位超前第二级的时钟信号clk《1》,第二级的时钟信号clk《1》的相位则超前第三级的时钟信号clk《2》,第三级的时钟信号clk《2》的相位则超前第四级的时钟信号clk《3》。选择器611~613分别产生选中时钟信号m1~m3,其中选中时钟信号m1、m2被传送至内插运算电路630。内插运算电路630可针对选中时钟信号m1、m2执行内插运算,并产生输出时钟信号out。

49.与图4的实施不相同的,选择器611~613接收相同的选择信号sel。而选择信号产生器620则根据选中时钟信号m1~m3中,具有最大延迟相位的选中时钟信号m3来产生。也就是说,选择器611~613均在延迟足够长的时间后,来执行时钟信号间的切换动作,可有效防止假信号的产生。

50.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1