一种数字功率发射芯片的阻抗调制系统及方法

1.本发明属于无线通信技术领域,具体涉及一种直接功率输出数字发射芯片的阻抗调制系统及其调制方法。

背景技术:

2.为了满足无线通信、空间互联网、认知无线电等需求,宽带、多带以及多种模式会同时并存,集成芯片实现可重构、高效率已成为了微波发射机的必然要求,而微波功率放大器数字化是实现这些需求的有效技术途径。数字功率放大器在微波开关功率放大器基础上,结合功率编码信号处理,实现全数字微波功率放大(power dac)。

3.在数字功率发射芯片中,使用数字功率放大器(digital power amplifiers,简称dpa或数字功放)阵列代替了传统发射机中的数字模拟转换器、混频器单元和功率放大器,实现基带信号直接到射频信号的上变频和功率放大。随着通信系统中不断引入高阶调制和复用调制技术,使得发射机的动态范围和输出精度要求越来越高。数字功率放大器作为新兴的数字发射机方案,发展出包含大量功率放大器单元的数字功率放大器阵列以满足需求。然而在大动态范围信号激励下,数字功放阵列的等效输入阻抗和等效输出阻抗变化巨大,极易产生阻抗失配现象,进而影响数字发射机效率。

4.而传统的数字发射芯片中鲜有关注上面提出的问题,数字功放阵列与前后级之间直接连接,或是匹配网络一般在设计时已经固定,并且是不可调节的。如a.balteanu(a.baltean u et al.,"a 2

‑

bit,24dbm,millimeter

‑

wave soi cmos power

‑

dac cell for watt

‑

level hi gh

‑

efficiency,fully digital m

‑

ary qam transmitters,"in ieee journal of solid

‑

state circui ts,vol.48,no.5,pp.1126

‑

1137,may 2013,doi:10.1109/jssc.2013.2252752.)等人的研究中,功放差分输出直接接入差分贴片天线。

5.因此,对数字功放阵列的输入、输出阻抗进行阻抗调制,解决大动态范围信号激励下数字发射机中阻抗失配问题,对于进一步提升数字发射机性能极为重要。

技术实现要素:

6.针对背景技术所存在的问题,本发明的目的在于提供一种数字功率发射芯片的阻抗调制系统及其调制方法。该系统分别通过调整多级驱动的功率分配网络和可重构输出匹配网络,实现芯片中数字功放阵列的输入、输出阻抗,与前级输出阻抗、负载阻抗之间的良好匹配,同时通过功率控制信号控制数字功率放大器的状态,使得发射芯片热管理更为有效,大大提升芯片的热可靠性。

7.为实现上述目的,本发明的技术方案如下:

8.一种数字功率发射芯片的阻抗调制系统,包括驱动功率分配网络、数字功放阵列、可重构输出匹配网络和数字控制模块;

9.所述驱动功率分配网络由n级驱动功率分配子单元级联形成,每一级驱动功率分配子单元包括功率分配模块和与功率分配模块连接的若干路驱动功率放大器,第n级的功

率分配模块的输入和第n

‑

1级的驱动功率放大器的输出相连接,第n级驱动功率放大器的输出连接数字功放阵列中高均匀权重(即most significant bit,msb)数字功放阵列的输入;

10.所述数字功放阵列包括高均匀权重数字功放阵列和低非均匀权重(即least significant bi t,lsb)数字功放阵列;所述高均匀权重数字功放阵列由m个数字功放子阵列组成,每个数字功放子阵列包含相同数目的数字功率放大器;所述低非均匀权重数字功放阵列包括若干个数字功率放大器和耦合单元;

11.所述可重构输出匹配网络用于实现数字功放阵列输出阻抗与数字发射芯片的负载阻抗之间的匹配,以及对数字功放阵列的输出进行功率合成,包括依次连接的输出预匹配单元、功率合成单元和可变参数元件匹配单元;所述输出预匹配单元用于对数字功放阵列的输出阻抗进行预匹配,功率合成单元将各个数字功放子阵列的输出进行功率合成,可变参数元件匹配单元对数字发射芯片的负载阻抗作调制;

12.所述数字控制模块用于对基带信号量化编码得到功率编码信号,从而实现对驱动功率分配网络、数字功放阵列和可重构输出匹配网络的控制,即数字控制模块对基带信号量化编码得到功率编码信号,再将该信号转码为功率控制信号a~a"、静态电压控制信号b、b'和可变参数控制信号c;其中,功率控制信号a~a"用于控制驱动功率分配网络中驱动功率放大器的工作状态,静态电压控制信号b、b'分别为数字功放阵列中的高均匀权重数字功放和低非均匀权重数字功放提供有效偏置,可变参数控制信号c控制可重构输出匹配网络中的可变参数元件匹配单元;

13.相位调制信号分别输入驱动功率分配网络中第一级驱动功率分配子单元的功率分配模块,和数字功放阵列的低非均匀权重数字功放阵列;其中,驱动功率分配网络中的功率分配模块用于将输入的相位调制信号作等功率分配,然后驱动功率放大器将信号进行功率放大,最后输出至高均匀权重数字功放阵列,同时驱动功率分配网络对高均匀权重数字功放阵列的输入阻抗进行调制;高均匀权重数字功放阵列用于在功率控制信号的控制下对相位调制信号作幅度调制,获得包含功率控制信号高位幅度信息的幅相调制信号,然后输出至可重构输出匹配网络的预匹配单元,经阻抗匹配后输入至功率合成单元;低非均匀权重数字功放阵列用于在功率控制信号的控制下对相位调制信号作幅度调制,获得包含功率控制信号低位幅度信息的幅相调制信号,输入至功率合成单元;功率合成单元将合成后的功率信号输入至可变参数元件匹配单元,然后送至发射芯片负载或天线。

14.进一步地,除第一级驱动功率分配子单元外的其它级驱动功率分配子单元中,与功率分配模块连接的驱动功率放大器的路数可以相同或不同。

15.进一步地,末级驱动功率放大器的总数等于数字功放阵列中所有高均匀权重数字功放的数目,末级驱动功率分配子单元的个数等于高均匀权重数字功放子阵列的个数,每个末级驱动功率分配子单元中包含的驱动功率放大器数目等于单个高均匀权重数字功放子阵列中数字功放的数目。

16.进一步地,所述功率分配模块除了对输入信号作若干路等功率分配外,还能够实现在后接的驱动功率放大器通断状态改变的情况下,使自身的输入阻抗保持稳定;所述驱动功率放大器用于为下一级的功率分配模块或者数字功放阵列提供合适的输入功率,其工作状态受到数字控制模块的控制。

17.进一步地,高均匀权重数字功放阵列中的m个数字功放子阵列在版图上布局具有

对称性,用于避免出现芯片局部过热导致芯片性能恶化和可靠性降低的现象。

18.一种数字功率发射芯片阻抗调制的方法,该方法包括:

19.数字控制模块对基带信号量化编码得到功率编码信号,再将该信号转码为功率控制信号a~a"、静态电压控制信号b、b'和可变参数控制信号c;其中,功率控制信号a~a"用于控制驱动功率分配网络中驱动功率放大器的工作状态,静态电压控制信号b、b'分别为数字功放阵列中的高均匀权重数字功放和低非均匀权重数字功放提供有效偏置,可变参数控制信号c控制可重构输出匹配网络中的可变参数元件匹配单元;

20.功率控制信号a~a"控制驱动功率分配网络,实现输入阻抗的匹配,具体过程为:每一级驱动功率分配子单元中驱动功率放大器的开通和关断分别受到功率控制信号a~a"控制,每个驱动功率放大器对应功率控制信号a~a"的一位;高均匀权重数字功放阵列中的每个数字功放的开通和关断,与之相连的末级驱动功率分配子单元中驱动功率放大器通断情况保持一致;

21.静态电压控制信号b,其位数与高均匀权重的数字功放数量相等,一位对应一个数字功放;若数字功放处于开通状态时,静态电压控制信号b为该数字功放提供有效偏置,同时,控制数字功放前级对应的驱动功率放大器开通;若数字功放处于关断状态时,静态电压控制信号b置于不能为数字功放提供偏置的无效电平,同时,控制数字功放前级相应的驱动功率放大器关闭;以上两步可以确保每个高均匀权重数字功放准确处于开通/关断状态;

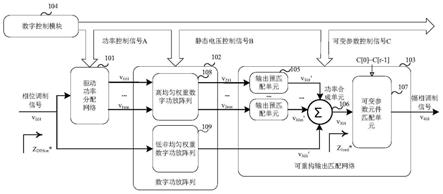

22.和静态电压控制信号b控制规律相同,静态电压控制信号b'每一位为一个低非均匀权重的数字功放提供有效偏置。

23.可变参数控制信号c调整可变参数元件匹配单元,改变该单元对发射芯片负载阻抗变换值,进而改变了可变参数元件匹配单元的输入阻抗,实现输出匹配阻抗调制的微调;输出预匹配单元与可变参数元件匹配单元共同实现了对数字功放阵列输出阻抗调制的功能,以此,使得数字发射芯片的负载阻抗与数字功放阵列的输出阻抗之间保持良好的匹配。

24.进一步地,数字控制模块将h位功率编码信号转码为静态电压控制信号b、b'采用移动温度编码的方式;其中,功率编码信号的高h位转码为静态电压控制信号b,用于控制处于开通状态的高均匀权重的数字功放均匀地分布在各个数字功放子阵列中;功率编码信号剩下的低h

‑

h位无需转码,即等于静态电压控制信号b',直接用于控制低非均匀权重的数字功放。

25.进一步,所述移动温度编码,类似于温度编码。温度编码是将步长为1的递进的二进制原码,译码为从低位到高位逐位变1的温度码,但是移动温度编码译码的结果是,每隔n

‑

1位变1(n为单个数字功放子阵列中包含的高均匀权重数字功放的数量);即从最低位(第0位)算起,按间隔n

‑

1位从低位往高位方向数,则第n位作为下一个变1的位,以此类推;若某一位往最高位数不足n位,则数到最高位后,跳到最低位继续数。

26.进一步地,功率控制信号a~a"需要控制n级驱动功率放大器;第k

‑

1级驱动功率分配子单元中每个驱动功率放大器的控制码字,可以取其后所接的第k级中所有驱动功率放大器的控制码字的或;即,当第k级驱动功率分配子单元中有一个驱动功率放大器处于开通状态时,其对应的第k

‑

1级的驱动功率放大器一定开通;末级驱动功率分配子单元中驱动功率放大器的控制码字,与静态电压控制信号b相同。

27.进一步地,功率控制信号a~a"控制处于开通状态的数字功放,使其相对均匀地分

布在各个数字功放子阵列中,从而使得每一个末级驱动功率分配子单元所带负载保持相等,并且使处于开通状态的数字功放均匀地分布在芯片版图四周,提高芯片的散热面积,避免出现芯片局部过热导致性能恶化和可靠性降低的现象。

28.进一步地,可变参数控制信号c通过控制可变参数元件匹配单元中元件的可变参数,从而控制该网络对芯片负载的阻抗变换值。

29.综上所述,由于采用了上述技术方案,本发明的有益效果是:

30.本发明通过多级驱动的功率分配网络对数字功放阵列的输入阻抗进行调制,使得输出功率发生变化时阻抗变化值限制在一个较小的范围内;同时利用可重构输出匹配网络对数字发射机负载阻抗进行调制,使得其与数字功放阵列的输出阻抗更好地匹配。因此,本发明方案解决了大动态范围信号激励下,数字功率发射芯片的输入/输出阻抗匹配网络的设计难度陡增的问题,并使得芯片的热管理更为有效,提升了数字发射机效率。

附图说明

31.图1为本发明数字功率发射芯片阻抗调制系统框图。

32.图2为本发明中多级驱动功率分配网络级联示意图。

33.图3为本发明中初级驱动功率分配子单元框图。

34.图4为本发明中高均匀权重数字功放阵列结构框图。

35.图5为本发明中低非均匀权重数字功放阵列结构框图。

36.图6为本发明数字功率发射芯片阻抗调制方法框图。

37.图7为本发明实施例中功率分配模块采用的巴伦结构示意图。

38.图8为本发明实施例中初级驱动功分子单元前级的单端转差分模块框图。

39.图9为本发明实施例中输出预匹配单元结构框图。

40.图10为本发明实施例中开关电容匹配网络框图。

41.图11为本发明实施例中开关电容阵列2框图。

具体实施方式

42.为使本发明的目的、技术方案和优点更加清楚,下面结合实施方式和附图,对本发明作进一步地详细描述。

43.实施例1

44.本发明实施例提供一种应用于4bit msb和4bit lsb的数字功率发射芯片的阻抗调制系统,其框图如图1所示,包括驱动功率分配网络101、数字功放阵列102、可重构输出匹配网络103和数字控制模块104;

45.所述驱动功率分配网络101由n级驱动功率分配子单元(简称驱动功分子单元)串联形成,级联示意图如图2所示,每一级驱动功分子单元包括功率分配模块和与功率分配模块连接的若干路驱动功率放大器(简称驱放),第n级的功率分配模块的输入和第n

‑

1级的驱放的输出相连接。本实施例中级数n=2,初级驱动功分子单元201的框图如图3所示,功率分配模块301采用巴伦结构,该巴伦将从端口1'输入的相位调制信号分成4路等功率的信号(t=4),分别送入4路驱放,每一路驱放从端口1"~4"输出,分别接一个第二级驱动功分子单元;4个第二级(也是本例中的末级)驱动功分子单元202的结构,均与初级驱动功分子单元

相同,其中第二级驱放的输出(4个第二级子单元共16路输出)接图4所示的高均匀权重数字功放子阵列401~404的输入。驱放的作用是为下一级的驱动功分子单元或者数字功放阵列提供合适的输入功率。

46.值得注意的是,每级子单元中的功率分配模块301不仅限于采用巴伦结构实现。所述巴伦结构如图7所示,采用差分输入、差分输出形式,因此在初级驱动功分子单元的前级,还需加入一个如图8所示的单端转差分模块,用于将输入的单端相位调制信号转换为差分信号;另外巴伦后所接驱放也采用差分结构。该巴伦除了对输入信号作4路等功率分配外,还能够实现在后接的驱放通断状态改变的情况下,限制自身的输入阻抗保持稳定。

47.所述数字功放阵列102采用差分结构,包括高均匀权重数字功放阵列108和低非均匀权重数字功放阵列109。其中,高均匀权重数字功放阵列由m个子阵列组成,如图4所示(m=4)401~404,其中每个子阵列包含4个高均匀权重差分数字功放(n=4),故数字功放的总数为16;低非均匀权重数字功放阵列包含4个非均匀权重的差分数字功放和一个耦合单元,其结构如图5所示。

48.图2中末级驱动功分子单元中的驱放302的输出(共16路)的每一路,接高均匀权重数字功放子阵列401~404中的一个均匀权重的差分数字功放,而低非均匀权重差分数字功放子阵列的输入直接由相位调制信号提供,高均匀权重数字功放子阵列的输出接图1中的可重构输出匹配网络103。

49.数字功放阵列102的输入阻抗经过多级驱动的功率分配网络101后得到调制。如图3所示,驱动功分子单元等效为一个多端口网络,输入端口为功率分配模块的输入,输出端口为t路驱放的输出。数字功放阵列的中高均匀权重数字功放的输入阻抗,为末级驱动功分子单元20n中驱放的等效负载;同理,在多级驱放链路中,后级驱动功分子单元的输入阻抗,为前级驱动功分子单元的等效负载。每级驱动功分子单元对其等效负载作阻抗变换,由此数字功放子阵列的输入阻抗经过驱动功率分配网络逐级得到调制,最终表现为驱动功率分配网络101的输入端阻抗,如图1中所标示的z

dpain*

。而低非均匀权重数字功放因为功率相对较小,对数字功放阵列的输入阻抗调制影响相对不大。

50.当基带信号功率变化时,控制处于开通状态的高均匀权重数字功放,使其相对均匀地分布在各个子阵列中,从而让各个末级的驱动功分子单元所负荷的等效负载相当,进而使各个末级子单元的输入阻抗相当,以此类推;最终使得初级驱动功分子单元中各个驱放所负荷的等效负载相当,此时再经过功率分配模块后,驱动功率分配网络输入阻抗值的变化能够限制在一个小范围内,便于与该网络前级的输出阻抗之间保持良好的匹配。

51.所述可重构输出匹配网络103用于实现数字功放阵列输出阻抗与数字发射芯片的负载阻抗之间的匹配,以及对数字功放阵列的输出进行功率合成;其结构如图1所示,包括依次连接的输出预匹配单元105、功率合成单元106和可变参数元件匹配单元107。本实施例中,输出预匹配单元105用于对数字功放阵列的输出阻抗进行预匹配,其结构如图9所示,高均匀权重数字功放子阵列的中,各路差分数字功放的输出分别接一个marchand巴伦,该结构实现阻抗调制的功能;各路marchand巴伦的输出再经过一个耦合单元,输出至功率合成单元106;

52.功率合成单元106将各个数字功放子阵列的输出进行功率合成后输出至可变参数元件匹配单元107。功率合成单元也可以采用图7所示的巴伦结构,将输入和输出端口互换

即可变换成四路差分合成一路差分的功率合成结构,每个高均匀权重数字功放子阵列的输出采用一个该合成结构进行合成,最后再将四个子阵列的四路合成信号再经过一个该合成结构合成为一路功率信号。低非均匀权重数字功放阵列的输出可以直接连接到最终的合成功率信号。

53.可变参数元件匹配单元107对数字发射芯片的负载阻抗作调制,采用开关电容阵列结合传输线构成,其结构如图10所示。功率合成信号v

301

经过传输线1001,输入开关电容阵列1002,再经过传输线1003后,输出到发射芯片负载。开关电容阵列1002由r条支路并联而成,每条支路由一个定值电容和一个开关电容串联得到。其中,r个开关电容受到r位的可变参数控制信号c控制,一个开关电容对应信号c中的一位。值得注意的是,图10中所示的传输线1001和1003的具体结构可以不相同。开关电容阵列1002除了采用图10中所示的开关电容阵列1以外,还可以采用图11中1101所示的开关电容阵列2。该电路由一个巴伦变压器和r个开关电容并联组成,同样地,每个开关电容也受r位的可变参数控制信号c中相应一位控制。

54.此外也可以采用所属领域技术人员们所了解的其他结构,并不局限于本实施例所列举的两个电路。

55.为了说明可重构输出匹配网络103中阻抗变换的原理,详细描述如下:负载阻抗经过可变参数元件匹配单元获得变换后,即成为如图1所示信号v

301

处阻抗z

load*

。对于功率合成单元106,信号v

301

处电流值为信号v

301

'~v

30m

'处电流之和,而在电压相同的情况下,信号v

301

'~v

30m

'处阻抗值可达信号v

301

处阻抗值的x倍(x等于信号v

301

处的电流大小与信号v

301

'~v

30m

'处电流大小的比值),即z

load*

的x倍。为使信号v

301

'~v

30m

'处阻抗xz

load*

与高均匀权重数字功放的理想负载阻抗r

opt

保持一致,通过输出预匹配单元对其进行变换。r

opt

可通过对数字功放进行负载牵引等方法得到。而低非均匀权重数字功放因为输出电流相对较小,对v

301

处阻抗值影响相对不大。

56.所述数字控制模块104用于对基带信号量化编码得到h位功率编码信号,从而实现对驱动功率分配网络、数字功放阵列和可重构匹配网络的控制,具体为:数字控制模块将功率编码信号转码为静态电压控制信号b,采用移动温度编码的方式,只需功率编码信号的高h位。转码后静态电压控制信号b的功能是,控制处于开通状态的高均匀权重的数字功放,均匀地分布在各个数字功放子阵列中。功率编码信号剩下的低h

‑

h位无需转码,即等于静态电压控制信号b',直接用于控制低非均匀权重的数字功放。

57.发明还提供一种基于上述阻抗调制系统的阻抗调制的方法,该方法框图如图6所示,具体包括:

58.数字控制模块104对基带信号量化编码得到8位的功率编码信号,再将该信号转码为功率控制信号a、a'、静态电压控制信号b、b'和可变参数控制信号c;其中,功率控制信号a、a'控制驱动功率分配网络中驱放的开通和关断,静态电压控制信号b、b'分别为数字功放阵列中的高均匀权重差分数字功放和低非均匀权重差分数字功放提供有效偏置,可变参数控制信号c控制可变参数元件匹配单元中的开关电容。

59.功率控制信号a~a'控制驱动功率分配网络101,实现输入阻抗的匹配。进一步,如图2所示的驱动功分子单元201~202(n=2)中,每个驱放的开通和关断受到功率控制信号a、a'中相应的一位控制。比如,初级驱动功分子单元201中的巴伦将输入分成四路输出(t=

4),巴伦后接的4个驱放,分别受a[0]~a[3]控制;第一个第二级驱动功分子单元202中的巴伦将输入分成4路输出,巴伦后接的4个驱放,分别受a'[0]~a'[3]控制;第二个第二级驱动功分子单元中4个驱放,分别受a'[4]~a'[7]控制。

[0060]

数字功放阵列102具体结构如图4、图5所示(m=4,n=4)。高均匀权重差分数字功放的输入接第二级驱动功分子单元202中驱放的输出(共16路),其中每个差分数字功放的开通和关断状态,受其前级的驱放通断情况影响。差分数字功放的偏置受静态电压控制信号b、b'码字的相应一位控制。比如,高均匀权重差分数字功放子阵列1的偏置受静态电压控制信号码字b[00]~b[03]控制,子阵列2偏置受静态电压控制信号码字b[10]~b[13]控制,以此类推。

[0061]

所述高均匀权重差分数字功放的开通和关断状态,和与之相连的末级驱动功分子单元中驱放通断情况保持一致,如图4所示,数字功放子阵列401~404中的差分数字功放开通时,通过静态电压控制信号b为该差分数字功放提供有效偏置;同时,控制其前级驱放开通。若差分数字功放处于关断状态时,静态电压控制信号b置于低电平;同时,控制其前级驱放关闭。以上两步可以确保每对高均匀权重差分功放处于开通/关断状态。

[0062]

数字功放子阵列的输入阻抗经过多级驱动的功率分配网络101得到调制。如图3所示,每级驱动功分子单元可以等效为一个5(t=4)端口的网络。其中,输入端口为巴伦的输入,输出端口为4路驱放的输出。第二级驱动功分子单元的每个输出端口对应接入图中数字功放子阵列401~404中的一个差分数字功放,数字功放子阵列的输入阻抗即为第二级驱动功分子单元202的等效负载;同理,第二级驱动功分子单元的输入阻抗为初级驱动功分子单元201的等效负载。数字功放子阵列的输入阻抗经过第二级驱动功分子单元202获得阻抗变换,表现为第二级驱动功分单元202的输入阻抗;同理,第二级驱动功分单元202的输入阻抗经过初级驱动功分单元201获得阻抗变换,最终,表现为驱动功分网络102的输入端阻抗,即图1中所示的z

dpain*

。

[0063]

当基带信号功率变化时,控制处于开通状态的高均匀权重差分数字功放,使其均匀地分布在图4中所示的4个子阵列401~404(m=4)中,其序号分别为1、2、3、4,比如使导通的差分功放依次位于子阵列1、4、3、2、1、4、3、2、

……

中,使第二级的4个驱动功分子单元所负荷的等效负载相当,而它们结构相同,即使得它们的输入阻抗相当。进而,对于初级驱动功分子单元201来说,其中每个驱放所负荷的等效负载相当,此时再结合巴伦结构,使初级驱动功分子单元201输入阻抗值的变化保持在一个较小的范围。最终,数字功放阵列102的输入阻抗经驱动功率分配网络101阻抗变换后,与前级输出阻抗之间保持良好的匹配。同时,功率控制信号a~a"控制处于开通状态的差分功放,使其均匀地分布在图4中所示的4个子阵列401~404中,令处于开通状态下的差分数字功放较为均匀地分布在电路版图的上,例如使开通的功放依次位于子阵列1、4、3、2、1、4、3、2、

……

中,每个子阵列中,处于开通状态下的差分数字功放数目相当,进而提高芯片的散热面积,避免出现芯片局部过热导致性能恶化和可靠性降低的现象。

[0064]

如图10所示,在输出预匹配单元工作的同时,可变参数控制信号c调整开关电容阵列1002的电容值,改变发射芯片负载阻抗经过该阵列和传输线得到的阻抗变换值,如图1所示的z

load*

,进而改变了信号v

301

'~v

30m

'处阻抗xz

load*

,实现输出匹配阻抗调制的微调。

[0065]

其中,数字控制模块将功率编码信号转码为静态电压控制信号b,采用移动温度编

码方式。本例中设计功率编码信号为8位,转码采用其高4位,剩下的低4位作为静态电压控制信号b',直接用于控制低非均匀权重的数字功放。所述移动温度编码,将步长为1的递进的二进制原码,译码为每隔3位变1的移动温度码。即从最低位(第0位)算起,按间隔3位从低位往高位方向数,则第4位作为下一个变1的位,以此类推;若某一位往最高位数不足4位,则数到最高位后,跳到最低位继续数。如,功率编码信号高4位为0101时,转码结果为001 0001 0001 0011;高4位为0110时,转码结果为001 0001 0011 0011。

[0066]

本实施例中移动温度编码方式的真值表如表1所示。

[0067]

表1

[0068][0069]

功率控制信号a需要控制2(n=2)级驱放。初级驱动功分子单元为一分四路驱动功分单元,设其中的4个驱放分别为a、b、c、d。第二级驱动功分子单元为4个相同的一分四路驱动功分单元,设其分别为单元p、q、u、v,其中驱放的控制字分别为a'[0]~a'[3]、a'[4]~a'[7]、a'[8]~a'[11]、a'[12]~a'[15](m=4,n=4),与静态电压控制信号b相同。单元p对应初级驱动功分单元中的驱放a,驱放a的控制字a[0],取单元p中驱放的控制字a'[0]~a'[3]的或。比如,功率编码信号高4位为0101时,信号b为001 0001 0001 0011,则a'[0]~a'[3]为0011,a'[4]~a'[7]为0001,a'[8]~a'[11]为0001,a'[12]~a'[15]为0001;则a[0]取a'

[0]~a'[3]的或,即为1。

[0070]

可变参数控制信号c共有r位,采用温度编码的形式,所需开关电容阵列容值大时,则使得更多的开关电容接通;所需开关电容阵列容值小时,则使得更多的开关电容断开。所需开关电容阵列容值根据对芯片的负载阻抗变换时的具体需求确定。

[0071]

以上所述,仅为本发明的具体实施方式,本说明书中所公开的任一特征,除非特别叙述,均可被其他等效或具有类似目的的替代特征加以替换;所公开的所有特征、或所有方法或过程中的步骤,除了互相排斥的特征和/或步骤以外,均可以任何方式组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1