一种采用正激变换原理的电磁锁驱动装置的制作方法

1.本实用新型属于电磁锁及感性负载驱动的技术领域,具体地说是涉及一种采用正激变换原理的电磁锁驱动装置。

背景技术:

2.电磁锁作为一种执行器件,被广泛的应用于各种控制系统中。小功率(100w以下)电磁锁通常采用低压(不大于36v)、直流供电,驱动较为简单,通常采用达灵顿管、三极管、或小型继电器就可驱动;中大功率(100w及以上)如果仍然采用低压供电,则电流较大(达到3a及以上),这对于三极管、小型继电器的通流量就有较高的要求;这时通常会提高供电电压(100v及以上)。电压升高,但驱动的三极管的v

ce

和小型继电器接点的耐压通常较小,这时通常采用mos来驱动。

3.如果电磁锁在吸起保持时段仍然提供与吸起时段相同的功率,则电磁锁的电磁线圈发热较为严重,这极大的降低了电磁锁的可靠性和寿命。但实验中发现电磁锁在吸起后,只需要提供比吸起阶段小得多的功率,就可使电磁锁可靠的处于吸起保持状态。根据这一特点,可采用功率调节技术,即电压调节。当电磁阀吸起后,适当降低电磁线圈的供电电压,使其能可靠的保持在吸起状态即可,以降低电磁阀的发热量。为了实现这一需求,通常采用继电器或固态继电器,使用两套驱动电路:一套控制、驱动高压,用于吸起时段;一套控制、驱动低压,用于吸起保持时段。当需要电磁锁吸起时,先打开高压驱动、控制电路,输出高功率,使电磁锁可靠吸起;当电磁锁吸起后,先切断高压输出,然后再打开低压驱动、控制电路,输出较低的功率,使电磁阀吸起保持。而采用mos来控制和驱动技术,就能很好解决这一问题:只用一套控制和驱动电路,通过调节mos控制信号的占空比,使其在吸起时段输出高占空比的电压,使电磁锁可靠吸起;当电磁锁吸起后,再输出低占空比的电压,使电磁阀吸起保持。这样就很好地实现了这个需求。

4.按控制电磁锁的供电位置,分为低边控制和高边控制。mos的低边控制较为简单,对于nmos来说,由于s极(源极)通常是接驱动电源的地(gnd),所以只需要通过预驱电路(三极管或预驱芯片)在nmos的g端(栅极)对gnd提供10v左右的电压,就可打开nmos。但采用这种方式时,电磁锁的“+”(正极)与驱动电源的“+”(正极)相连,电磁锁的

“‑”

(负极)与nmos的d极(漏极)相连。这样,当nmos的ds之间未导通时,电磁锁虽处于电源未接通状态,但仍将保持很高的电压(与驱动电源电压相同),这存在较大的触电和漏电风险。而高边控制能最大程度降低这一风险。因为采用高边控制时,电磁锁的

“‑”

(负端)是与gnd相连的,在nmos关断时,电磁锁的电位为gnd,处于安全电压。但高边控制稍显复杂,需要采用自举电路,这可采用高边驱动芯片或正激变换电路来实现。

5.另外,由于电磁锁在通电和关断瞬间,会产生较大的干扰,如果将控制部分和驱动部分共地,则电磁锁将干扰控制部分,对控制部分的可靠性和稳定性带来极大考验。这就需要采用隔离技术。而正激变换电路由正激变压器等构成,将源级(低压控制侧)和次级(高压驱动侧)隔离开来,很好地实现了这个需求。

技术实现要素:

6.本实用新型的目的是提供一种具有可靠性高、安全性高、成本低,釆用正激变换原理的电磁锁驱动装置。

7.为解决上述问题,本实用新型的技术方案是:涉及一种采用正激变换原理的电磁锁驱动装置,其特征是:包括正激变换电路(和mos驱动电路)、电磁锁电路,正激变换电路的输出端电连接电磁锁电路的电磁锁线圈。

8.所述的正激变换电路包括脉冲发生电路、门级驱动电路、正激变压器和输出滤波电路,脉冲发生电路输出端与驱动电路输入端电连接,驱动电路输出端与正激变压器初级端电连接,正激变压器次级端与输出滤波电路输入端电连接,输出滤波电路输出端电连接电磁锁电路的驱动端。

9.所述的脉冲发生电路包括cpu和与门电路, cpu产生两路频率脉冲,一路频率为50k~100khz、占空比为30~70%,最佳为80khz、40%占空比;另一路频率为500~5khz 、占空比为0~100%,最佳为1.0khz,占空比根据电磁锁的吸起和吸起保持的参数而定;与门将两路脉冲合成,生成间歇式脉冲信号;当然,也可不需要与门,由cpu直接产生最后所需的间歇式脉冲信号,只是算法会复杂些。

10.所述的门级驱动电路包括第一电阻、带光耦隔离的门级驱动器、第二电阻、第三电阻、第一电容、nmos、 npn三极管,第四电阻、第一整流二极管;与门电路输出端通过第一电阻到带光耦隔离的门级驱动器发光管的负端,发光管的正端接电源,带光耦隔离的门级驱动器光电接收端构成达林顿管输出,输出通过第二电阻到第三电阻、npn三极管集电极和nmos的栅极g形成的连接点,第三电阻另一端与地端gnd电连接,nmos的漏极分两路,一路与地端gnd电连接,另一路与正激变压器输入两绕组与12v的连接点连接;输入两绕组匝数多的一组另一端与地端gnd电连接,输入两绕组匝数少的一组另一端与第一整流二极管正端电连接;nmos的源极分两路,一路与npn三极管基极电连接,另一路通过第四电阻到地端gnd。

11.所述的输出滤波电路包括:第二整流二极管、电感、第一二极管、第二电容、第五电阻、稳压二极管;第二整流二极管、电感、第一二极管、第二电容构成标准的正激式整流滤波电路,在第二电容并联有第五电阻和稳压二极管,稳压二极管正端与电磁锁电路电连接。

12.所述的电磁锁电路包括:第六电阻、第二nmos、电磁锁线圈、第二二极管;第二nmos漏极与hvdc电连接,第二nmos漏极源极通过电磁锁线圈、第二二极管到hvgnd电连接,电磁锁线圈、第二二极管并联连接,第二nmos栅极和第二nmos漏极源极与输出滤波电路输出端电连接。

13.综上所述,本实用新型具有以下特点和优点:

14.(1)电压高、寿命长:本电路的输出电压可达100v以上,甚至可高达600v,且mos是电子开关,具有开关频率高、响应快、寿命长等特点。而三极管或继电器很难实现这一特点。

15.(2)电压可调:本电路通过改变占空比的方式来实现电压可调,实现了电磁锁的吸起时段和吸起保持时段的电压不同的要求,从而解决电磁锁的发热量大的问题,进而提高了电磁锁的寿命。

16.(3)高边控制:本电路的输出为采用高边控制,使电磁锁在断电时处于零电位,可有效降低漏电和触点风险。

17.(4)隔离:本电路具有两级隔离:带光耦的门级驱动为第一级隔离,正激变压器为第二级隔离。两级隔离将cpu电路、门级驱动电路、高压驱动电路三者之间彼此隔离,极大的提高了电路的抗干扰性和稳定性。

18.下面结合实施例及附图对本实用新型作进一步说明。

附图说明

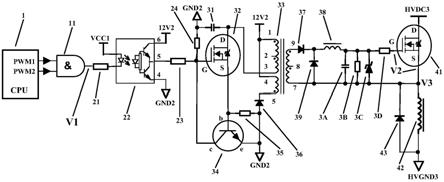

19.图1是本实用新型的电路原理图;

20.图2是电路有关测试点的波形图。

21.图中,1、cpu;11、与门;21、第一电阻、22、带光耦隔离的门级驱动器;23、第二电阻;24、第三电阻;31、第一电容;32、nmos;33、正激变压器;34、npn三极管;35、第四电阻;36、第一整流二极管;37、第二整流二极管;38、电感;39、第一二极管;3a、第二电容;3b、第五电阻;3c、稳压二极管;3d、第六电阻;41、nmos;42、电磁锁线圈;43、第二二极管。

具体实施方式

22.为进一步阐述本实用新型达成预定目的所采取的技术手段及功效,以下结合附图及实施例对本实用新型的具体实施方式、结构特征及其功效,详细说明如下。

23.如图1所示,本实用新型涉及一种采用正激变换原理的电磁锁驱动装置,其特征是:包括正激变换电路(和mos驱动电路)、电磁锁电路,正激变换电路的输出端电连接电磁锁电路的电磁锁线圈42。

24.所述的正激变换电路包括脉冲发生电路、驱动电路和正激变压器33和输出滤波电路,脉冲发生电路输出端与门级驱动电路输入端电连接,门级驱动电路输出端与正激变压器33初级端电连接,正激变压器33次级端与输出滤波电路输入端电连接,输出滤波电路输出端电连接电磁锁电路的驱动端。

25.所述的脉冲发生电路包括cpu1和与门电路11, cpu1产生两路频率脉冲,一路频率为50k~100khz、占空比为30~70%,最佳为80khz、40%占空比;另一路频率为500~5khz 、占空比为0~100%,最佳为1.0khz,占空比根据电磁锁的吸起和吸起保持的参数而定;与门11将两路脉冲合成,形成间歇式脉冲信号。当然,也可不需要与门11,由cpu1直接产生最后所需的间歇式脉冲信号。

26.所述的脉冲发生电路包括cpu1,cpu1输出频率为50k~100khz、占空比为30~70%和频率为500~5khz 、占空比为0~100%两信号与叠加。

27.所述的门级驱动电路包括第一电阻21、带光耦隔离的门级驱动器22、第二电阻23、第三电阻24、第一电容31、nmos32、 npn三极管34,第四电阻35、第一整流二极管36;与门电路11输出端通过第一电阻21到带光耦隔离的门级驱动器22发光管的负端,发光管的正端接电源,带光耦隔离的门级驱动器22光电接收端构成达林顿管输出,输出通过第二电阻23到第三电阻24、npn三极管34集电极和nmos32的栅极g形成的连接点,第三电阻24另一端与地端gnd2电连接,nmos32的漏极分两路,一路与地端gnd2电连接,另一路与正激变压器33输入两绕组与12v的连接点连接;输入两绕组匝数多的一组另一端与地端gnd2电连接,输入两绕组匝数少的一组另一端与第一整流二极管36正端电连接。nmos32的源极分两路,一路与npn三极管34基极电连接,另一路通过第四电阻35到地端gnd2。

28.所述的输出滤波电路包括:第二整流二极管37、电感38、第一二极管39、第二电容3a、第五电阻3b、稳压二极管3c;第二整流二极管37、电感38、第一二极管39、第二电容3a构成标准的正激式整流滤波电路,在第二电容3a并联有第五电阻3b和稳压二极管3c,稳压二极管3c正端与电磁锁电路电连接。

29.所述的电磁锁电路包括:第六电阻3d、第二nmos41、电磁锁线圈42、第二二极管43;第二nmos41漏极与hvdc3电连接,第二nmos41漏极源极通过电磁锁线圈42、第二二极管43到hvgnd3电连接,电磁锁线圈42、第二二极管43并联连接,第二nmos41栅极和第二nmos41源极与输出滤波电路输出端电连接。

30.图2中,电路有关测试点,pwm1为cpu的载频脉冲输出;pwm2为cpu的低频脉冲输出;v1为pwm1和pwm2经过与门后的输出;v2为41(nmos)的g和s之间的电压(v

gs

);v3为最终输出到电磁锁线圈上的电压。

31.电路工作原理为:当需要控制电磁锁42吸起时,cpu(单片机、arm、dsp等) 1通过片上的pwm(脉宽调制器)或定时器等资源,输出两路频率脉冲pwm1和pwm2,pwm1的频率为80khz(范围为50k~100khz),占空比为40%(范围为30~70%);pwm2频率为1.0khz(范围为500~5khz),占空比为50%(范围为0~100%);两路脉冲经过与门 11合成,得到波形为v1的脉冲,它是80khz的间歇式脉冲;该脉冲经过限流电阻21输入至带光耦隔离的门级驱动器22,22的输出经过限流电阻23、分压电阻24,输入至小功率开关nmos 32的栅极(g),使32工作在开关状态;正激变压器33在nmos 32的导通、关断的激励下,将能量耦合、传递到次级,经过整流二极管37、电感38、续流二极管39、滤波电容3a,生成一个约幅值为10v、1.0khz、50%占空比的脉冲电压,此电压经过负载电阻3b、保护稳压二极管3c、限流电阻3d,加在高压、大功率nmos 41的g、s两端,得到幅值为hvdc3(最高可达600v)、1.0khz、50%占空比的电压波形v3,该电压加在电磁锁的电磁线圈42上,使其吸合。43为续流二极管,nmos 41在关断时,电磁锁线圈42会产生反电动势,通过43进行泄放,以防止击穿nmos 41。

32.电阻35为采样电阻,在异常情况下,当通过nmos 32的d、s的电流过大,当采样电阻35上的采样电压超过0.7v时,保护npn三极管34的c,e导通,使nmos 32的g(栅极)点的电压拉到0v,使nmos 32关断,起到保护nmos 32的作用。

33.通常,电磁锁在吸起时需要较高的电压,可将pwm2的占空比提高(通常为90%以上),使其可靠吸起;吸起后,如果仍然保持电压不变,则电磁锁发热会比较严重,严重影响电磁锁的工作和寿命。此时可将pwm2的占空比降低(通常为50%以下),使其仍能可靠保持在吸起状态。这样,就可只用一套电路,有效解决电磁锁在吸起保持时段的发热严重的问题。

34.nmos 41的d、s之间耐压hvdc3可高达600v,所以,该电路可实现较高的电压控制;nmos 41是电子开关,无触点,所以寿命长。

35.nmos 41驱动电磁阀采用高边控制,在关断时,电磁锁处于零电位,可有效降低漏电和触电风险。

36.整个电路有两级隔离,第一级隔离为带光耦的门级驱动器,第二级隔离为正激变压器。两级隔离将cpu电路、驱动电路、高压驱动电路三者之间彼此隔离,极大的提高了电路的抗干扰性和稳定性。

37.另外,由于正激变压器只能耦合脉冲信号,与门11和前级输出的任何固定电平(恒高或恒低)将无法使后级的正激变换电路耦合、输出能量,也无法最终打开nmos 41、驱动电

磁锁,防止电磁锁误动。所以该电路具还有较高安全特性。

38.本实用新型中cpu或是单片机或是arm或dsp。

39.以上内容是结合具体的优选实施方式对本实用新型所作的进一步详细说明,不能认定本实用新型的具体实施只局限于这些说明。对于本实用新型所属技术领域的普通技术人员来说,在不脱离本实用新型构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1