电子装置的制作方法

[0001]

本申请是有关于一种电子装置,特别是有关于一种具有显示面板的电子装置。

背景技术:

[0002]

近年来,由于市场的需求,非矩形显示器逐渐兴起。显示器厂商可根据客户的需求,提供不同形状的显示面板。然而,非矩形显示面板的缺点在于,面板内每条扫描线的长度可能不同,并且不同的扫描线可能跨越不同数量的数据线。此外,不同的数据线可能具有不同的长度,并且不同的数据线可能跨越不同数量的扫描线。因此,造成显示器的画面不均匀。

技术实现要素:

[0003]

本申请提供一种电子装置,包括一基板、一第一栅极电路、一第二栅极电路、一信号线以及一屏蔽层。基板包括一显示区及一周边区。第一栅极电路位于周边区。第二栅极电路位于周边区。信号线耦接于第一栅极电路与第二栅极电路之间,并具有一特定线段。特定线段与显示区重叠。屏蔽层位于显示区之中,并重叠特定线段。

附图说明

[0004]

为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

[0005]

图1为本申请的电子装置的一实施例的示意图。

[0006]

图2为本申请的电子装置的另一实施例的示意图。

[0007]

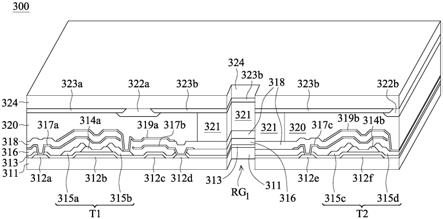

图3为本申请的电子装置的一实施例的结构示意图。

[0008]

图4a为本申请的电子装置的另一实施例的结构示意图。

[0009]

图4b为本申请的电子装置的另一实施例的结构示意图。

[0010]

图5为本申请的电子装置的另一实施例的结构示意图。

[0011]

图6为本申请的栅极电路的一实施例的示意图。

[0012]

图中元件标号说明:

[0013]

100、200、300、400a、400b、500:电子装置;

[0014]

110、210:基板

[0015]

620:显示面板;

[0016]

121~124、221~226、610:栅极电路;

[0017]

131~134、231~234:数据电路;

[0018]

140~160、240~280:信号线组;

[0019]

111、211、621:显示区;

[0020]

112、212:周边区;

[0021]

141~143、161~163:信号线;

[0022]

sg1~sg6、312c、412c、522d:特定线段;

[0023]

rg1、rg2:镂空区域:

[0024]

scn1~scn5、sl1~sl4:扫描线;

[0025]

311、411、511:下基板;

[0026]

312a、312b、312d~312f、315a~315d、317a、317c、412a、412b、412d~412f、415a~415d、418a、418b、418d、418e、516a、516c、516d、516f、519a~519d、522a~522c、522e~522g、524a、524b、524d、524e:电极;

[0027]

516b、516e:通道层

[0028]

319a、319b、416a、416b、526a、526b:像素电极;

[0029]

317b、418c、524c:屏蔽层;

[0030]

313、316、318、417、413、513~515、517、520、521、525:绝缘层;

[0031]

314a、314b、414a、414b:半导体层;

[0032]

t1~t6:晶体管;

[0033]

320、419、527:显示介质层;

[0034]

321、420、581:框胶;

[0035]

322a、322b、421a、421b、528a、528b:彩色滤光层;

[0036]

323a、323b、422a、422b、529a、529b:黑色矩阵;

[0037]

324、423、530:上基板;

[0038]

dis:距离;

[0039]

512a~512d:遮光层;

[0040]

518a~518d:栅极介电层;

[0041]

523:平坦层;

[0042]

611:控制电路;

[0043]

612~615:驱动元件;

[0044]

g1~g4:栅极信号;

[0045]

clk:时脉信号。

具体实施方式

[0046]

为让本申请的目的、特征和优点能更明显易懂,下文特举出实施例,并配合所附附图,做详细的说明。本申请说明书提供不同的实施例来说明本申请不同实施方式的技术特征。其中,实施例中的各元件的配置为说明之用,并非用以限制本申请。另外,实施例中附图标号的部分重复,是为了简化说明,并非意指不同实施例之间的关联性。

[0047]

再者,说明书与权利要求书中所使用的序数例如“第一”、“第二”等的用词,以修饰权利要求书的元件,其本身并不意含及代表该请求元件有任何之前的序数,也不代表某一请求元件与另一请求元件的顺序、或是制造方法上的顺序,这些序数的使用仅用来使具有某命名的一请求元件得以和另一具有相同命名的请求元件能作出清楚区分。

[0048]

图1为本申请的电子装置的一实施例的示意图。如图所示,电子装置100包括一基板110、栅极电路121~124、数据电路131~134以及信号线140~160。本申请并不限定电子装置100的种类。在一实施例中,电子装置100可包括显示装置、天线装置、感测装置或拼接

装置,但不以此为限。在其它实施例中,电子装置100可为可弯折或可挠式电子装置。在一些实施例中,电子装置100可例如包括液晶显示器(liquid crystal display,lcd)或是发光二极管显示器。在本申请中,发光二极管可例如包括有机发光二极管(organic light emitting diode,oled)、次毫米发光二极管(mini led)、微发光二极管(micro led)或量子点发光二极管(quantum dot light emitting diode,qled或qdled)。在其它实施例中,发光二极管包括萤光(fluorescence)材料、磷光(phosphor)材料或其他适合的材料或上述材料的组合,但不以此为限。在一实施例中,天线装置可例如是液晶天线,但不以此为限。另外,拼接装置可例如是显示器拼接装置或天线拼接装置,但不以此为限。需注意的是,电子装置可为前述的任意排列组合,但不以此为限。下文将以显示面板做为电子装置或拼接装置以说明本申请内容,但本申请不以此为限。

[0049]

电子装置100的基板110为一非矩形基板,并包括一显示区111及一周边区112。在本实施例中,显示区111的形状为一非矩形形状。栅极电路121~124位于显示区111外侧的周边区112,用以传送信号至显示区111内的扫描线。在一些实施例中,栅极电路121~124直接形成于基板110上,故该电子装置所使用的栅极电路121~124架构可称为gop(gate on panel)架构。在一些实施例中,栅极电路121~124的两者耦接同一扫描线的两端。举例而言,栅极电路121耦接一扫描线的右端,而栅极电路122耦接该扫描线的左端。在一些实施例中,栅极电路121~124耦接不同的扫描线。栅极电路通过扫描线传送扫描信号,以控制与扫描线耦接的像素的开启或关闭状态。

[0050]

数据电路131~134也位于周边区112,用以提供影像信号予显示区111内的数据线。在一些实施例中,数据电路131~134的封装是采用一薄膜覆晶(chip on film,cof)技术或是一玻璃覆晶(chip on glass,cog)技术。

[0051]

信号线组140~160分别耦接于两栅极电路之间,用以传送控制信号(如时脉信号、电源、重置信号)。在本实施例中,信号线组140~160各自具有多条信号线。以信号线组140为例,信号线组140具有信号线141~143。信号线141~143的一端与栅极电路121相连。信号线141~143的另一端与栅极电路122相连,但本申请并不以此为限。

[0052]

由于非矩形显示面板的显示区111的形状为非矩形,为了配合显示区111的形状,栅极电路121~124需围绕显示区111而设置。同样地,数据电路131~134也需围绕显示区111而设置。如图1所示,在一些实施例中,会因为面板外形设计使得栅极电路间的信号线无法设置于周边区112,或是数据电路131~134的至少一者可设置在两栅极电路之间,使得栅极电路之间的信号线需穿过显示区111。

[0053]

以栅极电路121及122为例,由于数据电路131设置于栅极电路121与122之间,故栅极电路121与122之间的信号线组140穿过显示区111。在本实施例中,信号线141~143穿过显示区111或是与显示区111重叠的线段称为特定线段sg1~sg3。换句话说,信号线141的长度大于或等于特定线段sg1的长度。相似的,数据电路132位于栅极电路123与124之间,故连接栅极电路123与124的信号线组160延伸进入显示区111。在本实施例中,信号线组160的信号线161~163的特定线段sg4~sg6位于显示区111之中。相似的,在本申请中各信号线的长度也分别大于或等于所对应的特定线段的长度。

[0054]

另外,在栅极电路122与123之间并不具有数据电路,故耦接栅极电路122及123的信号线组150可在非显示区112中延伸,而未进入显示区111。

~sg6的任一者)。电极312d用以接收一固定电压,如一接地电压或是一共通电压。电极312e为另一共通电极,用以接收共通电压或接地电压。电极312f为另一栅极。

[0061]

绝缘层313重叠312a、312b、312d~312f以及特定线段312c,用以电性隔离312a、312b、312d~312f以及特定线段312c。在本实施例中,绝缘层313直接接触例如部分的下基板311。半导体层314a及314b设置于绝缘层313之上。在本实施例中,半导体层314a重叠电极312b,并且半导体层314b重叠电极312f。

[0062]

电极315a及315b部分重叠半导体层314a。在本实例中,半导体层314a、电极315a、315b、312b构成一晶体管(transistor)t1。电极315a作为晶体管t1的漏极(drain)。电极315b作为晶体管t1的源极(source),电极312b作为晶体管t1的栅极。而在一些实施例中,电极315a作为晶体管t1的源极,电极315b作为晶体管t1的漏极。

[0063]

类似的,电极315c及315d部分重叠半导体层314b。在本实例中,半导体层314b、电极315c、315d、312f构成一晶体管t2。电极315c作为晶体管t2的漏极,电极315d作为晶体管t2的源极,电极312f作为晶体管t2的栅极。而在一些实施例中,电极315c作为晶体管t2的源极,电极315d作为晶体管t2的漏极。但本申请中,晶体管t1与t2的结构并不以此为限。另外,本申请并不限定晶体管t1与t2的材料。在本申请中,晶体管t1或t2可包含a-si,ltps,igzo或其他适合的材料,而多个tft之间可包含相同的半导体材料或不同的半导体材料。

[0064]

绝缘层316重叠电极315a~315d以及半导体层314a、314b。在本实施例中,绝缘层316直接接触例如部分的绝缘层313。电极317a、317c以及一屏蔽层(shielding layer)317b设置于绝缘层316之上。在本实施例中,电极317a作为一共通电极(common electrode),重叠电极315a、315b以及半导体层314a,并电性连接电极312a。屏蔽层317b重叠特定线段312c,用以减少特定线段312c的电场对其它电极或走线的影响。在本实施例中,屏蔽层317b电性连接电极312d,用以接收一固定电压,例如一接地电压或是一共通电压。电极317c也作为一共通电极,重叠电极315c、315d以及半导体层314b,并电性连接电极312e。在另一实施例中,电极317c电性连接屏蔽层317b。

[0065]

绝缘层318重叠电极317a~317c。在本实施例中,绝缘层318直接接触例如部分的绝缘层316。像素电极(pixel electrode)319a及319b设置于绝缘层318之上。在本实施例中,像素电极319a电性连接电极315b。由于屏蔽层317b设置于特定线段312c与像素电极319a之间,故可减少特定线段312c的电场对像素电极319b的影响。另外,像素电极319b电性连接电极315d。

[0066]

显示介质层320设置于像素电极319a及319b之上。在本实施例中,显示介质层中的显示介质可为液晶,但本申请并不限于此。在一些实施例中,显示介质可为自发光元件,例如有机发光二极管(organic light emitting diode,oled)、次毫米发光二极管(mini led)、微发光二极管(micro led)或量子点发光二极管(quantum dot light emitting diode,qled或qdled)。在一实施例中,显示介质层320直接接触例如部分的绝缘层318。在本实施例中,由于一镂空区域(如图1的rg1)贯穿电子装置300,故框胶(sealant)321涂布于镂空区域rg1的周围,用以密封显示介质层320,减少显示介质层320的液晶从镂空区域(如图1的rg1)渗出的可能。在本实施例中,框胶321与部分的绝缘层316和318重叠,但本申请并不限于此。在一些实施例中,框胶321位于镂空区域rg1与绝缘层316和318之间,以分隔镂空区域rg1与绝缘层316和318,而在一些实施例中,框胶321可与上基板324或下基板311直接接

触。

[0067]

彩色滤光层(color filter)322a及322b设置于显示介质层320之上,用以滤除部分颜色的光线。

[0068]

黑色矩阵(black matrix,bm)323a及323b设置于显示介质层320之上。在本实施例中,在上基板324的法线方向上,黑色矩阵323a重叠彩色滤光层322a的一部分,而黑色矩阵323b重叠彩色滤光层322a的另一部分。在此例中,部分的彩色滤光层322a并未与黑色矩阵323a或323b重叠。另外,黑色矩阵323b重叠彩色滤光层322b的一部分。在此例中,彩色滤光层322b的另一部分未被黑色矩阵323b所重叠,但本申请并不以此为限。在一些实施例中,彩色滤光层322a或322b与黑色矩阵323a或323b并未重叠。

[0069]

上基板324重叠黑色矩阵323a、323b及彩色滤光层322a、322b。在一些实施例中,上下基板可分别为硬板(如玻璃基板)、软性可挠基板或上述的组合,但不限于此。在本实施例中,镂空区域rg1贯穿下基板311、绝缘层313、316、318、显示介质层320、黑色矩阵323b及上基板324。在一实施例中,绝缘层313、316及318的材料包括sinx(氮化硅)或siox(氧化硅),但不限于此。

[0070]

图4a为本申请的电子装置的另一实施例的结构示意图。如图所示,电子装置400a具有一下基板411。在一实施例中,下基板411为一玻璃基板。电极412a、412b、412d~412f及特定线段412c设置于下基板411之上,绝缘层413重叠电极412a~412f。其中,本实施例的绝缘层413、电极412a、412b、412d到412f及特定线段412c与图3所示的实施例中的绝缘层313、电极312a、312b、312d到312f及特定线段312c在位置、材料、制程与功能上相似,故在此不再赘述。

[0071]

相似的,在图4a的实施例中,半导体层414a及414b、电极415a及415b、电极415c及415d、绝缘层417与图3所示的实施例中的半导体层314a及314b、电极315a及315b、电极315c及315d、绝缘层316在位置、材料、制程与功能上相似,故在此不再赘述。

[0072]

像素电极416a重叠部分的电极415b及绝缘层413。在本实施例中,将像素电极416a与特定线段412c之间的间距在基板上的投影定义为一距离dis。借由将像素电极416a与特定线段412c之间的距离dis加大,便可降低像素电极416a受到特定线段412c的电场的干扰的情况发生。在一实施例中,像素电极416b重叠部分的电极415d及绝缘层413。

[0073]

电极418a、418b、418d、418e及屏蔽层418c设置于绝缘层417之上。在本实施例中,电极418a及418b作为共通电极。电极418a电性连接电极412a。电极418b重叠像素电极416a,并具有多个金属块。屏蔽层418c重叠特定线段412c。在本实施例中,屏蔽层418c用以减少特定线段412c的电场对像素电极416a的影响。在本实施例中,屏蔽层418c电性连接电极412d,用以接收一固定电压。在其它实施例中,电极412d接收一接地电压或是一共通电压。电极418d及418e作为共通电极。在本实施例中,电极418d电性连接电极412e。电极418e重叠像素电极416b,并具有多个金属块。在本实施例中,除了增加像素电极416a与特定线段412c之间的距离dis外,通过将绝缘层417减薄的方式减少屏蔽层418c与特定线段412c的距离,也可以减少像素电极416a所受到特定线段412c电场干扰的现象。

[0074]

显示介质层419设置于电极418a~418e之上。在一实施例中,显示介质层419直接接触例如部分的绝缘层417,在本实施例中,显示介质层中的显示介质的材料类型与前述实施例相似,故不再赘述。框胶420涂布于镂空区域rg1的周围,用以密封显示介质层419,减少

显示介质层419里的液晶从一镂空区域(如rg1)渗出的可能。在本实施例中,框胶420与部分的绝缘层417重叠,但本申请并不限于此。在一些实施例中,框胶420位于镂空区域rg1与绝缘层417之间,并分隔镂空区域rg1与绝缘层417,而在一些实施例中,框胶420可与上基板423或下基板411直接接触。

[0075]

彩色滤光层421a及421b设置于显示介质层419之上,用以滤除部分颜色的光线,黑色矩阵422a及422b设置于显示介质层419之上。在本实施例中,黑色矩阵422a重叠部分彩色滤光层421a,而黑色矩阵422b重叠彩色滤光层421a的另一部分。在此例中,部分的彩色滤光层421a并未重叠黑色矩阵422a或422b。另外,黑色矩阵422b重叠彩色滤光层421b的一部分,但本申请并不以此为限。在一些实施例中,彩色滤光层421a或421b与黑色矩阵422a或422b并未重叠。上基板423重叠黑色矩阵422a、422b及彩色滤光层421a、421b。在一实施例中,上基板423为一玻璃基板,但本申请并不以此为限。在本实施例中,镂空区域rg1贯穿下基板411、绝缘层413、417、框胶420、黑色矩阵422b及上基板423。在一实施例中,绝缘层413、417的材料包括sinx或siox,但不限于此。

[0076]

图4b为本申请的电子装置的另一实施例的结构示意图。图4b中的各元件与图4a相似,故不再赘述。不同之处在于,在图4b的电子装置400b中,特定线段412c设置于绝缘层413之上。在本实施例中,特定线段412c与像素电极416a是由同一道制程所形成。在一实施例中,特定线段412c与像素电极416a具有相同的导电材料。

[0077]

图5为本申请的电子装置的另一实施例的结构示意图。如图所示,电子装置500具有一下基板511与上基板530。在一些实施例中,下基板511与上基板530为硬板(例如玻璃基板)、可挠软性基板或其组合,但本申请并不以此为限。遮光层512a~512d设置于下基板511之上。

[0078]

绝缘层513设置在遮光层512a~512d之上。在本实施例中,绝缘层513直接接触例如部分的下基板511。在一实施例中,绝缘层513的材料包括sinx,但不限于此。绝缘层514重叠绝缘层513。在一实施例中,绝缘层514的材料包括siox,但不限于此。绝缘层515重叠于绝缘层514之上。在一实施例中,绝缘层515的材料包括sinx,但不限于此。

[0079]

电极516a~516f设置于绝缘层515之上。在本实施例中,通道层516b位于电极516a与516c之间,并且通道层516e位于电极516d与516f之间。绝缘层517重叠电极516a~516f。在本实施例中,绝缘层517直接接触例如部分的绝缘层515。在一实施例中,绝缘层517的材料包括siox,但不限于此。

[0080]

栅极介电层518a~518d设置于绝缘层517之上。电极519a~519d分别设置于绝缘层518a~518d之上。在本实施例中,电极519a~519d作为栅极。电极519a、519b、516a、516c以及通道层516b构成一晶体管t5,其中电极519a及519b作为晶体管t5的栅极,电极516a作为晶体管t5的漏极,电极516c作为晶体管t5的源极。在其它实施例中,电极516a作为晶体管t5的源极,电极516c作为晶体管t5的漏极。另外,电极519c、519d、516d、516f及通道层516e构成一晶体管t6,其中电极519d及519d作为晶体管t6的栅极,电极516d作为晶体管t6的漏极,电极516f作为晶体管t6的源极。在其它实施例中,电极516d作为晶体管t6的源极,电极516f作为晶体管t6的漏极。但本申请的晶体管结构并不限于此。例如在一些实施例中的晶体管中仅存在一栅极,在一些实施例中,晶体管的栅极可位于通道层的下方,而在一些实施例中,两个栅极可在基板的法线方向上重叠。

[0081]

绝缘层520重叠电极519a~519d。在本实施例中,绝缘层520直接接触例如部分的绝缘层517。在一实施例中,绝缘层520的材料包括siox,但不限于此。绝缘层521重叠绝缘层520。在一实施例中,绝缘层521的材料包括sinx,但不限于此。

[0082]

电极522a~522c、522e~522g及特定线段522d位于绝缘层521之上。在本实施例中,电极522a电性连接电极516a,电极522b电性连接电极516c。电极522c作用为一共通电极,用以接收一共通电压或是一接地电压。特定线段522d为电子装置500的显示区内的信号线的特定线段(如图1的sg1~sg6)。电极522e用以接收一固定电压。在一实施例中,电极522e接收一接地电压或是一共通电压。电极522f电性连接电极516d,而电极522g电性连接电极516f。

[0083]

平坦层523重叠电极522a~522c、522e~522g及特定线段522d。在本实施例中,平坦层523直接接触例如部分的绝缘层521。电极524a、524b、524d、524e及屏蔽层524c设置于平坦层523之上。在一实施例中,电极524a及524b作为一共通电极。电极524b电性连接电极522c。屏蔽层524c重叠特定线段522d,用以减少特定线段522d的电场对其它电极(如像素电极)或走线的影响。在本实施例中,屏蔽层524c电性连接电极522e。电极524d与524e作为共通电极。

[0084]

绝缘层525重叠电极524a、524b、524d、524e及屏蔽层524c。在本实施例中,绝缘层525直接接触例如部分的平坦层523。在一实施例中,绝缘层525的材料包括sinx,但不限于此。像素电极526a与526b设置于绝缘层525之上。在本实施例中,当像素电极526a与特定线段522d之间的最近距离愈长时,像素电极526a的电位愈不受特定线段522d的电位的影响。

[0085]

显示介质层527设置于像素电极526a与526b之上。在一实施例中,显示介质层527直接接触例如部分的绝缘层525。框胶581涂布于镂空区域rg的周围,用以密封显示介质层527,减少显示介质层527里的液晶从镂空区域rg1渗出的可能性,在本实施例中,框胶581与各绝缘层重叠,而在一些实施例中,框胶581位于镂空区域rg1与部分绝缘层之间,并分隔镂空区域rg1与这些绝缘层,而在一些实施例中,框胶581可与上基板530或下基板511直接接触。在本实施例中,显示介质层中的显示介质的材料类型与前述实施例相似,故不再赘述。

[0086]

彩色滤光层528a及528b设置于显示介质层527之上,用以滤除部分颜色的光线。黑色矩阵529a及529b设置于显示介质层527之上。在本实施例中,黑色矩阵529a重叠彩色滤光层528a的一部分,而黑色矩阵529b重叠彩色滤光层528a的另一部分。在此例中,部分的彩色滤光层528a并未重叠黑色矩阵529a或529b。另外,黑色矩阵529b重叠彩色滤光层528b的一部分。在一些实施例中,彩色滤光层528a或528b与黑色矩阵529a或529b并未重叠。

[0087]

上基板530重叠黑色矩阵529a、529b及彩色滤光层528a、528b。在本实施例中,镂空区域rg贯穿下基板511、绝缘层513~515、517、520、521、平坦层523、绝缘层525、框胶581、黑色矩阵529b及上基板530。由于屏蔽层524c重叠特定线段522d,故可减少特定线段522d的电场对其它电极或走线的干扰。

[0088]

图6为本申请的栅极电路的一实施例的示意图。如图所示,栅极电路610包括一控制电路611以及驱动元件612~615。在一实施例中,控制电路611至少包括一移位暂存电路,用以依序输出栅极信号,但并不限于此。本申请并不限定控制电路611的架构。

[0089]

驱动元件612~615根据控制电路611的输出及时脉信号clk,提供栅极信号g1~g4,用以开启显示区621里各扫描线sl1~sl4所连接的像素。在本实施例中,驱动元件612~

615均为n型晶体管,在另一些实施例中,驱动元件612~615可为p型晶体管,在另一些实施例中,驱动元件612~615可为n型与p型晶体管的组合,但本申请并未以此为限。以驱动元件612为例,当控制电路611导通驱动元件612时,驱动元件612根据时脉信号clk提供栅极信号g1。在一实施例中,驱动元件612~615可作为缓冲器(buffer),但本申请并不限定于此。

[0090]

为了使各驱动元件所对应的栅极信号抵达所对应扫描线中的像素时能具有相近的驱动能力,在一实施例中,驱动元件612~615具有不同的尺寸,用以提供不同强度的栅极信号。举例而言,当驱动元件612被开启时,流过驱动元件612的栅极信号g1不同于驱动元件615被开启时,流过驱动元件615的栅极信号g4。需注意的是,在本实施例中,作为驱动元件的晶体管具有一通道区(channel region),通道区具有一宽度w与一间距l,而驱动元件的尺寸为通道区宽度w与间距l间的比值(w/l)。

[0091]

在本实施例中,由于显示区621里的扫描线sl1~sl4的长度不均,因此,不同长度的扫描线本身可能具有不同的电阻。同时,不同的扫描线可能因为耦接不同数量的像素及跨越不同数量的数据线而造成不同的电容负载,因此在每条扫描线的电阻及电容负载均可能不同的情况下,使得不同传输线之间的栅极信号的穿通(feedthrough)电压产生差异,进而影响画面品质。然而,借由提供不同强度的栅极信号g1~g4,便可补偿传输线之间的穿通电压的差异。

[0092]

以栅极信号g1与g4为例,由于扫描线sl4的长度大于扫描线sl1的长度,故扫描线sl4的整体负载(例如包含了电阻及电容负载)大于扫描线sl1的整体负载。在此例中,由于驱动元件615的尺寸大于驱动元件612的尺寸,故驱动元件615所提供的栅极信号g4的强度大于驱动元件612所提供的栅极信号g1的强度。因此,便可减少扫描线sl1与sl4之间的穿通电压的差异。

[0093]

在其它实施例中,借由改变扫描线sl1~sl4的负载,也可减少扫描线sl1~sl4的穿通电压的差异。以扫描线sl1及sl4为例,当扫描线sl4所对应的像素(未显示)的元件尺寸小于扫描线sl1所对应的像素的元件尺寸时,扫描线sl1与sl4之间的穿通电压的差异也会随之变小。

[0094]

除非另作定义,在此所有词汇(包含技术与科学词汇)均属本领域技术人员的一般理解。此外,除非明白表示,词汇于一般字典中的定义应解释为与其相关技术领域的文章中意义一致,而不应解释为理想状态或过分正式的语态。

[0095]

虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的修改和完善,因此本发明的保护范围当以权利要求书所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1