一种内部补偿电路及其控制方法与流程

[0001]

本发明涉及显示器补偿电路技术领域,特别涉及一种内部补偿电路及其控制方法。

背景技术:

[0002]

当今科技发展,人们生活水平进步,对显示器的面板要求变得更高,需要面板厂商进一步提升显示器的显示质量,要提高显示器的质量,提高解析度是关键,为了在有限的空间内尽可能做高解析度,需要每个pixel(像素)所占面积更小;对于oled(英文全称为organic light emitting diode,有机发光二极管)面板来说,面内2t1c(两个tft和一个电容)pixel电路会受到vth(阈值电压)漂移的影响导致面板发光亮度不均匀,影像显示效果,补偿电路可提升面板显示效果,而为了达到更好的补偿效果,补偿电路会有多个tft(英文全称为thin film transistor,薄膜场效应晶体管),但是tft过多会使pixel所占面积增大,进而导致面板容纳的pixel数量减少,即解析度变低,无法满足高解析度的要求。

技术实现要素:

[0003]

本发明所要解决的技术问题是:提供一种内部补偿电路及其控制方法。

[0004]

为了解决上述技术问题,本发明采用的第一种技术方案为:

[0005]

一种内部补偿电路,包括晶体管t1、晶体管t2、晶体管t3、晶体管t4、晶体管t5、晶体管t6、电容c1、电容c2和发光二极管oled,所述晶体管t3、晶体管t4和晶体管t6均为多晶硅薄膜晶体管且均设置于基板与介质层之间,所述晶体管t1、晶体管t2和晶体管t5均为氧化物薄膜晶体管且均设置于介质层上方;

[0006]

所述晶体管t1的栅极接第一扫描信号,所述晶体管t1的源极接数据信号,所述晶体管t1的漏极分别与电容c1的一端和晶体管t2的源极电连接,所述晶体管t2的栅极接第二扫描信号,所述晶体管t2的漏极分别与晶体管t3的源极和电容c2的一端电连接,所述晶体管t3的栅极接第三扫描信号,所述晶体管t3的漏极分别与晶体管t4的栅极和晶体管t5的源极电连接,所述晶体管t4的漏极接电源信号,所述晶体管t4的源极分别与晶体管t6的源极和电容c2的另一端电连接,所述晶体管t5的栅极接第二扫描信号,所述晶体管t6的漏极与发光二极管oled的阳极电连接,所述晶体管t6的栅极接第二扫描信号。

[0007]

本发明采用的第二种技术方案为:

[0008]

一种内部补偿电路的控制方法,包括以下步骤:

[0009]

步骤s1、在第一时间段,控制晶体管t1的栅极输入低电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平;

[0010]

步骤s2、在第二时间段,控制晶体管t1的栅极和晶体管t3的栅极均输入高电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平;

[0011]

步骤s3、在第三时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入低电平;

[0012]

步骤s4、在第四时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平,控制晶体管t3的栅极输入高电平;所述第一时间段、第二时间段、第三时间段和第四时间段为依次连续的时间段。

[0013]

本发明的有益效果在于:

[0014]

本方案设计的晶体管t3、晶体管t4和晶体管t6均为多晶硅薄膜晶体管且均设置于基板与介质层之间,晶体管t1、晶体管t2和晶体管t5均为氧化物薄膜晶体管且均设置于介质层上方,这样设计的内部补偿电路可补偿vth漂移,改善了由vth漂移引发的不良问题;这样设计的补偿电路架构可减少pixel所占面积,增加解析度,提高ppi,改善显示效果。

附图说明

[0015]

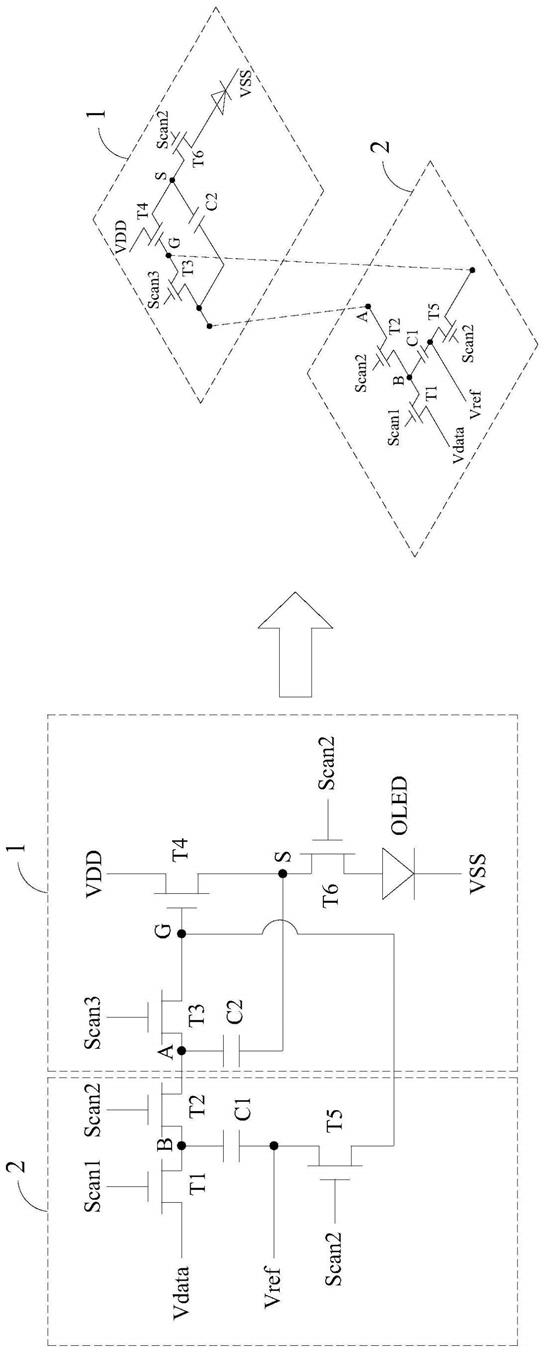

图1为根据本发明的一种内部补偿电路的结构示意图;

[0016]

图2为根据本发明的一种内部补偿电路的架构分层示意图;

[0017]

图3为根据本发明的一种内部补偿电路的架构分层示意图;

[0018]

图4为根据本发明的一种内部补偿电路的波形图;

[0019]

图5为根据本发明的一种内部补偿电路的t1阶段的结构示意图;

[0020]

图6为根据本发明的一种内部补偿电路的t2阶段的结构示意图;

[0021]

图7为根据本发明的一种内部补偿电路的t3阶段的结构示意图;

[0022]

图8为根据本发明的一种内部补偿电路的t4阶段的结构示意图;

[0023]

图9为根据本发明的一种内部补偿电路的控制方法的步骤流程图;

[0024]

标号说明:

[0025]

1、上层;2、下层。

具体实施方式

[0026]

为详细说明本发明的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

[0027]

请参照图1,本发明提供的一种技术方案:

[0028]

一种内部补偿电路,包括晶体管t1、晶体管t2、晶体管t3、晶体管t4、晶体管t5、晶体管t6、电容c1、电容c2和发光二极管oled,所述晶体管t3、晶体管t4和晶体管t6均为多晶硅薄膜晶体管且均设置于基板与介质层之间,所述晶体管t1、晶体管t2和晶体管t5均为氧化物薄膜晶体管且均设置于介质层上方;

[0029]

所述晶体管t1的栅极接第一扫描信号,所述晶体管t1的源极接数据信号,所述晶体管t1的漏极分别与电容c1的一端和晶体管t2的源极电连接,所述晶体管t2的栅极接第二扫描信号,所述晶体管t2的漏极分别与晶体管t3的源极和电容c2的一端电连接,所述晶体管t3的栅极接第三扫描信号,所述晶体管t3的漏极分别与晶体管t4的栅极和晶体管t5的源极电连接,所述晶体管t4的漏极接电源信号,所述晶体管t4的源极分别与晶体管t6的源极和电容c2的另一端电连接,所述晶体管t5的栅极接第二扫描信号,所述晶体管t6的漏极与发光二极管oled的阳极电连接,所述晶体管t6的栅极接第二扫描信号。

[0030]

从上述描述可知,本发明的有益效果在于:

[0031]

本方案设计的晶体管t3、晶体管t4和晶体管t6均为多晶硅薄膜晶体管且均设置于

基板与介质层之间,晶体管t1、晶体管t2和晶体管t5均为氧化物薄膜晶体管且均设置于介质层上方,这样设计的内部补偿电路可补偿vth漂移,改善了由vth漂移引发的不良问题;这样设计的补偿电路架构可减少pixel所占面积,增加解析度,提高ppi,改善显示效果。

[0032]

进一步的,所述电容c1设置于介质层上方。

[0033]

进一步的,所述电容c2设置于基板与介质层之间。

[0034]

进一步的,还包括穿透介质层的第一连接线和第二连接线,所述晶体管t2的漏极与晶体管t3的漏极之间通过第一连接线连接,所述晶体管t5的源极与晶体管t3的漏极之间均第二连接线连接。

[0035]

请参照图9,本发明提供的另一种技术方案:

[0036]

一种内部补偿电路的控制方法,包括以下步骤:

[0037]

步骤s1、在第一时间段,控制晶体管t1的栅极输入低电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平;

[0038]

步骤s2、在第二时间段,控制晶体管t1的栅极和晶体管t3的栅极均输入高电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平;

[0039]

步骤s3、在第三时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入低电平;

[0040]

步骤s4、在第四时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平,控制晶体管t3的栅极输入高电平;所述第一时间段、第二时间段、第三时间段和第四时间段为依次连续的时间段。

[0041]

从上述描述可知,本发明的有益效果在于:

[0042]

在第一时间段,控制晶体管t1的栅极输入低电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平,在第二时间段,控制晶体管t1的栅极和晶体管t3的栅极均输入高电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平,在第三时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入低电平,在第四时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平,控制晶体管t3的栅极输入高电平,使得能够补偿vth漂移,改善了由vth漂移引发的不良问题;这样设计的补偿电路架构可减少pixel所占面积,增加解析度,提高ppi,改善显示效果。

[0043]

请参照图1至图8,本发明的实施例一为:

[0044]

请参照图1,一种内部补偿电路,包括晶体管t1、晶体管t2、晶体管t3、晶体管t4、晶体管t5、晶体管t6、电容c1、电容c2和发光二极管oled;

[0045]

请参照图2和图3,所述晶体管t3、晶体管t4和晶体管t6均为多晶硅薄膜晶体管且均设置于基板与介质层之间(即下层2),所述晶体管t1、晶体管t2和晶体管t5均为氧化物薄膜晶体管且均设置于介质层上方(即上层1);

[0046]

请参照图1,所述晶体管t1的栅极接第一扫描信号,所述晶体管t1的源极接数据信号,所述晶体管t1的漏极分别与电容c1的一端和晶体管t2的源极电连接,所述晶体管t2的栅极接第二扫描信号,所述晶体管t2的漏极分别与晶体管t3的源极和电容c2的一端电连接,所述晶体管t3的栅极接第三扫描信号,所述晶体管t3的漏极分别与晶体管t4的栅极和晶体管t5的源极电连接,所述晶体管t4的漏极接电源信号,所述晶体管t4的源极分别与晶

体管t6的源极和电容c2的另一端电连接,所述晶体管t5的栅极接第二扫描信号,所述晶体管t6的漏极与发光二极管oled的阳极电连接,所述晶体管t6的栅极接第二扫描信号。

[0047]

请参照图1,所述电容c1设置于介质层上方。

[0048]

请参照图1,所述电容c2设置于基板与介质层之间。

[0049]

请参照图1,还包括穿透介质层的第一连接线和第二连接线,所述晶体管t2的漏极与晶体管t3的漏极之间通过第一连接线连接,所述晶体管t5的源极与晶体管t3的漏极之间均第二连接线连接。

[0050]

上述的内部补偿电路的工作原理为:

[0051]

请参照图4和图5,为t1阶段,第一扫描信号scan1写入低电平,晶体管t1打开,b点写入vdata(数据信号)电压,第二扫描信号scan2写入高电平,晶体管t2和晶体管t5关闭,v

b

=v

data

;

[0052]

请参照图4和图6,为t2阶段,第一扫描信号scan1写入高电平,晶体管t1关闭,第二扫描信号scan2依旧写入高电平,晶体管t2和晶体管t5继续保持关闭,晶体管t6依旧打开,第三扫描信号scan3写入低电平,晶体管t3关闭,s点放电至发光二极管oled两端跨压,即v

s

=v

oled

;

[0053]

请参照图4和图7,为t3阶段,第二扫描信号scan2写入低电平,晶体管t2和晶体管t5打开,a点写入vdata(数据信号)电压,g点写入vref(参考电压),s点达到(v

ref-vth),即此时v

a

=v

data

,v

g

=v

ref

,v

s

=v

ref

ꢀ–

vth;

[0054]

请参照图4和图8,为t4阶段,第二扫描信号scan2写入高电平,晶体管t2和晶体管t5关闭,晶体管t6打开,第三扫描信号scan3写入高电平,晶体管t3打开;g点写入vdata(数据信号)电压,即v

g

=v

dat

a,v

s

=v

ref

ꢀ–

vth,那么v

gs

=v

g-v

s

=v

data-(v

ref

ꢀ–

vth),代入n型tft饱和区电流公式i

oled

=1/2μnc

ox

w/l(v

gs-v

th

)2,得到i

oled

=1/2μnc

ox

w/l(v

data-v

ref

)2(注μn为场效应迁移率,c

ox

为单位面积的绝缘层电容;w/l为tft沟道宽度比长度)。

[0055]

从公式中可以得出此电路中发光二极管oled的发光电流只与vdata与vref讯号有关,与vth无关,其他参数相对固定,不会受到其他不稳定因子(例如vdd、vss、voled等)的影响,同时该分层架构使pixel所占面积较小,面板容纳pixel数量较多,解析度较高。

[0056]

请参照图4至图9,本发明的实施例二为:

[0057]

请参照图9,一种内部补偿电路的控制方法,包括以下步骤:

[0058]

步骤s1、在第一时间段,控制晶体管t1的栅极输入低电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平;

[0059]

步骤s2、在第二时间段,控制晶体管t1的栅极和晶体管t3的栅极均输入高电平,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平;

[0060]

步骤s3、在第三时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入低电平;

[0061]

步骤s4、在第四时间段,控制晶体管t2的栅极、晶体管t5的栅极和晶体管t6的栅极均输入高电平,控制晶体管t3的栅极输入高电平;所述第一时间段、第二时间段、第三时间段和第四时间段为依次连续的时间段。

[0062]

本方案的具体实施例为:

[0063]

请参照图4和图5,在第一时间段(即t1阶段),第一扫描信号scan1写入低电平,晶

体管t1打开,b点写入vdata(数据信号)电压,第一扫描信号scan2写入高电平,晶体管t2和晶体管t5关闭,v

b

=v

data

;

[0064]

请参照图4和图6,在第二时间段(即t2阶段),第一扫描信号scan1写入高电平,晶体管t1关闭,第二扫描信号scan2依旧写入高电平,晶体管t2和晶体管t5继续保持关闭,晶体管t6依旧打开,第三扫描信号scan3写入低电平,晶体管t3关闭,s点放电至发光二极管oled两端跨压,即v

s

=v

oled

;

[0065]

请参照图4和图7,在第三时间段(即t3阶段),第二扫描信号scan2写入低电平,晶体管t2和晶体管t5打开,a点写入vdata(数据信号)电压,g点写入vref(参考电压),s点达到(v

ref-vth),即此时v

a

=v

data

,v

g

=v

ref

,v

s

=v

ref

–

vth;

[0066]

请参照图4和图8,在第四时间段(即t4阶段),第二扫描信号scan2写入高电平,晶体管t2和晶体管t5关闭,晶体管t6打开,第三扫描信号scan3写入高电平,晶体管t3打开;g点写入vdata(数据信号)电压,即v

g

=v

data

,v

s

=v

ref

–

vth,那么v

gs

=v

g-v

s

=v

data-(v

ref

ꢀ–

vth),代入n型tft饱和区电流公式i

oled

=1/2μnc

ox

w/l(v

gs-vth)2,得到i

oled

=1/2μnc

ox

w/l(v

data-v

ref

)2(注μn为场效应迁移率,c

ox

为单位面积的绝缘层电容;w/l为tft沟道宽度比长度)。

[0067]

从公式中可以得出此电路中发光二极管oled的发光电流只与vdata与vref讯号有关,与vth无关,其他参数相对固定,不会受到其他不稳定因子(例如vdd、vss、voled等)的影响,同时该分层架构使pixel所占面积较小,面板容纳pixel数量较多,解析度较高。

[0068]

综上所述,本发明提供的一种内部补偿电路及其控制方法,本方案设计的晶体管t3、晶体管t4和晶体管t6均为多晶硅薄膜晶体管且均设置于基板与介质层之间,晶体管t1、晶体管t2和晶体管t5均为氧化物薄膜晶体管且均设置于介质层上方,这样设计的内部补偿电路可补偿vth漂移,改善了由vth漂移引发的不良问题;这样设计的补偿电路架构可减少pixel所占面积,增加解析度,提高ppi,改善显示效果。

[0069]

以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1