显示装置的制作方法

1.本发明涉及一种显示装置,更具体地,涉及一种包括数据-扫描集成芯片的显示装置。

背景技术:

2.显示装置包括:显示面板,包括多个像素;扫描驱动器,通过多个扫描线中选择的扫描线,将扫描信号提供于所述多个像素中选择的行的像素;以及数据驱动器,通过多个数据线,将数据电压提供于所述选择的行的像素。所述选择的行的像素可以在接收通过所述扫描驱动器提供的所述扫描信号的期间,存储通过所述数据驱动器提供的所述数据电压,并基于所述存储的数据电压而发光。

3.通常,所述扫描驱动器配置于所述显示面板的至少一个第一侧,所述数据驱动器配置于与所述第一侧不同的所述显示面板的至少一个第二侧。由此,减小所述显示面板的边框宽度存在局限。

技术实现要素:

4.本发明的一目的是提供数据驱动器以及扫描驱动器配置于显示面板的相同侧并实现为数据-扫描集成芯片的显示装置。

5.但是,本发明要解决的技术问题不限于上述提及的技术问题,可以在不超出本发明的构思以及领域的范围中进行各种扩展。

6.为了达到本发明的一目的,根据本发明的实施例的显示装置包括:显示面板,包括:多个像素;多个数据线,向第一方向延伸,并连接于所述多个像素;多个第一扫描线,向与所述第一方向不同的第二方向延伸,并连接于所述多个像素;以及多个第二扫描线,向所述第一方向延伸,并连接于所述多个第一扫描线;数据驱动器,通过所述多个数据线,将数据电压提供于所述多个像素;以及扫描驱动器,通过所述多个第二扫描线以及所述多个第一扫描线,将扫描信号以行单位依次提供于所述多个像素。所述数据驱动器以及所述扫描驱动器实现为输出所述数据电压以及所述扫描信号的数据-扫描集成芯片。

7.在一实施例中,可以是,在所述多个第二扫描线中的相邻的两个之间配置有所述多个数据线中的至少一个。

8.在一实施例中,可以是,所述数据-扫描集成芯片包括:多个数据输出焊盘,连接于所述多个数据线;以及多个扫描输出焊盘,连接于所述多个第二扫描线。

9.在一实施例中,可以是,在所述多个扫描输出焊盘中的相邻的两个之间配置有所述多个数据输出焊盘中的至少一个。

10.在一实施例中,可以是,在第一区间中,所述数据-扫描集成芯片将与所述多个像素中选择的行的像素有关的所述数据电压输出于所述多个数据线,在所述第一区间后的第二区间中,所述数据-扫描集成芯片使所述多个数据线浮置,并将所述扫描信号输出于所述多个第二扫描线中与所述选择的行相对应的第二扫描线。

11.在一实施例中,可以是,在所述第一区间期间,所述数据电压充电于所述多个数据线,在所述第二区间期间,充电于所述多个数据线中的所述数据电压存储于所述选择的行的所述像素。

12.在一实施例中,可以是,所述数据-扫描集成芯片包括:第一移位寄存器,基于数据时钟信号,生成采样信号;锁存器阵列,响应所述采样信号,存储图像数据;第一电平移位器阵列,将从所述锁存器阵列输出的锁存器输出信号的电压电平进行移位;数字-模拟变换器阵列,对从所述第一电平移位器阵列输出的移位器输出信号执行数字-模拟变换;第一输出缓冲器阵列,将从所述数字-模拟变换器阵列输出的变换器输出信号作为所述数据电压输出;多个数据输出焊盘,连接于所述多个数据线;数据输出开关阵列,响应选择信号,将所述第一输出缓冲器阵列选择性地连接于所述多个数据输出焊盘;第二移位寄存器,基于扫描时钟信号,生成所述扫描信号;第二电平移位器阵列,将从所述第二移位寄存器输出的所述扫描信号的电压电平进行移位;第二输出缓冲器阵列,输出从所述第二电平移位器阵列输出的所述扫描信号;以及多个扫描输出焊盘,连接于所述第二输出缓冲器阵列以及所述多个第二扫描线。

13.在一实施例中,可以是,所述数据-扫描集成芯片包括被所述数据驱动器以及所述扫描驱动器共享的至少一个构成要件。

14.在一实施例中,可以是,所述数据-扫描集成芯片包括用于所述数据驱动器的第一移位寄存器、锁存器阵列、数字-模拟变换器阵列以及第一输出缓冲器阵列,并包括用于所述扫描驱动器的第二移位寄存器以及第二输出缓冲器阵列,并且还包括被所述数据驱动器以及所述扫描驱动器共享的共享电平移位器阵列。

15.在一实施例中,可以是,所述共享电平移位器阵列包括:多个电平移位器;移位器输入开关阵列,响应选择信号而将所述锁存器阵列的输出端子连接于所述多个电平移位器的输入端子,并响应反向选择信号而将所述第二移位寄存器的输出端子连接于所述多个电平移位器的所述输入端子;以及移位器输出开关阵列,响应所述选择信号而将所述多个电平移位器的输出端子连接于所述数字-模拟变换器阵列的输入端子,并响应所述反向选择信号而将所述多个电平移位器的所述输出端子连接于所述第二输出缓冲器阵列的输入端子。

16.在一实施例中,可以是,所述共享电平移位器阵列还包括:第一移位器高电源开关,响应所述选择信号而将数据移位器高电源电压传输于所述共享电平移位器阵列的高电源线;第二移位器高电源开关,响应所述反向选择信号而将扫描移位器高电源电压传输于所述共享电平移位器阵列的所述高电源线;第一移位器低电源开关,响应所述选择信号而将数据移位器低电源电压传输于所述共享电平移位器阵列的低电源线;以及第二移位器低电源开关,响应所述反向选择信号而将扫描移位器低电源电压传输于所述共享电平移位器阵列的所述低电源线。

17.在一实施例中,可以是,所述数据-扫描集成芯片包括用于所述数据驱动器的第一移位寄存器、锁存器阵列、第一电平移位器阵列以及数字-模拟变换器阵列,并包括用于所述扫描驱动器的第二移位寄存器以及第二电平移位器阵列,并且还包括被所述数据驱动器以及所述扫描驱动器共享的共享输出缓冲器阵列。

18.在一实施例中,可以是,所述数据-扫描集成芯片还包括:多个数据输出焊盘,连接

于所述多个数据线;以及多个扫描输出焊盘,连接于所述多个第二扫描线,所述共享输出缓冲器阵列包括:多个输出缓冲器;缓冲器输入开关阵列,响应选择信号而将所述数字-模拟变换器阵列的输出端子连接于所述多个输出缓冲器的输入端子,并响应反向选择信号而将所述第二电平移位器阵列的输出端子连接于所述多个输出缓冲器的所述输入端子;以及缓冲器输出开关阵列,响应所述选择信号而将所述多个输出缓冲器的输出端子连接于所述多个数据输出焊盘,并响应所述反向选择信号而将所述多个输出缓冲器的所述输出端子连接于所述多个扫描输出焊盘。

19.在一实施例中,可以是,所述多个输出缓冲器的高电源电压的电压电平被确定为数据缓冲器高电源电压与扫描缓冲器高电源电压中高的电压的电压电平,所述多个输出缓冲器的低电源电压的电压电平被确定为数据缓冲器低电源电压与扫描缓冲器低电源电压中低的电压的电压电平。

20.在一实施例中,可以是,所述数据-扫描集成芯片包括用于所述数据驱动器的第一移位寄存器、锁存器阵列以及数字-模拟变换器阵列,并包括用于所述扫描驱动器的第二移位寄存器,并且还包括被所述数据驱动器以及所述扫描驱动器共享的共享电平移位器阵列以及共享输出缓冲器阵列。

21.在一实施例中,可以是,所述数据-扫描集成芯片还包括:多个数据输出焊盘,连接于所述多个数据线;以及多个扫描输出焊盘,连接于所述多个第二扫描线,所述共享电平移位器阵列包括:多个电平移位器;移位器输入开关阵列,响应选择信号而将所述锁存器阵列的输出端子连接于所述多个电平移位器的输入端子,并响应反向选择信号而将所述第二移位寄存器的输出端子连接于所述多个电平移位器的所述输入端子;以及移位器输出开关阵列,响应所述选择信号而将所述多个电平移位器的输出端子连接于所述数字-模拟变换器阵列的输入端子,并响应所述反向选择信号而将所述多个电平移位器的所述输出端子连接于所述共享输出缓冲器阵列的输入端子,所述共享输出缓冲器阵列包括:多个输出缓冲器;缓冲器输入开关阵列,响应所述选择信号而将所述数字-模拟变换器阵列的输出端子连接于所述多个输出缓冲器的输入端子,并响应所述反向选择信号而将所述共享电平移位器阵列的输出端子连接于所述多个输出缓冲器的所述输入端子;以及缓冲器输出开关阵列,响应所述选择信号而将所述多个输出缓冲器的输出端子连接于所述多个数据输出焊盘,并响应所述反向选择信号而将所述多个输出缓冲器的所述输出端子连接于所述多个扫描输出焊盘。

22.为了达到本发明的一目的,根据本发明的实施例的显示装置包括:显示面板,包括:多个像素;多个数据线,向第一方向延伸,并连接于所述多个像素;多个第一扫描线,向与所述第一方向不同的第二方向延伸,并连接于所述多个像素;以及多个第二扫描线,向所述第一方向延伸,并连接于所述多个第一扫描线;数据驱动器,通过所述多个数据线,将数据电压提供于所述多个像素;以及扫描驱动器,通过所述多个第二扫描线以及所述多个第一扫描线,将扫描信号以行单位依次提供于所述多个像素。所述数据驱动器以及所述扫描驱动器实现为输出所述数据电压以及所述扫描信号的数据-扫描集成芯片。所述数据-扫描集成芯片包括被所述数据驱动器以及所述扫描驱动器共享的至少一个构成要件。

23.在一实施例中,可以是,所述至少一个构成要件包括被所述数据驱动器以及所述扫描驱动器共享的共享电平移位器阵列。

24.在一实施例中,可以是,所述至少一个构成要件包括被所述数据驱动器以及所述扫描驱动器共享的共享输出缓冲器阵列。

25.在一实施例中,可以是,所述至少一个构成要件包括被所述数据驱动器以及所述扫描驱动器共享的共享电平移位器阵列以及共享输出缓冲器阵列。

26.(发明的效果)

27.在根据本发明的实施例的显示装置中,数据驱动器以及扫描驱动器可以配置于显示面板的相同侧。由此,能够减小显示面板的边框宽度。

28.另外,在根据本发明的实施例的显示装置中,数据驱动器以及扫描驱动器可以实现为数据-扫描集成芯片。由此,能够减小用于显示面板的驱动的芯片或者集成电路(integrated circuit;ic)的芯片尺寸或者ic尺寸。

29.而且,在根据本发明的实施例的显示装置中,数据-扫描集成芯片可以包括由数据驱动器以及扫描驱动器共享的至少一个构成要件(例如,电平移位器阵列及/或输出缓冲器阵列)。由此,能够更加减小用于显示面板的驱动的芯片或者ic的芯片尺寸或者ic尺寸,并减小电力消耗。

30.但是,本发明的效果不限于上述的效果,可以在不超出本发明的构思以及领域的范围中进行各种扩展。

附图说明

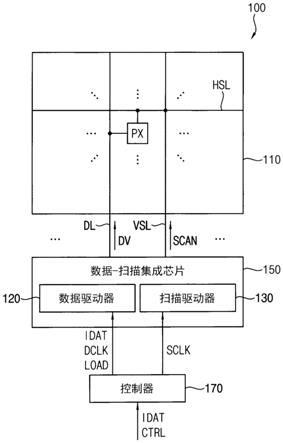

31.图1是示出根据本发明的实施例的显示装置的框图。

32.图2是示出根据本发明的实施例的包括在显示装置中的像素的一例的电路图。

33.图3是示出根据本发明的实施例的包括在显示装置中的显示面板的一例的图。

34.图4是示出根据本发明的实施例的包括在显示装置中的显示面板的另一例的图。

35.图5是用于说明至少一个数据-扫描集成芯片连接于显示面板的一例的图。

36.图6是用于说明至少一个数据-扫描集成芯片连接于显示面板的另一例的图。

37.图7是示出根据本发明的一实施例的数据-扫描集成芯片的框图。

38.图8是用于说明根据本发明的实施例的数据-扫描集成芯片的工作的一例的时序图。

39.图9是示出根据本发明的另一实施例的数据-扫描集成芯片的框图。

40.图10是示出根据本发明的实施例的包括在数据-扫描集成芯片中的电平移位器的一例的电路图。

41.图11是用于说明根据本发明的实施例的数据-扫描集成芯片的工作的一例的时序图。

42.图12是示出根据本发明的又另一实施例的数据-扫描集成芯片的框图。

43.图13是示出根据本发明的实施例的包括在数据-扫描集成芯片中的输出缓冲器的一例的框图。

44.图14是示出根据本发明的又另一实施例的数据-扫描集成芯片的框图。

45.图15是示出包括根据本发明的实施例的显示装置的电子设备的框图。

46.(附图标记说明)

47.100:显示装置

48.110、110a、110b:显示面板

49.120、210、610:数据驱动器

50.130、260、660:扫描驱动器

51.150、151、152、154、200、400、500、600:数据-扫描集成芯片

52.170:控制器

53.290:数据输出开关阵列

54.310、410、510、710:第一移位寄存器

55.320、420、520、720:锁存器阵列

56.330、530:第一电平移位器阵列

57.340、440、540、730:数字-模拟变换器阵列

58.350、450:第一输出缓冲器阵列

59.360、460、560、750:第二移位寄存器

60.370、570:第二电平移位器阵列

61.380、480:第二输出缓冲器阵列

62.490、770:共享电平移位器阵列

63.590、790:共享输出缓冲器阵列

具体实施方式

64.以下,参照所附的附图,更详细地说明本发明的优选实施例。针对附图中的相同的构成要件,使用相同的附图标记,针对相同的构成要件,省略重复的说明。

65.图1是示出根据本发明的实施例的显示装置的框图,图2是示出根据本发明的实施例的包括在显示装置中的像素的一例的电路图,图3是示出根据本发明的实施例的包括在显示装置中的显示面板的一例的图,图4是示出根据本发明的实施例的包括在显示装置中的显示面板的另一例的图,图5是用于说明至少一个数据-扫描集成芯片连接于显示面板的一例的图,图6是用于说明至少一个数据-扫描集成芯片连接于显示面板的另一例的图。

66.参照图1,根据本发明的实施例的显示装置100可以包括:显示面板110,包括多个像素px;数据驱动器120,将数据电压dv提供于多个像素px;扫描驱动器130,将扫描信号scan提供于多个像素px;以及控制器170,控制数据驱动器120以及扫描驱动器130。

67.显示面板110可以包括:多个像素px;多个数据线dl,连接于多个像素px;多个第一扫描线hsl,连接于多个像素px;以及多个第二扫描线vsl,连接于多个第一扫描线hsl。可以是,多个数据线dl向第一方向延伸,多个第一扫描线hsl向与所述第一方向不同的第二方向延伸,多个第二扫描线vsl向所述第一方向延伸。在一实施例中,可以是,所述第一方向是垂直方向,多个第二扫描线vsl是多个垂直扫描线vsl,所述第二方向是水平方向,多个第一扫描线hsl是多个水平扫描线hsl,但是不限于此。以下,针对所述第一方向是所述垂直方向且所述第二方向是所述水平方向的例子进行说明,第一扫描线hsl命名为水平扫描线hsl,第二扫描线vsl命名为垂直扫描线vsl。

68.在一实施例中,显示面板110可以是各像素px包括有机发光二极管(organic light emitting diode;oled)的oled显示面板。例如,如图2所示,各像素px可以包括驱动晶体管tdr、开关晶体管tsw、存储电容器cst以及有机发光二极管el。

69.存储电容器cst可以存储通过数据线dl传输的数据电压dv。在一实施例中,存储电容器cst可以具有:第一电极,连接于驱动晶体管tdr的栅极;以及第二电极,连接于驱动晶体管tdr的源极。

70.开关晶体管tsw可以响应通过垂直扫描线vsl以及水平扫描线hsl从扫描驱动器130接收的扫描信号scan,将数据线dl的数据电压dv传输于存储电容器cst的所述第一电极。在一实施例中,可以是,在第一区间中,数据驱动器120将数据电压dv输出于数据线dl,数据线dl及/或数据线dl的寄生电容器cdl被充电成具有数据电压dv。可以是,在所述第一区间后的第二区间中,数据线dl被浮置,开关晶体管tsw传输充电于数据线dl中的数据电压dv,存储电容器cst存储数据电压dv。另外,在一实施例中,开关晶体管tsw可以具有:栅极,接收扫描信号scan;漏极,连接于数据线dl;以及源极,连接于存储电容器cst的所述第一电极和驱动晶体管tdr的所述栅极。

71.驱动晶体管tdr可以基于存储于存储电容器cst中的数据电压dv而生成驱动电流。在一实施例中,驱动晶体管tdr可以具有:栅极,连接于存储电容器cst的所述第一电极;漏极,接收第一电源电压(例如,高电源电压)elvdd;以及源极,连接于存储电容器cst的所述第二电极。

72.有机发光二极管el可以响应通过驱动晶体管tdr生成的所述驱动电流而发光。在一实施例中,有机发光二极管el可以具有:正极,连接于驱动晶体管tdr的所述源极;以及负极,接收第二电源电压(例如,低电源电压)elvss。

73.另一方面,尽管图2中示出了各像素px具有2t1c结构的例子,但是根据本发明的实施例的像素px不限于图2中示出的示例性结构,可以具有各种结构。

74.在另一实施例中,显示面板110可以是各像素px包括开关晶体管以及连接于所述开关晶体管的液晶电容器的液晶显示(liquid crystal display;lcd)面板。但是,显示面板110不限于所述lcd面板以及所述oled面板,可以是任何的显示面板。

75.在一实施例中,多个水平扫描线hsl和多个垂直扫描线vsl可以一对一连接,但是不限于此。例如,多个水平扫描线hsl的数量可以与多个垂直扫描线vsl的数量彼此相同,但是不限于此。

76.图3中示出了用于说明多个数据线dl、多个水平扫描线hsl以及多个垂直扫描线vsl的配置的一例的显示面板110a的一例。显示面板110a可以包括n个(n是2以上的整数)数据线dl1、dl2、dl3、dl4、dl5、dl6、...、dln-5、dln-4、dln-3、dln-2、dln-1、dln、m个(m是2以上的整数)水平扫描线hsl1、hsl2、...、hslm-1、hslm以及m个垂直扫描线vsl1、vsl2、...、vslm-1、vslm。可以是,m个水平扫描线hsl1~hslm向所述水平方向延伸,n个数据线dl1~dln和m个垂直扫描线vsl1~vslm彼此平行地向所述垂直方向延伸。在一实施例中,在m个垂直扫描线vsl1~vslm中的相邻的两个之间可以配置有n个数据线dl1~dln中的至少一个。例如,可以是,在第一垂直扫描线vsl1与第二垂直扫描线vsl2之间配置有第四、第五以及第六数据线dl4、dl5、dl6,在第m-1垂直扫描线vslm-1与第m垂直扫描线vslm之间配置有第n-2、第n-1以及第n数据线dln-2、dln-1、dln。另一方面,图3中示出了在相邻的两个垂直扫描线(例如,vsl1、vsl2)之间配置有三个数据线(例如,dl4、dl5、dl6)的例子,但是在相邻的两个垂直扫描线之间配置的数据线的数量不限于图3的例子。

77.在一实施例中,可以是,m个水平扫描线hsl1~hslm配置于第一层,m个垂直扫描线

vsl1~vslm配置于与所述第一层不同的第二层,m个水平扫描线hsl1~hslm和m个垂直扫描线vsl1~vslm通过m个接触孔分别连接。例如,如图3所示,第一至第m水平扫描线hsl1~hslm可以分别连接于第一至第m垂直扫描线vsl1~vslm。在此情况下,所述m个接触孔可以在显示面板110a内向对角线方向配置,但是不限于此。

78.图4中示出了用于说明多个水平扫描线hsl和多个垂直扫描线vsl的连接关系的另一例的显示面板110b的另一例。例如,如图4所示,可以是,第奇数个水平扫描线hsl1、hsl3、...、hslm-3、hslm-1连接于左侧一半的垂直扫描线vsl1、vsl2、...、vslm/2-1、vslm/2,第偶数个水平扫描线hsl2、hsl4、

…

、hslm-2、hslm连接于右侧一半的垂直扫描线vslm/2+1、vslm/2+2、

…

、vslm-1、vslm。在此情况下,用于连接m个水平扫描线hsl1~hslm和m个垂直扫描线vsl1~vslm的所述m个接触孔可以在显示面板110b内以v-字形式配置,但是不限于此。

79.另一方面,图3和图4中示出了多个数据线dl、多个水平扫描线hsl以及多个垂直扫描线vsl的配置以及连接关系的例子,但是显示面板110的线dl、hsl、vsl的配置以及连接关系不限于图3以及图4的例子。

80.数据驱动器120可以基于从控制器170接收的图像数据idat以及数据控制信号而生成数据电压dv,通过多个数据线dl将数据电压dv提供于多个像素px。在一实施例中,所述数据控制信号可以包括数据时钟信号dclk以及负载信号load,但是不限于此。

81.扫描驱动器130可以基于从控制器170接收的扫描控制信号而生成扫描信号scan,通过多个垂直扫描线vsl以及多个水平扫描线hsl将扫描信号scan以行单位依次提供于多个像素px。所述扫描控制信号可以包括扫描时钟信号sclk。在一实施例中,所述扫描控制信号可以还包括扫描开始信号等,但是不限于此。

82.如图1所示,由于扫描驱动器130通过多个垂直扫描线vsl以及多个水平扫描线hsl将扫描信号scan提供于多个像素px,因此扫描驱动器130可以还配置于配置有数据驱动器120的显示面板110的一侧(例如,下侧)。由此,能够减小未配置有数据驱动器120以及扫描驱动器130的显示面板110的三个侧中的边框宽度。另一方面,数据驱动器120以及扫描驱动器130仅配置于显示面板110的一侧的结构可以称为单侧驱动(ssd;single side driving)结构。

83.数据驱动器120以及扫描驱动器130可以实现为至少一个数据-扫描集成芯片(或者集成电路(integrated circuit;ic))150。即,单个数据-扫描集成芯片150可以不仅输出数据电压dv还输出扫描信号scan。由此,能够减小用于显示面板110的驱动的芯片(或ic)的芯片尺寸(或ic尺寸)。

84.至少一个数据-扫描集成芯片150可以连接于显示面板110。在一实施例中,如图5所示,数据驱动器120以及扫描驱动器130可以实现为k个(k是1以上的整数)数据-扫描集成芯片151、152、...、154,k个数据-扫描集成芯片151、152、...、154可以在显示面板110上以玻璃覆晶(cog;chip-on-glass)方式或者塑料覆晶(cop;chip-on-plastic)方式安装。在另一实施例中,如图6所示,可以是,k个膜141、142、...、144连接于显示面板110,k个数据-扫描集成芯片151、152、...、154通过k个膜141、142、...、144以薄膜覆晶(cof;chip-on-film)方式连接于显示面板110。

85.在一实施例中,数据-扫描集成芯片150可以包括被数据驱动器120以及扫描驱动

器130共享的至少一个构成要件。在一例中,如图9所示,数据-扫描集成芯片400可以包括被数据驱动器120以及扫描驱动器130共享的共享电平移位器阵列490。在另一例中,如图12所示,数据-扫描集成芯片500可以包括被数据驱动器120以及扫描驱动器130共享的共享输出缓冲器阵列590。在又另一例中,如图14所示,数据-扫描集成芯片600可以包括被数据驱动器120、610以及扫描驱动器130、660共享的共享电平移位器阵列770以及共享输出缓冲器阵列790。在此情况下,能够更加减小用于显示面板110的驱动的芯片(或ic)的芯片尺寸(或ic尺寸),能够减小电力消耗。

86.控制器170(例如,时序控制器(timing controller;tcon))可以从外部的主机(例如,图形处理单元(graphic processing unit;gpu)、图形卡等)接收图像数据idat以及控制信号ctrl的提供。例如,图像数据idat可以是包括红色图像数据、绿色图像数据以及蓝色图像数据的rgb图像数据,但是不限于此。另外,例如,控制信号ctrl可以包括垂直同步信号、水平同步信号、数据使能信号、主时钟信号等,但是不限于此。在一实施例中,控制器170可以执行针对从所述外部的主机接收的图像数据idat的图像处理,并将执行了所述图像处理的图像数据idat提供于数据驱动器120。另外,控制器170可以基于控制信号ctrl而生成所述数据控制信号以及所述扫描控制信号。控制器170可以将图像数据idat以及所述数据控制信号提供于数据驱动器120而控制数据驱动器120的工作,将所述扫描控制信号提供于扫描驱动器130而控制扫描驱动器130的工作。

87.如上所述,在根据本发明的实施例的显示装置100中,数据驱动器120以及扫描驱动器130可以配置于显示面板110的相同侧。由此,能够减小显示面板110的边框宽度。另外,在根据本发明的实施例的显示装置100中,数据驱动器120以及扫描驱动器130可以实现为数据-扫描集成芯片150。由此,能够减小用于显示面板110的驱动的芯片(或ic)的芯片尺寸(或ic尺寸)。在一实施例中,数据-扫描集成芯片150的至少一个构成要件可以被数据驱动器120以及扫描驱动器130共享。在此情况下,能够更加减小所述芯片尺寸(或所述ic尺寸),能够减小所述电力消耗。

88.图7是示出根据本发明的一实施例的数据-扫描集成芯片的框图,图8是用于说明根据本发明的实施例的数据-扫描集成芯片的工作的一例的时序图。

89.参照图7,根据本发明的一实施例的数据-扫描集成芯片200可以包括用于数据驱动器210的第一移位寄存器310、锁存器阵列320、第一电平移位器阵列330、数字-模拟变换器(digital-to-analog converter;dac)阵列340以及第一输出缓冲器阵列350,并包括用于扫描驱动器260的第二移位寄存器360、第二电平移位器阵列370以及第二输出缓冲器阵列380,并且包括数据输出开关阵列290、多个数据输出焊盘dp1、dp2、dp3、dp4、dp5、dp6、...、dpn-2、dpn-1、dpn以及多个扫描输出焊盘sp1、sp2、...、spm。

90.可以是,多个数据输出焊盘dp1~dpn连接于显示面板的多个数据线,多个扫描输出焊盘sp1~spm连接于所述显示面板的多个垂直扫描线。在一实施例中,如图7所示,数据-扫描集成芯片200可以包括n个(n是2以上的整数)数据输出焊盘dp1~dpn以及m个(m是2以上的整数)扫描输出焊盘sp1~spm。在一例中,n可以大于m,但是不限于此。另外,在一实施例中,在m个扫描输出焊盘sp1~spm中的相邻的两个之间可以配置有n个数据输出焊盘dp1~dpn中的至少一个。例如,在第一扫描输出焊盘sp1与第二扫描输出焊盘sp2之间可以配置有第四、第五以及第六数据输出焊盘dp4、dp5、dp6。另一方面,图7中示出了在相邻的两个扫

描输出焊盘(例如,sp1、sp2)之间配置有三个数据输出焊盘(例如,dp4、dp5、dp6)的例子,但是在相邻的两个扫描输出焊盘之间配置的数据输出焊盘的数量不限于图7的例子。

91.第一移位寄存器310可以基于数据时钟信号clk而依次生成采样信号ss。在一实施例中,第一移位寄存器310可以包括依次生成采样信号ss的多个触发器,但是不限于此。

92.锁存器阵列320可以响应采样信号ss而依次存储图像数据idat,响应负载信号load而输出与一行的像素有关的图像数据idat或锁存器输出信号。在一实施例中,锁存器阵列320可以包括:多个采样锁存器,响应采样信号ss而依次存储图像数据idat;以及/或者多个保持锁存器,响应负载信号load而存储及输出与存储于所述多个采样锁存器的一行的像素有关的图像数据idat。

93.第一电平移位器阵列330可以将从锁存器阵列320输出的所述锁存器输出信号的电压电平进行移位。例如,第一电平移位器阵列330可以将所述锁存器输出信号的所述电压电平移位为适合于数字-模拟变换器阵列340的电压电平。在一实施例中,第一电平移位器阵列330可以包括执行移位工作的多个电平移位器。

94.数字-模拟变换器阵列340可以对从第一电平移位器阵列330输出的移位器输出信号执行数字-模拟变换。在一实施例中,数字-模拟变换器阵列340可以包括执行所述数字-模拟变换的多个数字-模拟变换器。

95.第一输出缓冲器阵列350可以将从数字-模拟变换器阵列340输出的变换器输出信号作为图1中示出的数据电压dv输出。在一实施例中,第一输出缓冲器阵列350可以包括用于缓冲数据电压dv的多个输出缓冲器。

96.数据输出开关阵列290可以响应选择信号sel而将第一输出缓冲器阵列350选择性地连接于多个数据输出焊盘dp1~dpn。在一实施例中,数据输出开关阵列290可以包括响应选择信号sel而执行连接工作的多个开关。根据实施例,选择信号sel可以通过图1中示出的控制器170生成,或通过数据-扫描集成芯片200生成。

97.选择信号sel可以在第一区间中具有高电平,在所述第一区间后的第二区间中具有低电平。在此情况下,数据输出开关阵列290可以在所述第一区间中将第一输出缓冲器阵列350连接于多个数据输出焊盘dp1~dpn,在所述第二区间中切断第一输出缓冲器阵列350与多个数据输出焊盘dp1~dpn之间的连接。由此,数据-扫描集成芯片200可以在所述第一区间中将数据电压dv输出于图1中示出的多个数据线dl,在所述第一区间后的所述第二区间中多个数据线dl被浮置。

98.第二移位寄存器360可以基于扫描时钟信号sclk而依次生成扫描信号scan。在一实施例中,第二移位寄存器360可以包括依次生成扫描信号scan的多个级,但是不限于此。

99.第二电平移位器阵列370可以将从第二移位寄存器360输出的扫描信号scan的电压电平进行移位。例如,第二电平移位器阵列370可以将扫描信号scan的所述电压电平移位为适合于多个像素px的开关晶体管的电压电平。在一实施例中,第二电平移位器阵列370可以包括执行移位工作的多个电平移位器。

100.第二输出缓冲器阵列380可以输出从第二电平移位器阵列370输出的扫描信号scan。在一实施例中,第二输出缓冲器阵列380可以包括用于缓冲扫描信号scan的多个输出缓冲器。

101.可以是,通过第二输出缓冲器阵列380输出的扫描信号scan通过多个扫描输出焊

盘sp1~spm提供于图1中示出的多个垂直扫描线vsl,提供于多个垂直扫描线vsl的扫描信号scan通过图1中示出的多个水平扫描线hsl提供于多个像素px。

102.以下,参照图1、图2、图7以及图8,后述根据本发明的实施例的数据-扫描集成芯片200的工作的一例。

103.参照图1、图2、图7以及图8,各帧区间fp可以包括:第一区间p11、p21、...、pm1,输出关于多个像素px的数据电压dv;以及第二区间p12、p22、...、pm2,数据电压dv存储于多个像素px。在各第一区间p11~pm1中,数据-扫描集成芯片200可以将与选择的行的像素px有关的数据电压dv输出于多个数据线dl,数据电压dv充电于多个数据线dl。另外,在第一区间p11~pm1后的相应的第二区间p12~pm2中,数据-扫描集成芯片200可以使多个数据线dl浮置,将扫描信号scan输出于与所述选择的行相对应的垂直扫描线vsl,充电于多个数据线dl的数据电压dv存储于所述选择的行的像素px。

104.例如,如图8所示,控制器170可以将与多个像素px中的第一行的像素px有关的图像数据dat1作为图像数据idat提供于数据-扫描集成芯片200。可以是,第一移位寄存器310生成采样信号ss,锁存器阵列320响应采样信号ss而依次存储与第一行的像素px有关的图像数据dat1。

105.可以是,在与第一行的像素px有关的第一区间p11中,锁存器阵列320响应负载信号load而输出与第一行的像素px有关的图像数据dat1,第一电平移位器阵列330将与第一行的像素px有关的图像数据dat1的电压电平进行移位,数字-模拟变换器阵列340将与第一行的像素px有关的图像数据dat1变换为与第一行的像素px有关的第一数据电压dv1,第一输出缓冲器阵列350输出与第一行的像素px有关的第一数据电压dv1,数据输出开关阵列290响应具有高电平的选择信号sel而将第一输出缓冲器阵列350连接于多个数据输出焊盘dp1~dpn。由此,在与第一行的像素px有关的第一区间p11中,通过多个数据输出焊盘dp1~dpn,与第一行的像素px有关的第一数据电压dv1可以输出于多个数据线dl。由此,多个数据线dl及/或多个数据线dl的寄生电容器cdl可以被充电,以使多个数据线dl的电压v_dl成为与第一行的像素px有关的第一数据电压dv1。

106.可以是,在所述第一区间p11后的与第一行的像素px有关的第二区间p12中,选择信号sel具有低电平,数据输出开关阵列290响应具有所述低电平的选择信号sel而切断第一输出缓冲器阵列350与多个数据输出焊盘dp1~dpn的连接。由此,被充电为与第一行的像素px有关的第一数据电压dv1的多个数据线dl可以被浮置。另外,可以是,第二移位寄存器360基于扫描时钟信号sclk而生成与第一行的像素px有关的第一扫描信号scan1,第二电平移位器阵列370将第一扫描信号scan1的电压电平进行移位,第二输出缓冲器阵列380输出第一扫描信号scan1。因此,在与第一行的像素px有关的第二区间p12中,通过第一扫描输出焊盘sp1、第一垂直扫描线vsl以及第一水平扫描线hsl,第一扫描信号scan1可以提供于第一行的像素px。由此,在与第一行的像素px有关的第二区间p12期间,第一行的像素px的存储电容器cst可以存储充电于多个数据线dl中的第一数据电压dv1。另外,在与第一行的像素px有关的第二区间p12内,锁存器阵列320可以存储与第二行的像素px有关的图像数据dat2。

107.可以是,在所述第二区间p12后的与第二行的像素px有关的第一区间p21中,第一输出缓冲器阵列350输出与第二行的像素px有关的第二数据电压dv2,数据输出开关阵列

290响应具有所述高电平的选择信号sel而将第一输出缓冲器阵列350连接于多个数据输出焊盘dp1~dpn。由此,在与第二行的像素px有关的第一区间p21中,多个数据线dl及/或多个数据线dl的寄生电容器cdl可以被充电,以使多个数据线dl的电压v_dl成为与第二行的像素px有关的第二数据电压dv2。

108.可以是,在所述第一区间p21后的与第二行的像素px有关的第二区间p22中,输出开关阵列290响应具有所述低电平的选择信号sel而切断第一输出缓冲器阵列350与多个数据输出焊盘dp1~dpn的连接,被充电为与第二行的像素px有关的第二数据电压dv2的多个数据线dl可以被浮置。另外,第二移位寄存器360、第二电平移位器阵列370以及第二输出缓冲器阵列380可以输出第二扫描信号scan2。因此,在与第二行的像素px有关的第二区间p22中,通过第二扫描输出焊盘sp2、第二垂直扫描线vsl以及第二水平扫描线hsl,第二扫描信号scan2可以提供于第二行的像素px。由此,在与第二行的像素px有关的第二区间p22期间,第二行的像素px的存储电容器cst可以存储充电于多个数据线dl中的第二数据电压dv2。另外,在与第二行的像素px有关的第二区间p22内,锁存器阵列320可以存储与第三行的像素px有关的图像数据dat3。

109.另外,在与第m行的像素px有关的第一区间pm1中,多个数据线dl及/或多个数据线dl的寄生电容器cdl可以被充电,以使多个数据线dl的电压v_dl成为与第m行的像素px有关的第m数据电压dvm。另外,在所述第一区间pm1后的与第m行的像素px有关的第二区间pm2中,被充电为与第m行的像素px有关的第m数据电压dvm的多个数据线dl可以被浮置。另外,第二移位寄存器360、第二电平移位器阵列370以及第二输出缓冲器阵列380可以输出第m扫描信号scanm。因此,在与第m行的像素px有关的第二区间pm2中,通过第m扫描输出焊盘spm、第m垂直扫描线vsl以及第m水平扫描线hsl,第m扫描信号scanm可以提供于第m行的像素px。由此,在与第m行的像素px有关的第二区间pm2期间,第m行的像素px的存储电容器cst可以存储充电于多个数据线dl中的第m数据电压dvm。以这种方式,数据电压dv可以以行单位依次存储于多个像素px,多个像素px可以基于存储的数据电压dv而发光。

110.图9是示出根据本发明的另一实施例的数据-扫描集成芯片的框图,图10是示出根据本发明的实施例的包括在数据-扫描集成芯片中的电平移位器的一例的电路图,图11是用于说明根据本发明的实施例的数据-扫描集成芯片的工作的一例的时序图。

111.参照图9,根据本发明的另一实施例的数据-扫描集成芯片400可以包括用于数据驱动器的第一移位寄存器410、锁存器阵列420、数字-模拟变换器阵列440以及第一输出缓冲器阵列450,并包括用于扫描驱动器的第二移位寄存器460以及第二输出缓冲器阵列480,并且还包括被所述数据驱动器以及所述扫描驱动器共享的共享电平移位器阵列490。图9的数据-扫描集成芯片400除了代替第一电平移位器阵列330以及第二电平移位器阵列370而包括共享电平移位器阵列490之外,可以具有与图7的数据-扫描集成芯片200相似的结构以及相似的工作。在一实施例中,尽管图9中未示出,但是数据-扫描集成芯片400可以还包括响应选择信号sel而将第一输出缓冲器阵列450选择性地连接于多个数据输出焊盘的图7中示出的数据输出开关阵列290。

112.共享电平移位器阵列490可以包括多个电平移位器ls1、ls2、ls3、...、lsn-2、lsn-1、lsn、移位器输入开关阵列492以及移位器输出开关阵列493。在一实施例中,在显示装置包括n个数据线以及m个垂直扫描线,n大于m的情况下,共享电平移位器阵列490可以包括n

个电平移位器ls1~lsn。另一方面,如图7所示,在数据-扫描集成芯片200包括用于所述数据驱动器的第一电平移位器阵列330以及用于所述扫描驱动器的第二电平移位器阵列370的情况下,数据-扫描集成芯片200可以包括n+m个电平移位器。但是,由于数据-扫描集成芯片400包括被所述数据驱动器以及所述扫描驱动器共享的共享电平移位器阵列490,数据-扫描集成芯片400可以仅包括n个电平移位器ls1~lsn,由此能够更加减小数据-扫描集成芯片400的芯片尺寸(或ic尺寸)。

113.在一实施例中,如图10所示,各电平移位器ls可以包括:第一至第三晶体管t1、t2、t3,串联连接于高电源线vddl与输出反向输出电压voutb的反向输出端子之间;第四晶体管t4,连接于所述反向输出端子与低电源线vssl之间;第五至第七晶体管t5、t6、t7,串联连接于高电源线vddl与输出输出电压vout的输出端子之间;以及第八晶体管t8,连接于所述输出端子与低电源线vssl之间。可以是,第一至第三以及第五至第七晶体管t1、t2、t3、t5、t6、t7实现为pmos晶体管,第四以及第八晶体管t4、t8实现为nmos晶体管。可以是,第一以及第二晶体管t1、t2响应低电平的输入电压vin而导通,第三晶体管t3响应低电平的输出电压vout而导通,第八晶体管t8响应高电平的反向输入电压vinb而导通。由此,电平移位器ls可以响应低电平的输入电压vin以及高电平的反向输入电压vinb而分别输出低电源线vssl的低电源电压dsvss/ssvss以及高电源线vddl的高电源电压dsvdd/ssvdd作为输出电压vout以及反向输出电压voutb。另外,可以是,第五以及第六晶体管t5、t6响应低电平的反向输入电压vinb而导通,第七晶体管t7响应低电平的反向输出电压voutb而导通,第四晶体管t4响应高电平的输入电压vin而导通。由此,电平移位器ls可以响应高电平的输入电压vin以及低电平的反向输入电压vinb而分别输出高电源线vddl的高电源电压dsvdd/ssvdd以及低电源线vssl的低电源电压dsvss/ssvss作为输出电压vout以及反向输出电压voutb。另一方面,尽管图10中示出了电平移位器ls接收差分输入电压vin、vinb并输出差分输出电压vout、voutb的例子,但是电平移位器ls的输入以及输出不限于图10的例子。例如,电平移位器ls可以接收单一(或单端(single-ended))输入信号,并输出单一(或单端)输出信号。另外,尽管图10中示出了电平移位器ls的结构的一例,但是根据本发明的实施例的包括在数据-扫描集成芯片400中的电平移位器ls不限于图10的例子。

114.再次参照图9,移位器输入开关阵列492可以响应选择信号sel而将锁存器阵列420的输出端子连接于多个电平移位器ls1~lsm的输入端子,响应反向选择信号selb而将第二移位寄存器460的输出端子连接于多个电平移位器ls1~lsm的所述输入端子。在一实施例中,移位器输入开关阵列492可以包括:n个输入开关,响应选择信号sel而执行连接工作;以及m个输入开关,响应反向选择信号selb而执行连接工作。另外,移位器输出开关阵列493可以响应选择信号sel而将多个电平移位器ls1~lsm的输出端子连接于数字-模拟变换器阵列440的输入端子,响应反向选择信号selb而将多个电平移位器ls1~lsm的所述输出端子连接于第二输出缓冲器阵列480的输入端子。在一实施例中,移位器输出开关阵列493可以包括:n个输出开关,响应选择信号sel而执行连接工作;以及m个输出开关,响应反向选择信号selb而执行连接工作。由此,共享电平移位器阵列490可以在选择信号sel具有高电平的期间连接于用于所述数据驱动器的锁存器阵列420与数字-模拟变换器阵列440之间,并在反向选择信号selb具有高电平的期间连接于用于所述扫描驱动器的第二移位寄存器460与第二输出缓冲器阵列480之间。

115.在一实施例中,共享电平移位器阵列490可以还包括:第一移位器高电源开关496,响应选择信号sel而将数据移位器高电源电压dsvdd传输于共享电平移位器阵列490的高电源线vddl;第二移位器高电源开关497,响应反向选择信号selb而将扫描移位器高电源电压ssvdd传输于共享电平移位器阵列490的高电源线vddl;第一移位器低电源开关498,响应选择信号sel而将数据移位器低电源电压dsvss传输于共享电平移位器阵列490的低电源线vssl;以及第二移位器低电源开关499,响应反向选择信号selb而将扫描移位器低电源电压ssvss传输于共享电平移位器阵列490的低电源线vssl。由此,可以是,在选择信号sel具有高电平的期间,用于所述数据驱动器的电平移位器的数据移位器高电源电压dsvdd以及数据移位器低电源电压dsvss供应于多个电平移位器ls1~lsm,在反向选择信号selb具有高电平的期间,用于所述扫描驱动器的电平移位器的扫描移位器高电源电压ssvdd以及扫描移位器低电源电压ssvss供应于多个电平移位器ls1~lsm。

116.如上所述,根据本发明的另一实施例的数据-扫描集成芯片400可以包括被所述数据驱动器以及所述扫描驱动器共享的共享电平移位器阵列490。由此,能够更加减小根据本发明的另一实施例的数据-扫描集成芯片400的芯片尺寸(或ic尺寸),能够减小电力消耗。

117.以下,参照图9以及图11后述根据本发明的另一实施例的数据-扫描集成芯片400的工作的一例。

118.参照图9以及图11,可以是,在与第一行的像素px有关的第一区间p11中,选择信号sel具有高电平,反向选择信号selb具有低电平。由此,共享电平移位器阵列490可以连接于锁存器阵列420与数字-模拟变换器阵列440之间。由此,可以是,数据-扫描集成芯片400将与第一行的像素px有关的第一数据电压dv1输出于多个数据线dl,多个数据线dl被充电为与第一行的像素px有关的第一数据电压dv1。

119.可以是,在所述第一区间p11后的与第一行的像素px有关的第二区间p12中,选择信号sel具有低电平,反向选择信号selb具有高电平。由此,共享电平移位器阵列490可以连接于第二移位寄存器460与第二输出缓冲器阵列480之间。另外,被充电为与第一行的像素px有关的第一数据电压dv1的多个数据线dl可以被图7中示出的数据输出开关阵列290浮置。可以是,数据-扫描集成芯片400将第一扫描信号scan1提供于第一行的像素px,第一行的像素px存储充电于多个数据线dl中的第一数据电压dv1。

120.可以是,在所述第二区间p12后的与第二行的像素px有关的第一区间p21中,选择信号sel具有高电平,反向选择信号selb具有低电平,共享电平移位器阵列490连接于锁存器阵列420与数字-模拟变换器阵列440之间。可以是,数据-扫描集成芯片400将与第二行的像素px有关的第二数据电压dv2输出于多个数据线dl,多个数据线dl被充电为与第二行的像素px有关的第二数据电压dv2。可以是,在所述第一区间p21后的与第二行的像素px有关的第二区间p22中,选择信号sel具有低电平,反向选择信号selb具有高电平,共享电平移位器阵列490连接于第二移位寄存器460与第二输出缓冲器阵列480之间,多个数据线dl被浮置。可以是,数据-扫描集成芯片400将第二扫描信号scan2提供于第二行的像素px,第二行的像素px存储充电于多个数据线dl中的第二数据电压dv2。

121.另外,可以是,在与第m行的像素px有关的第一区间pm1中,选择信号sel具有高电平,反向选择信号selb具有低电平,共享电平移位器阵列490连接于锁存器阵列420与数字-模拟变换器阵列440之间。可以是,数据-扫描集成芯片400将与第m行的像素px有关的第m数

据电压dvm输出于多个数据线dl,多个数据线dl被充电为与第m行的像素px有关的第m数据电压dvm。可以是,在所述第一区间pm1后的与第m行的像素px有关的第二区间pm2中,选择信号sel具有低电平,反向选择信号selb具有高电平,共享电平移位器阵列490连接于第二移位寄存器460与第二输出缓冲器阵列480之间,多个数据线dl被浮置。可以是,数据-扫描集成芯片400将第m扫描信号scanm提供于第m行的像素px,第m行的像素px存储充电于多个数据线dl中的第m数据电压dvm。以这种方式,数据电压dv1、dv2、...、dvm可以以行单位依次存储于多个像素px,多个像素px可以基于存储的数据电压dv1、dv2、...、dvm而发光。

122.图12是示出根据本发明的又另一实施例的数据-扫描集成芯片的框图,图13是示出根据本发明的实施例的包括在数据-扫描集成芯片中的输出缓冲器的一例的框图。

123.参照图12,根据本发明的又另一实施例的数据-扫描集成芯片500可以包括用于数据驱动器的第一移位寄存器510、锁存器阵列520、第一电平移位器阵列530以及数字-模拟变换器阵列540,并包括用于扫描驱动器的第二移位寄存器560以及第二电平移位器阵列570,并且还包括被所述数据驱动器以及所述扫描驱动器共享的共享输出缓冲器阵列590。图12的数据-扫描集成芯片500除了代替第一输出缓冲器阵列350以及第二输出缓冲器阵列380而包括共享输出缓冲器阵列590之外,可以具有与图7的数据-扫描集成芯片200相似的结构以及相似的工作。

124.共享输出缓冲器阵列590可以包括多个输出缓冲器ob1、ob2、ob3、...、obn-2、obn-1、obn、缓冲器输入开关阵列592以及缓冲器输出开关阵列593。在一实施例中,在显示装置包括n个数据线以及m个垂直扫描线,n大于m的情况下,共享输出缓冲器阵列590可以包括n个输出缓冲器ob1~obn。另一方面,如图7所示,在数据-扫描集成芯片200包括用于所述数据驱动器的第一输出缓冲器阵列350以及用于所述扫描驱动器的第二输出缓冲器阵列380的情况下,数据-扫描集成芯片200可以包括n+m个输出缓冲器。但是,由于数据-扫描集成芯片500包括被所述数据驱动器以及所述扫描驱动器共享的共享输出缓冲器阵列590,数据-扫描集成芯片500可以仅包括n个输出缓冲器ob1~obn,由此能够更加减小数据-扫描集成芯片500的芯片尺寸(或ic尺寸)。

125.在一实施例中,如图13所示,各输出缓冲器ob可以包括具有输入端子、反向输入端子以及输出端子的放大器amp。放大器amp可以从所述输入端子接收输入电压vin,所述反向输入端子和所述输出端子彼此连接。放大器amp可以在所述输出端子处输出与输入电压vin实质上相同的输出电压vout。另外,放大器amp可以接收高电源电压vdd以及低电源电压vss的供应。在一实施例中,可以是,放大器amp的高电源电压vdd的电压电平被确定为用于所述数据驱动器的输出缓冲器的数据缓冲器高电源电压与用于所述扫描驱动器的输出缓冲器的扫描缓冲器高电源电压中高的电压的电压电平,放大器amp的低电源电压vss的电压电平被确定为用于所述数据驱动器的输出缓冲器的数据缓冲器低电源电压与用于所述扫描驱动器的输出缓冲器的扫描缓冲器低电源电压中低的电压的电压电平。由此,各输出缓冲器ob可以作为所述数据驱动器的输出缓冲器以及所述扫描驱动器的输出缓冲器正常地工作。另一方面,尽管图13中示出了输出缓冲器ob的结构的一例,但是根据本发明的实施例的包括在数据-扫描集成芯片500中的输出缓冲器ob不限于图13的例子。

126.再次参照图12,缓冲器输入开关阵列592可以响应选择信号sel而将数字-模拟变换器阵列540的输出端子连接于多个输出缓冲器ob1~obn的输入端子,响应反向选择信号

selb而将第二电平移位器阵列570的输出端子连接于多个输出缓冲器ob1~obn的所述输入端子。在一实施例中,缓冲器输入开关阵列592可以包括:n个输入开关,响应选择信号sel而执行连接工作;以及m个输入开关,响应反向选择信号selb而执行连接工作。另外,缓冲器输出开关阵列593可以响应选择信号sel而将多个输出缓冲器ob1~obn的输出端子连接于多个数据输出焊盘dp1~dpn,并响应反向选择信号selb而将多个输出缓冲器ob1~obn的所述输出端子连接于多个扫描输出焊盘sp1~spm。在一实施例中,缓冲器输出开关阵列593可以包括:n个输出开关,响应选择信号sel而执行连接工作;以及m个输出开关,响应反向选择信号selb而执行连接工作。由此,共享输出缓冲器阵列590可以在选择信号sel具有高电平的期间连接于用于所述数据驱动器的数字-模拟变换器阵列540与多个数据输出焊盘dp1~dpn之间,在反向选择信号selb具有高电平的期间连接于用于所述扫描驱动器的第二电平移位器阵列570与多个扫描输出焊盘sp1~spm之间。

127.如上所述,根据本发明的又另一实施例的数据-扫描集成芯片500可以包括被所述数据驱动器以及所述扫描驱动器共享的共享输出缓冲器阵列590。由此,能够更加减小根据本发明的又另一实施例的数据-扫描集成芯片500的芯片尺寸(或ic尺寸),能够减小电力消耗。

128.以下,参照图11以及图12,后述根据本发明的另一实施例的数据-扫描集成芯片500的工作的一例。

129.参照图11以及图12,可以是,在与第一行的像素px有关的第一区间p11中,选择信号sel具有高电平,反向选择信号selb具有低电平,共享输出缓冲器阵列590连接于数字-模拟变换器阵列540与多个数据输出焊盘dp1~dpn之间。可以是,数据-扫描集成芯片500将与第一行的像素px有关的第一数据电压dv1输出于多个数据线dl,多个数据线dl被充电为与第一行的像素px有关的第一数据电压dv1。可以是,在所述第一区间p11后的与第一行的像素px有关的第二区间p12中,选择信号sel具有低电平,反向选择信号selb具有高电平,共享输出缓冲器阵列590连接于第二电平移位器阵列570与多个扫描输出焊盘sp1~spm之间,多个数据线dl被浮置。可以是,数据-扫描集成芯片500将第一扫描信号scan1提供于第一行的像素px,第一行的像素px存储充电于多个数据线dl中的第一数据电压dv1。

130.可以是,在所述第二区间p12后的与第二行的像素px有关的第一区间p21中,选择信号sel具有高电平,反向选择信号selb具有低电平,共享输出缓冲器阵列590连接于数字-模拟变换器阵列540与多个数据输出焊盘dp1~dpn之间。可以是,数据-扫描集成芯片500将与第二行的像素px有关的第二数据电压dv2输出于多个数据线dl,多个数据线dl被充电为与第二行的像素px有关的第二数据电压dv2。可以是,在所述第一区间p21后的与第二行的像素px有关的第二区间p22中,选择信号sel具有低电平,反向选择信号selb具有高电平,共享输出缓冲器阵列590连接于第二电平移位器阵列570与多个扫描输出焊盘sp1~spm之间,多个数据线dl被浮置。可以是,数据-扫描集成芯片500将第二扫描信号scan2提供于第二行的像素px,第二行的像素px存储充电于多个数据线dl中的第二数据电压dv2。

131.另外,可以是,在与第m行的像素px有关的第一区间pm1中,选择信号sel具有高电平,反向选择信号selb具有低电平,共享输出缓冲器阵列590连接于数字-模拟变换器阵列540与多个数据输出焊盘dp1~dpn之间。可以是,数据-扫描集成芯片500将与第m行的像素px有关的第m数据电压dvm输出于多个数据线dl,多个数据线dl被充电为与第m行的像素px

console)、导航仪(navigation)等之类任意的电子设备。

146.以上,参照本发明的实施例进行了说明,但是本技术领域的熟练的人员可以理解在不超出权利要求书中记载的本发明的构思和领域的范围内可以对本发明进行多种修改和变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1