显示控制器、显示设备以及显示控制器的控制方法与流程

1.本公开涉及显示技术领域,具体涉及一种显示控制器、显示设备以及显示设备的控制方法。

背景技术:

2.随着信息科学技术的发展,显示技术也得到了发展。基于有机发光二极管(organic electroluminescence display,oled)的显示技术具有自发光、视角广、响应快、可弯曲和柔性化等特点,是显示技术领域的较为重要的突破,提高了视觉效果。

技术实现要素:

3.本公开实施例提供了一种显示控制器、显示设备以及显示控制器的控制方法。

4.本公开实施例提供了一种显示控制器,包括:渲染电路,被配置为接收显示数据并对接收到的显示数据执行渲染,所述显示数据的刷新率是显示面板的刷新率的k倍,其中k为大于1的整数;存储器,被配置为存储补偿数据;补偿电路,与所述渲染电路和所述存储器连接,并且被配置为基于所述存储器中的补偿数据对渲染电路渲染后的显示数据执行补偿,得到补偿后的显示数据;以及,驱动电路,与所述补偿电路连接,并且被配置为基于所述补偿电路提供的所述补偿后的显示数据来产生驱动控制信号,所述驱动控制信号用于在k个时段中的每个时段驱动显示面板包含的n行子像素中的n/k行子像素,其中n为大于1的整数,且n/k为大于或等于1的整数。

5.例如,所述补偿电路包括第一补偿子电路和第二补偿子电路,所述补偿数据包括第一补偿数据和第二补偿数据,所述存储器包括用于存储第一补偿数据的第一存储器和用于存储第二补偿数据的第二存储器,其中,所述第一补偿子电路与所述渲染电路和所述第一存储器连接,并且被配置为基于所述第一存储器中存储的第一补偿数据,对渲染电路渲染后的显示数据执行去烧屏处理,得到去烧屏处理后的显示数据;以及,所述第二补偿子电路与所述第一补偿子电路、所述第二存储器和所述驱动电路连接,并且被配置为基于所述第二存储器中存储的第二补偿数据对所述第一补偿子电路提供的所述去烧屏处理后的显示数据执行去摩尔纹处理以得到去摩尔纹处理后的显示数据,并将所述去摩尔纹处理后的显示数据作为所述补偿后的显示数据提供至所述驱动电路。

6.例如,k=2,所述驱动控制信号用于在第一时段驱动显示面板中的奇数行子像素,在第二时段驱动显示面板中的偶数行子像素。

7.例如,所述渲染电路接收的显示数据的刷新率是240hz,所述显示面板的刷新率是120hz。

8.例如,所述第一存储器和第二存储器均为随机存取存储器。

9.例如,还包括闪存存储器,所述闪存存储器与所述第一存储器和所述第二存储器连接,用于向所述第一存储器提供所述第一存储数据以及向所述第二存储器提供所述第二存储数据。

10.例如,所述渲染电路、所述存储器、所述补偿电路和所述驱动电路集成为芯片,所述闪存存储器是所述芯片的外接存储器。

11.本公开实施例还提供了一种显示设备,包括:如上所述的显示控制器;以及,显示面板,与所述显示控制器连接,并且被配置为根据所述显示控制器提供的驱动控制信号来进行显示。

12.例如,所述显示面板包括:n行子像素,其中n为大于1的整数;栅极驱动电路,与显示控制器和所述n行子像素连接,并且被配置为基于所述显示控制器提供的驱动控制信号向所述n行子像素提供栅极驱动信号;以及,源极驱动电路,与显示控制器和所述n行子像素连接,并且被配置为基于所述显示控制器提供的驱动控制信号向所述n行子像素提供数据信号。

13.例如,所述栅极驱动电路包括n级级联的移位寄存器单元,其中第n级移位寄存器单元与第n行子像素连接,并且第n级移位寄存器单元的输出端与第n+i级移位寄存器单元的输入端连接,其中n为整数且1≤n<n,i为大于1的整数。

14.例如,其中,k=2,i=2。

15.本公开实施例提供了一种如上所述的显示控制器的控制方法,包括:渲染电路接收显示数据并对接收到的显示数据执行渲染,所述显示数据的刷新率是显示面板的刷新率的k倍,其中k为大于1的整数;补偿电路基于所述存储器中的补偿数据对渲染电路渲染后的显示数据执行补偿,得到补偿后的显示数据;以及,驱动电路基于所述补偿电路提供的所述补偿后的显示数据来产生驱动控制信号,所述驱动控制信号用于在k个时段中的每个使得驱动显示面板包含的n行子像素中的n/k行子像素,其中n为大于1的整数,且n/k为大于或等于1的整数。

16.例如,驱动电路在第一时段驱动显示面板中的奇数行子像素,在第二时段驱动显示面板中的偶数行子像素。

附图说明

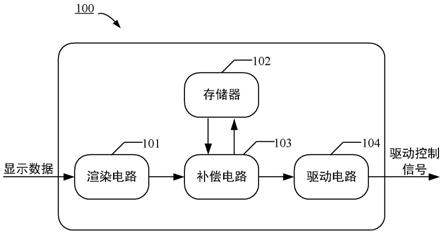

17.图1示意性示出了根据本公开实施例的显示控制器的框图;

18.图2示意性示出了根据本公开另一实施例的显示控制器的框图;

19.图3示意性示出了根据本公开另一实施例的显示控制器的框图;

20.图4示意性示出了根据本公开实施例的显示设备的框图;

21.图5示意性示出了根据本公开另一实施例的显示设备的框图;

22.图6示意性示出了根据本公开实施例的栅极驱动电路的示例结构图;

23.图7示意性示出了根据本公开实施例的显示设备的信号时序图;以及

24.图8示意性示出了根据本公开实施例的显示控制器的控制方法的流程图。

具体实施方式

25.虽然将参照含有本公开的较佳实施例的附图充分描述本公开,但在此描述之前应了解本领域的普通技术人员可修改本文中所描述的公开,同时获得本公开的技术效果。因此,须了解以上的描述对本领域的普通技术人员而言为一广泛的揭示,且其内容不在于限制本公开所描述的示例性实施例。

26.另外,在下面的详细描述中,为便于解释,阐述了许多具体的细节以提供对本公开实施例的全面理解。然而明显地,一个或多个实施例在没有这些具体细节的情况下也可以被实施。在其他情况下,公知的结构和装置以图示的方式体现以简化附图。

27.基于oled的驱动架构可以包括ap(application processor,应用处理器)端、ic(integrated circuit,集成电路)端。ap端与ic端可以基于接口实现数据交互,以驱动显示面板的显示。例如,如果ap为移动应用处理器,则可以基于mipi(mobile industry processor interface,移动行业处理器接口)实现ap端与ic端之间的数据交互。mipi的传输模式可以包括命令模式(即command mode)和视频模式(即video mode)。如果ap端与ic端基于mipi的命令模式实现数据交互,则需要利用ic端具备帧缓存能力。ap端先将显示数据通过帧存储器发送至编码器,利用编码器对显示数据执行编码,得到编码后的显示数据。然后,ap端将编码后的显示数据发送至ic端的帧缓存。ic端先利用解码器对存储于帧缓存的编码后的显示数据执行解码,得到解码后的显示数据,基于解码后的显示数据来进行诸如渲染、补偿之类的处理,从而产生驱动控制信号以控制显示面板根据驱动控制信号来进行显示。然而这种方式下,ic端结构复杂,功耗较高。

28.图1示意性示出了根据本公开实施例的显示控制器的框图。

29.如图1所示,显示控制器100包括渲染电路101、存储器102、补偿电路103和驱动电路104。

30.渲染电路101可以接收显示数据并对接收到的显示数据执行渲染,显示数据的刷新率是显示面板的刷新率的k倍,k为大于1的整数。

31.存储器102可以为存储补偿数据。

32.补偿电路103与渲染电路101和存储器102连接。补偿电路103可以基于存储器102中的补偿数据对渲染电路101渲染后的显示数据执行补偿,得到补偿后的显示数据。

33.驱动电路104与补偿电路连接。驱动电路104可以基于补偿电路103提供的补偿后的显示数据来产生驱动控制信号,驱动控制信号用于在k个时段中的每个时段驱动显示面板包含的n行子像素中的n/k行子像素,n为大于1的整数,且n/k为大于或等于1的整数。

34.根据本公开的实施例,显示数据可以指来自的ap端的显示数据。补偿数据可以指能够提高显示数据的显示效果的数据。补偿数据可以包括一个或多个。补偿数据可以预先存储于显示控制器中。例如,补偿数据可以包括以下至少一项:用于对由烧屏问题导致的显示数据的缺陷进行补偿的补偿数据和用于对由摩尔纹(即mura)导致的显示数据的缺陷进行补偿的补偿数据。补偿数据可以根据显示数据确定。

35.根据本公开的实施例,存储器102可以包括一个或多个。存储器102可以包括随机存取存储器(random access memory,ram)或闪存存储器(flash electrically erasable programmable read only memory,flash eprom)。驱动控制信号可以指用于驱动显示面板包含的子像素的控制信号。驱动控制信号可以包括栅极驱动信号和数据信号。驱动控制信号还可以包括其他控制信号。例如,与数据信号相关的控制信号和与栅极驱动相关的控制信号。

36.根据本公开的实施例,渲染电路101可以利用渲染算法对来自ap端的显示数据执行渲染,得到渲染后的显示数据。例如,渲染算法可以包括子像素渲染(sub pixel rendering,spr)算法。显示数据的刷新率可以为显示面板的刷新率的k倍。k可以为大于1的

整数。k的数值可以根据实际业务需求进行配置,在此不作限定。例如,显示数据的刷新率是240hz。在k=2的情况下,显示面板的刷新率是120hz。在k=4的情况下,显示面板的刷新率是60hz。

37.根据本公开的实施例,在获得渲染后的显示数据之后,补偿电路103可以基于存储于存储器102的补偿数据对渲染后的显示数据执行渲染,得到补偿后的显示数据。

38.根据本公开的实施例,驱动电路104可以基于补偿后的显示数据来产生驱动控制信号。驱动控制信号可以针对k个时段中的每个时段,能够实现驱动与该时段对应的显示面板包含的部分行子像素。部分行子像素可以包括n/k行子像素。不同时段驱动的子像素可以不同,即,不同时段驱动的n/k行子像素之间无重复。

39.根据本公开的实施例,与每个时段对应的n/k行子像素可以是以间隔驱动方式得到的n/k行子像素。例如,与每个时段对应的n/k行子像素可以是以每间隔(k-1)行子像素的方式得到的n/k行子像素。即,驱动控制信号能够实现按照每间隔(k-1)行子像素的方式,驱动与每个时段对应的显示面板包含的n/k行子像素。

40.根据本公开的实施例,与每个时段对应的n/k行子像素还可以是按照混合驱动方式得到的n/k行子像素。混合驱动可以包括间隔驱动和逐行驱动,即,与每个时段对应的n/k行子像素可以包括以逐行驱动方式得到的t行子像素和以间隔驱动方式得到的s行子像素。t和s均为大于或等于1的整数,且n/k=t+s。

41.例如,与每个时段对应的n/k行子像素可以是以每间隔(k-1)行子像素的方式得到的n/k行子像素。

42.在k=2的情况下,k个时段段包括第一时段和第二时段。与第一时段和第二时段对应的n/2行子像素可以是以每间隔一行子像素的方式得到的n/2行子像素。即,如果n是偶数,则与第一时段对应的n/2行子像素包括第一行子像素、第三行子像素、

……

、第n-3行子像素和第n-1行子像素。与第二时段对应的n/2行子像素包括第二行子像素、第四行子像素、

……

、第n-2行子像素和第n行子像素。如果n是奇数,则与第一时段对应的n/2行子像素包括第一行子像素、第三行子像素、

……

、第n-2行子像素和第n行子像素。与第二时段对应的n/2行子像素包括第二行子像素、第四行子像素、

……

、第n-3行子像素和第n-1行子像素。

43.在k=3的情况下,k个时段包括第一时段、第二时段和第三时段。与第一时段、第二时段和第三时段对应的n/3行子像素可以是以每间隔两行子像素的方式得到的n/3行子像素。即,与第一时段对应的n/3行子像素包括第一行子像素、第四行子像素、第七行子像素,以此类推。与第二时段对应的n/3行子像素包括第二行子像素、第五行子像素、第八行子像素,以此类推。与第三时段对应的n/3行子像素可以包括第三行子像素、第六行子像素、第九行子像素,以此类推。

44.本公开实施例的显示控制器通过利用渲染电路接收刷新率是显示面板k倍的显示数据,并利用驱动电路来产生驱动总行数1/k的子像素行,使得能够无需缓存和解码器,即可实现正常显示。由于省略了缓存和解码器,简化了显示控制器的结构,从而可以降低功耗。

45.图2示意性示出了根据本公开另一实施例的显示控制器的框图。图2的显示控制器200与上述显示控制器100类似,以上对于显示控制器100的描述同样适用于本实施例。为了便于描述,下面将主要对区别部分进行详细说明。

46.如图2所示,显示控制器200包括渲染电路101、存储器、补偿电路和驱动电路104。在图2中,补偿电路可以包括第一补偿子电路1030和第二补偿子电路1031。补偿数据包括第一补偿数据和第二补偿数据。存储器102可以包括用于存储第一补偿数据的第一存储器1020和用于存储第二补偿数据的第二存储器1021。例如,第一存储器1020和第二存储器1021均可以为随机存取存器(ram,random access memory)。

47.第一补偿子电路1030与渲染电路101和第一存储器1020连接。第一补偿子电路1030可以基于第一存储器1020中存储的第一补偿数据,对渲染电路101渲染后的显示数据执行去烧屏(deburn-in)处理,得到去烧屏处理后的显示数据。

48.第二补偿子电路1031与第一补偿子电路1030、第二存储器1021和驱动电路104连接。第二补偿子电路1031可以基于第二存储器1021中存储的第二补偿数据对第一补偿子电路提供的去烧屏处理后的显示数据执行去摩尔纹(demura)处理以得到去摩尔纹处理后的显示数据,并将去摩尔纹处理后的显示数据作为补偿后的显示数据提供至驱动电路104。

49.根据本公开的实施例,第一补偿数据可以指用于对烧屏问题导致的显示数据的缺陷进行补偿的补偿数据。第二补偿数据可以是用于对由摩尔纹导致的显示数据的缺陷进行补偿的补偿数据。摩尔纹可以指在显示面板制造过程中,不同膜层厚度不均匀,导致在电学和光学上均一性较差,使得用户在观看显示面板时呈现出色彩不均匀的现象。摩尔纹处理可以指对显示面板的色彩不均匀显示进行亮度补偿,使得色彩较为均匀。

50.在工作中,渲染电路101对接收到的显示数据进行渲染。第一补偿子电路1030可以基于存储于第一存储器1020的第一补偿数据对渲染电路101渲染后的显示数据执行去烧屏处理,得到去烧屏处理后的显示数据。第二补偿子电路1031可以对第一补偿子电路1030去烧屏处理后的显示数据执行摩尔纹处理,得到摩尔纹处理后的显示数据并提供给驱动电路。驱动电路104可以基于第二补偿电路1031提供的补偿后的显示数据来产生驱动控制信号。

51.根据本公开的实施例,k=2。在这种情况下,渲染电路101接收的显示数据的刷新率是显示面板的刷新率的2倍。例如渲染电路101接收刷新率为240hz的显示数据,显示面板的刷新率是120hz。驱动电路104产生的驱动控制信号可以用于在第一时段驱动显示面板中的奇数行子像素,在第二时段驱动显示面板中的偶数行子像素。例如,可以在第一时段按照第1行、第三行、第五行

……

的顺序驱动显示面板的奇数行子像素发光,然后在第二时段按照第二行、第四行、第六行的顺序驱动偶数行子像素发光。通过这种方式,实现了奇数行子像素与偶数行子像素的交叉驱动。可以看出,即使接收到的显示数据的刷新率是显示面板的刷新率的两倍,本公开实施例的显示控制器仍然能够控制显示面板以显示面板自身的刷新率来实现显示扫描,从而保证显示面板的正常显示效果。在显示面板的刷新率为120hz的情况下,利用40nm工艺制程的ic进行测试,相比于相关技术,显示控制器的功耗可以降低约37mw。

52.图3示意性示出了根据本公开另一实施例的显示控制器的框图。图3的显示控制器300与上述显示控制器200类似,区别至少在于还包括闪存存储器105。为了便于描述,下面将主要对区别部分进行详细说明。

53.如图3所示,显示控制器300还可以包括闪存存储器105。闪存存储器105与第一存储器1020和第二存储器1021连接。闪存存储器105可以向第一存储器1020提供第一补偿数

据以及向第二存储器1021提供第二补偿数据。

54.由于第一存储器1020和第二存储器1021均是随机存取存储器,具有易失性。闪存存储器105可以在断电的情况下,不丢失存储的数据。因此,第一存储器1020和第二存储器1021断电清除数据后,如果需要再次使用补偿数据,可以从闪存存储器105重新加载补偿数据,保证操作的正常执行。根据本公开的实施例,渲染电路101、存储器102、补偿电路103和驱动电路104可以集成为芯片,闪存存储器105可以是芯片的外接存储器。

55.图4示意性示出了根据本公开实施例的显示设备的框图。

56.如图4所示,显示设备400可以包括显示控制器401和显示面板402。

57.显示控制器401可以实现为上述任意实施例的显示控制器,例如显示控制器100、200或300。

58.显示面板402与显示控制器401连接。显示面板402可以根据显示控制器401提供的驱动控制信号来进行显示。

59.根据本公开的实施例,显示控制器401可以对接收到的显示数据执行渲染,得到渲染后的显示数据,基于补偿数据对渲染后的显示数据执行补偿,得到补偿后的显示数据,并基于补偿后的显示数据来产生驱动控制信号。显示面板402可以根据显示控制器401提供的驱动控制信号,在k个时段中的每个时段显示面板包含的n行子像素中的n/k行子像素。

60.图5示意性示出了根据本公开另一实施例的显示设备的框图。

61.如图5所示,显示设备500包括显示控制器501和显示面板502。

62.显示控制器501可以由上述任意实施例的显示控制器来实现。在本实施例中,显示控制器501实现为与上述显示控制器300具有相同的结构,这里不再赘述。

63.显示面板502可以包括多个子像素p、栅极驱动电路202和源极驱动电路203。

64.多个子像素p可以布置成n行,n为大于1的整数。例如多个子像素p可以布置成阵列形式。

65.栅极驱动电路202与显示控制器501和n行子像素p连接。栅极驱动电路202可以基于显示控制器501提供的驱动控制信号向n行子像素p提供栅极驱动信号。

66.源极驱动电路203与显示控制器501和n行子像素201连接。源极驱动电路203可以基于显示控制器501提供的驱动控制信号向n行子像素p提供数据信号。

67.根据本公开的实施例,显示控制器501提供的驱动控制信号可以包括栅极驱动信号和数据信号。n行子像素201可以包括n

×

m个子像素p。n

×

m个子像素p布置成n

×

m阵列。m可以为大于1的整数。栅极驱动信号可以包括n个,即,第一栅极驱动信号g1、第二栅极驱动信号g2、

……

、第n-1栅极驱动信号gn-1和第n栅极确定信号gn。数据信号可以包括m个,即第一数据信号d1、第二数据信号d2、

……

、第m-1数据信号dm-1和第m数据信号dm。

68.根据本公开的实施例,栅极驱动电路202可以与n

×

m个子像素p连接。栅极驱动电路202可以通过沿第一方向(图5中为x方向)延伸的多条栅极信号线分别与n行子像素201连接。多条栅极信号线可以包括n条,即,第一栅极信号线、第二栅极信号线、

……

、第n-1栅极信号线和第n栅极信号线。

69.例如,栅极驱动电路201可以通过第一栅极信号线连接第一行子像素p,以向第一行子像素p提供第一栅极驱动信号g1。通过第二栅极信号线连接第二行子像素p以向第二行子像素p提供第二栅极驱动信号g2,以此类推。第一行子像素p响应于接收到第一栅极驱动

信号g1而开启,第二行子像素p响应于接收到第二栅极驱动信号g2而开启,以此类推。

70.根据本公开的实施例,栅极驱动电路202可以每间隔至少一行或多行来驱动n行子像素201,以依次开启部分行的子像素p。例如,栅极驱动电路202可以每间隔一行来驱动n行子像素201依次开启奇数行子像素p,即,可以依次开启第一行子像素p、第三行子像素p、第五行子像素p,以此类推;然后可以依次开启第二行子像素p、第四行子像素p、第六行子像素p,以此类推。

71.根据本公开的实施例,源极驱动电路203可以与n

×

m个子像素p连接。源极驱动电路203可以通过沿第二方向(图5中为y方向)延伸的多条数据线分别与m列子像素p连接。多条源极信号线可以包括m条,即,第一源极信号线、第二源极信号线、

……

、第m-1源极信号线和第m源极信号线。

72.例如,源极驱动电路203可以通过第一数据线连接第一列子像素p,以向第一列子像素p提供第一数据信号d1。通过第二数据线连接第二列子像素p,以向第二列子像素p提供第二数据信号d2,以此类推。

73.例如,在第一行子像素p开启的情况下,源极驱动电路203可以通过m条数据线分别向第一行子像素p包括的m个子像素提供针对第一行子像素的m个数据信号。在第二行子像素p开启的情况下,源极驱动电路203可以通过m条数据线分别向第二行子像素p包括的m个子像素提供针对第二行子像素p的m个数据信号,以此类推。

74.图6示意性示出了根据本公开实施例的栅极驱动电路的示例结构图。

75.如图6所示,栅极驱动电路202可以包括n个级联的移位寄存器单元,即,移位寄存器单元goa1、移位寄存器单元goa2、

……

、移位寄存器单元goan、

……

、移位寄存器单元goan-1和移位寄存器单元goan。为了简明起见仅示出了第一至第四级一位寄存器单元goa1至goa4。

76.根据本公开的实施例,每个移位寄存器单元可以具有输入端in和输出端out。第n级移位寄存器单元的输出的与第n行子像素连接。例如第一级移位寄存器goa1的输出的out与第一行子像素a/a1连接,第二级移位寄存器goa2的输出的out与第二行子像素a/a2连接,第三级移位寄存器goa3的输出的out与第三行子像素a/a3连接,以此类推。

77.根据本公开的实施例,第n级移位寄存器单元的输出端与第n+i级移位寄存器单元的输入端连接。n为整数且1≤n<n,i为大于1的整数。在图6中,k=2,i=2,第一级移位寄存器单元goal的输出端out连接第三级移位寄存器单元goa3的输入端in,第二级移位寄存器单元goa2的输出的out连接第四级移位寄存器单元goa4的输入端,以此类推。第一级移位寄存器单元goa1的输入端in可以连接为接收第一启动信号gstv1,第二级移位寄存器单元goa2的输入端in可以连接为接收第二启动信号gstv2。

78.每个移动寄存器单元还可以具有时钟信号端clk。根据本公开的实施例,每级移位寄存器单元可以在各自的时钟信号端clk和输入端in的信号的控制下,在输出端out产生输出信号作为栅极驱动信号。例如,移位寄存器单元goa1产生第一栅极驱动信号g1,移位寄存器单元goa2产生第二栅极驱动信号g2,以此类推。通过级联的方式,使得后一级移位寄存器单元产生的栅极驱动信号可以相对于前一级移位寄存器单元产生的栅极驱动信号而移位。

79.根据本公开的实施例,栅极驱动电路接收的时钟信号可以包括第一时钟信号clk1和第二时钟信号clk2。在图6中,奇数级的移位寄存器单元的clk端连接为接收第一时钟信

号clk1,偶数级的移位寄存器单元的时钟信号端clk连接为接收第二时钟信号clk2。

80.根据本公开的实施例,每个移位寄存器单元还可以连接为接收电源信号vgh和参考信号vgl。

81.根据本公开的实施例,显示控制器提供给显示面板的栅极驱动电路的驱动控制信号可以包括上述启动信号gstv1、gstv2、时钟信号clk1、clk2中的至少之一。

82.以上虽然以k=2,i=2为例进行了描述,然而本公开的实施例不限于此。根据本公开的实施例,i的数值可以根据k的数值确定,k的数值可以根据需求进行配置,在此不作限定。

83.以上仅仅是本公开实施例的显示设备的示例说明,本公开实施例的显示设备的结构不限于此,可以根据需要而具有其他结构。例如,显示设备可以是基于有机发光二极管显示技术的显示设备。显示设备的栅极驱动电路可以采用不同于图6所示的级联方式。

84.图7示意性示出了根据本公开实施例的显示设备的信号时序图。下面以在n=1080,k=2的情况下,以图5的显示设备为例来说明图7的信号时序。

85.在第一时段,栅极驱动电路202可以产生以预设的时间间隔顺次移位的栅极驱动信号g1、g3、g5

……

g1079,从而依次开启第一行子像素、第三行子像素、第五行子像素

……

第1079行子像素。

86.在第二时段,栅极驱动电路202可以产生以预设的时间间隔顺次移位的栅极驱动信号g2、g4、g6

……

g1080,从而依次开启第二行子像素、第四行子像素

……

第1080行子像素。

87.图8示意性示出了根据本公开实施例的显示控制器的控制方法的流程图。

88.如图8所示,该方法包括操作s810~s830。

89.操作s810,渲染电路接收显示数据并对接收到的显示数据执行渲染,显示数据的刷新率是显示面板的刷新率的k倍,k为大于1的整数。

90.操作s820,补偿电路基于存储器中的补偿数据对渲染电路渲染后的显示数据执行补偿,得到补偿后的显示数据。

91.操作s830,驱动电路基于补偿电路提供的补偿后的显示数据来产生驱动控制信号,驱动控制信号用于在k个时段中的每个使得驱动显示面板包含的n行子像素中的n/k行子像素,n为大于1的整数,且n/k为大于或等于1的整数。

92.根据本公开的实施例,k=2,驱动电路在第一时段驱动显示面板中的奇数行子像素,在第二时段驱动显示面板中的偶数行子像素。

93.本领域的技术人员可以理解,上面所描述的实施例都是示例性的,并且本领域的技术人员可以对其进行改进,各种实施例中所描述的结构在不发生结构或者原理方面的冲突的情况下可以进行自由组合。

94.在详细说明本公开的较佳实施例之后,熟悉本领域的技术人员可清楚的了解,在不脱离随附权利要求的保护范围与精神下可进行各种变化与改变,且本公开亦不受限于说明书中所举示例性实施例的实施方式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1