发光显示设备的制作方法

发光显示设备

1.本技术是申请号为201811406378.6、申请日为2018年11月23日、发明名称为“发光显示设备及其驱动方法”的发明专利申请的分案申请。

技术领域

2.本发明涉及一种发光显示设备及其驱动方法。

背景技术:

3.在显示设备的领域中,正广泛使用重量轻且功耗低的液晶显示(lcd)设备,但其需要诸如背光之类的单独的光源。相比之下,发光显示设备可通过自发光器件显示图像。与lcd设备相比,发光显示设备具有快速响应时间、低功耗和优良的视角,因而作为下一代显示设备引起了很多关注。

4.一般的发光显示设备包括针对每个像素形成的像素电路。像素电路通过根据数据电压切换驱动晶体管以控制从驱动电源流到发光器件的电流的幅度,由此使发光器件发光来显示预定图像。

5.在一般的发光显示设备中,由于工艺变化导致的驱动晶体管的阈值电压的变化,流过每个像素的发光器件的电流可发生变化。因此,因为即使施加相同的数据电压,从驱动晶体管输出的数据电流对于每个像素来说也是不同的,所以一般的发光显示设备的像素电路可包括用于补偿驱动晶体管的阈值电压的内部补偿电路。难以获得均匀的图像质量。

6.在相关技术中,具有内部补偿电路的像素电路在采样时段期间采样驱动晶体管的阈值电压,将采样电压存储在电容器中,并且使用存储在电容器中的采样电压补偿驱动晶体管的阈值电压。

7.然而,在采样电压与驱动晶体管的实际阈值电压之间可能存在差异。此外,由于设置在像素中的驱动晶体管之间的阈值电压变化,存储在像素的电容器中的采样电压之间可发生采样变化。结果,由于采样电压变化导致的像素之间的电压变化,图像质量可劣化。

技术实现要素:

8.因此,本发明旨在提供一种基本上克服了由于相关技术的局限性和缺点而导致的一个或多个问题的发光显示设备及其驱动方法。

9.本发明的一个目的是提供一种发光显示设备及其驱动方法,用于防止由于设置在像素中的驱动晶体管之间的阈值电压变化导致的像素之间的电压变化而造成的图像质量劣化。

10.在下面的描述中将列出本发明的附加特征和优点,这些特征和优点的一部分通过该描述将是显而易见或者可通过本发明的实践领会到。本发明的这些目的和其他优点可通过说明书及其权利要求书以及附图中具体指出的结构来实现和获得。

11.为了实现这些和其他优点并根据本发明的意图,如在此具体化和概括描述的,发光显示设备可包括:包括多个像素的发光显示面板,所述多个像素的每一个按照初始化时

段、采样时段、偏移电压形成时段、数据写入时段和发光时段的顺序操作;数据驱动电路,所述数据驱动电路用于向每个像素提供数据电压;栅极驱动电路,所述栅极驱动电路用于向每个像素提供控制信号,所述控制信号具有针对相应像素的初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段而确定的电压电平;和时序控制器,所述时序控制器用于控制所述数据驱动电路和所述栅极驱动电路,其中所述偏移电压形成时段比所述采样时段长。

12.在另一个方面中,提供一种驱动发光显示设备的方法,所述发光显示设备包括多个像素,所述多个像素的每一个具有发光器件和连接至所述发光器件的像素电路,所述方法可包括:按照初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段的顺序操作每个像素,其中所述偏移电压形成时段比所述采样时段长。

13.在又一个方面中,发光显示设备可包括:多个像素的发光显示面板,所述多个像素的每一个按照初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段的顺序操作;数据驱动电路,所述数据驱动电路用于向每个像素提供数据电压;栅极驱动电路,所述栅极驱动电路用于向每个像素提供控制信号,所述控制信号具有针对相应像素的初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段而确定的电压电平;和时序控制器,所述时序控制器用于控制所述数据驱动电路和所述栅极驱动电路,其中每个像素包括发光器件和连接至所述发光器件的像素电路,其中每个像素电路包括:驱动晶体管,所述驱动晶体管具有连接至第一像素节点的栅极电极、连接至第二像素节点的源极电极、以及连接至第三像素节点的漏极电极;开关电路,所述开关电路用于向所述第一像素节点提供基准电压或所述数据电压;初始化晶体管,所述初始化晶体管用于向所述第二像素节点提供初始化电压;发光控制晶体管,所述发光控制晶体管用于向所述第三像素节点提供像素驱动电压,其中所述发光控制晶体管在所述初始化时段和所述数据写入时段期间截止并且在所述采样时段、所述偏移电压形成时段和所述发光时段期间导通;和存储电容器,所述存储电容器连接在所述第一像素节点与所述第二像素节点之间。

14.在又一个方面中,发光显示设备可包括:包括多个像素的发光显示面板,所述多个像素的每一个按照初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段的顺序操作;数据驱动电路,所述数据驱动电路用于向每个像素提供数据电压;栅极驱动电路,所述栅极驱动电路用于向每个像素提供控制信号,所述控制信号具有针对相应像素的初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段而确定的电压电平;和时序控制器,所述时序控制器用于控制所述数据驱动电路和所述栅极驱动电路,其中每个像素包括发光器件和连接至所述发光器件的像素电路,其中每个像素电路包括:驱动晶体管,所述驱动晶体管具有连接至第一像素节点的栅极电极、连接至第二像素节点的源极电极、以及连接至第三像素节点的漏极电极;和存储电容器,所述存储电容器连接在所述第一像素节点与所述第二像素节点之间,其中在所述采样时段中:所述第一像素节点接收基准电压,所述第二像素节点电性浮置,所述第三像素节点接收像素驱动电压,其中在所述偏移电压形成时段中:所述第一像素节点和所述第二像素节点的每一个电性浮置,所述第三像素节点接收所述像素驱动电压,其中在所述数据写入时段中:所述第二像素节点和所述第三像素节点的每一个电性浮置,所述第一像素节点接收所述数据电压。

15.应当理解,本发明前面的概括描述和下面的详细描述都是例示性的和解释性的,

意在对要求保护的本发明提供进一步的解释。

附图说明

16.被包括用来给本发明提供进一步理解并且并入本技术中组成本技术一部分的附图图解了本发明的示例性实施方式,并与说明书一起用于解释本发明的原理。在附图中:

17.图1是显示根据本发明示例性实施方式的发光显示设备的示意图;

18.图2是显示图1中所示的示例性像素的示图;

19.图3是图解图2中所示的像素的操作的操作时序图;

20.图4是显示图1中所示的另一示例性像素的示图;

21.图5是图解图4中所示的像素的操作的操作时序图;

22.图6a和6b是图解在根据本发明示例性实施方式的发光显示设备中,具有不同阈值电压的两个驱动晶体管的采样时段和偏移电压形成时段的特性的示图;

23.图7是显示在根据本发明示例性实施方式的发光显示设备中,布置在同一水平行中并且包括具有不同阈值电压的驱动晶体管的三个像素的模拟操作结果的波形图。

具体实施方式

24.现在将详细参考本发明的示例性实施方式,附图中图解了这些实施方式的一些例子。

25.在不背离本发明的精神或范围的情况下,可在本发明的发光显示设备及其驱动方法中进行各种修改和变化,这对于所属领域技术人员来说是显而易见的。因而,本发明旨在覆盖落入所附权利要求书范围及其等同范围内的对本发明的修改和变化。

26.为了描述本发明的示例性实施方式而在附图中公开的形状、大小、比例、角度和数量仅仅是示例,因而本发明不限于图解的细节。相似的附图标记通篇指代相似的要素。在下面的描述中,当确定对相关已知技术的详细描述会不必要地使本发明的重点模糊不清时,将省略该详细描述。

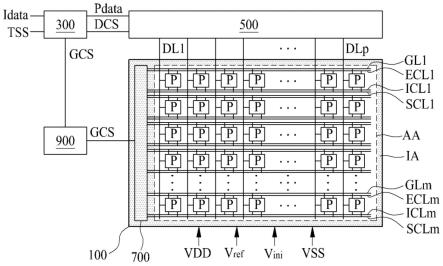

27.在本技术中使用“包括”、“具有”和“包含”的情况下,可添加其他部分,除非使用了“仅”。

28.在解释一要素时,尽管没有明确说明,但该要素应解释为包含误差范围。

29.在描述位置关系时,例如,当两部分之间的位置关系被描述为“在

……

上”、“在

……

上方”、“在

……

下方”和“在

……

之后”时,可在这两部分之间设置一个或多个其他部分,除非使用了“正好”或“直接”。

30.在描述时间关系时,例如,当时间顺序被描述为“在

……

之后”、“随后”、“接下来”和“在

……

之前”时,可包括不连续的情况,除非使用了“正好”或“直接”。

31.将理解到,尽管在此可使用术语“第一”、“第二”等来描述各种要素,但这些要素不应被这些术语限制。这些术语仅仅是用来将一要素与另一要素区分开。例如,在不背离本发明的范围的情况下,第一要素可能被称为第二要素,类似地,第二要素可能被称为第一要素。

32.术语“至少一个”应当理解为包括相关所列项目中的一个或多个的任意组合和所有组合。例如,“第一项目、第二项目和第三项目中的至少一个”表示选自第一项目、第二项

目和第三项目中的两个或更多个项目的所有项目组合以及第一项目、第二项目或第三项目。

33.所属领域技术人员能够充分理解到,本发明各示例性实施方式的特征可彼此部分或整体地结合或组合,且可在技术上彼此进行各种互操作和驱动。本发明的示例性实施方式可彼此独立实施,或者以相互依赖的关系共同实施。

34.下文中,将参照附图详细描述根据本发明示例性实施方式的发光显示设备及其驱动方法。在给每幅图的要素添加参考标记时,尽管显示在不同图中,但相似的参考标记可指代相似的要素。在下面的描述中,当确定对相关已知功能或构造的详细描述会不必要地使本发明的重点模糊不清时,将省略该详细描述。

35.图1是显示根据本发明示例性实施方式的发光显示设备的示意图。

36.参照图1,根据本发明示例性实施方式的发光显示设备包括发光显示面板100、时序控制单元300、数据驱动电路500和栅极驱动电路(或栅极驱动器)700。

37.发光显示面板100可包括限定在基板上的显示区域aa(例如,有源区域)和围绕显示区域aa的非显示区域ia(例如,无源区域)。

38.显示区域aa可包括多个像素p,多个像素p分别设置在由第一到第m(其中m是等于或大于2的自然数)栅极线gl1到glm、第一到第m发光控制线ecl1到eclm、以及多条数据线dl1到dlp(其中p是等于或大于2的自然数)限定的多个像素区域中。此外,显示区域aa可进一步包括第一到第m初始化控制线icl1到iclm和第一到第m采样控制线scl1到sclm。此外,显示区域aa可进一步包括被提供有像素驱动电压vdd的多条像素驱动电压线、被提供有初始化电压vini的多条初始化电压线、被提供有基准电压vref的多条基准电压线、以及被提供有阴极电压vss的阴极电极层cel(见图2)。

39.根据示例性实施方式的像素p可设置成条结构。在这种情形中,每个像素p可包括红色子像素、绿色子像素和蓝色子像素,并且可进一步包括白色子像素。

40.然而,示例性实施方式不限于此,根据另一示例性实施方式,多个像素p可在显示区域aa中布置成pentile结构。在这种情形中,多个像素p的每一个可包括一维地布置成多边型的一个红色子像素、两个绿色子像素和一个蓝色子像素。例如,具有pentile结构的每个像素p可包括一维地布置成八边型的一个红色子像素、两个绿色子像素和一个蓝色子像素。在这种情形中,蓝色子像素可具有最大尺寸,两个绿色子像素的每一个可具有最小尺寸。

41.布置在栅极线gl的长度方向上的多个像素p的每一个可连接至穿过相应像素区域的栅极线gl、发光控制线ecl、初始化控制线icl、采样控制线scl、数据线dl、像素驱动电压线、初始化电压线、基准电压线、阴极电极层cel。一条像素驱动电压线、一条初始化电压线和一条基准电压线可连接至一个子像素或一个单位像素。

42.多个像素p按照初始化时段、采样时段、偏移(offset)电压形成时段、数据写入时段和发光时段的(例如,信号)顺序进行操作,并且通过与提供至数据线dl的数据电压对应的数据电流发光。在此,偏移电压形成时段可设置为比采样时段长。根据一示例性实施方式,采样时段可设置为小于或等于1.5个水平周期。作为一示例,水平周期可指用于驱动一个水平行(例如,栅极线)的像素的时间。此外,根据一示例性实施方式,偏移电压形成时段可设为采样时段的二到六倍长。

43.非显示区域ia可沿基板的边缘设置,以围绕显示区域aa。非显示区域ia的一个部分可设置在基板上并且可包括与数据线dl1到dlp连接的焊盘部。

44.时序控制器300可将输入的视频数据idata排列为适合于驱动发光显示面板100的基于像素的数字数据pdata,时序控制器300可从时序同步信号tss产生数据控制信号dcs,以将数据控制信号dcs提供至数据驱动电路500。

45.时序控制器300可基于时序同步信号tss产生栅极控制信号gcs并且可将栅极控制信号gcs提供至栅极驱动电路700,栅极控制信号gcs包括栅极起始信号、多个栅极时钟、多个进位时钟、多个采样时钟和多个初始化时钟。栅极控制信号gcs可经由焊盘部提供至栅极驱动电路700。

46.数据驱动电路500可连接至设置在发光显示面板100中的数据线dl1到dlp。数据驱动电路500可基于从时序控制器300提供的数据控制信号dcs,通过使用多个基准伽马电压将基于像素的数字数据pdata转换为基于像素的模拟数据电压。数据驱动电路500可将基于像素的模拟数据电压提供至相应的数据线dl。

47.栅极驱动电路700连接至设置在显示区域aa中的第一到第m栅极线gl1到glm、第一到第m发光控制线ecl1到eclm、第一到第m初始化控制线icl1到iclm、以及第一到第m采样控制线scl1到sclm。栅极驱动电路700可基于栅极控制信号gcs,给每个像素p提供具有针对每个像素p的初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段确定的电压电平的控制信号。控制信号可包括初始化控制信号、采样控制信号、扫描控制信号和发光控制信号。

48.根据一示例性实施方式,栅极驱动电路700产生具有相同周期和周期性移位的相位的扫描控制信号,并且将扫描控制信号按顺序提供至多条栅极线gl1到glm。栅极驱动电路700还产生具有相同周期和周期性移位的相位的初始化控制信号,并且将初始化控制信号按顺序提供至多条初始化控制线icl1到iclm。栅极驱动电路700附加地产生具有相同周期和周期性移位的相位的采样控制信号,并且将采样控制信号按顺序提供至多条采样控制线scl1到sclm。栅极驱动电路700还产生具有相同周期和周期性移位的相位的进位信号。栅极驱动电路700基于至少两个不同的进位信号附加地产生发光控制信号,并且将发光控制信号提供至第一到第m发光控制线ecl1到eclm,发光控制信号包括具有不同相位差的第一栅极截止电压电平(gate-off voltage level)和第二栅极截止电压电平。

49.栅极驱动电路700可随制造像素p的薄膜晶体管的工艺一起形成在基板的非显示区域的左部和/或右部中。例如,栅极驱动电路700可形成在基板的非显示区域的左部中并且可利用单馈送方案(single feeding scheme)进行操作来给多条栅极线gl提供扫描控制信号。作为另一示例,栅极驱动电路700可形成在基板的非显示区域的左部和右部中并且可以以双馈送方案(double feeding scheme)进行操作来给多条栅极线gl提供扫描控制信号。作为再一示例,栅极驱动电路700可形成在基板的非显示区域的左部和右部中并且可以以双馈送交错方案(double feeding interlacing scheme)进行操作来给多条栅极线gl提供扫描控制信号。

50.根据本发明示例性实施方式的发光显示设备可进一步包括对栅极控制信号gcs进行电平移位的电平移位器单元900。

51.电平移位器单元900可基于从栅极导通电压源提供的栅极导通电压和从栅极截止

电压源提供的栅极截止电压,将栅极控制信号gcs的高逻辑电压电平移位为栅极导通电压电平。电平移位器单元900还可将栅极控制信号gcs的低逻辑电压电平移位为栅极截止电压电平。电平移位器单元900可将电平移位后的高逻辑电压和低逻辑电压提供至栅极驱动电路700。在一示例中,电平移位器单元900可内置在例如时序控制单元300中,以成为该时序控制单元300的电路的一部分。

52.图2是显示图1中所示的示例性像素的示图,其显示了发光显示面板100的与任意栅极线和任意数据线连接的一个像素(或一个子像素)。

53.参照图1和2,根据本发明一示例性实施方式,像素p可包括像素电路pc和发光器件eld。

54.发光器件eld可夹在连接至像素电路pc的第一电极(例如,阳极电极)与连接至阴极电极层cel的第二电极(例如,阴极电极)之间。根据一示例性实施方式,发光器件eld可包括有机发光单元、量子点发光单元或无机发光单元,或者可包括微型发光二极管器件。发光器件eld通过从像素电路pc提供的数据电流发光。

55.像素电路pc可连接至栅极线gl、发光控制线ecl、初始化控制线icl、采样控制线scl、数据线dl、像素驱动电压线pl、初始化电压线il和基准电压线rl,并且可给发光器件eld提供与提供至数据线dl的数据电压vdata对应的数据电流。

56.像素电路pc可包括驱动晶体管tdr、初始化晶体管tini、发光控制晶体管tem、开关电路sc(或开关单元)和存储电容器cst。

57.驱动晶体管tdr可连接在像素驱动电压线pl与发光器件eld之间,并且可根据存储电容器cst的电压进行切换,以控制从像素驱动电压线pl流到发光器件eld的电流。根据一示例性实施方式,驱动晶体管tdr可包括电连接至第一像素节点q的栅极电极、电连接至第二像素节点a的源极电极、以及电连接至第三像素节点b的漏极电极。

58.初始化晶体管tini可响应于初始化控制信号ics将从初始化电压线il提供的初始化电压vini提供至与驱动晶体管tdr的源极电极连接的第二像素节点a。就是说,初始化晶体管tini可通过在初始化时段期间提供的栅极导通电压电平的初始化控制信号导通,以将初始化电压vini提供至第二像素节点a。根据一示例性实施方式,初始化晶体管tini可包括电连接至相邻初始化控制线icl的栅极电极、电连接至初始化电压线的第一源极/漏极电极、以及连接至第二像素节点a的第二源极/漏极电极。初始化晶体管tini可根据初始化控制信号ics仅在初始化时段期间导通。

59.发光控制晶体管tem可响应于发光控制信号ecs将从像素驱动电压线pl提供的像素驱动电压vdd提供至与驱动晶体管tdr的漏极电极连接的第三像素节点b。就是说,发光控制晶体管tem可通过在初始化时段和数据写入时段期间提供的栅极截止电压电平的发光控制信号ecs截止,以阻挡提供至第三像素节点b的像素驱动电压vdd,并且可通过在采样时段、偏移电压形成时段和发光时段期间提供的栅极导通电压电平的发光控制信号ecs导通,以将像素驱动电压提供至第三像素节点b。

60.根据一示例性实施方式,发光控制晶体管tem可包括电连接至相邻发光控制线ecl的栅极电极、电连接至像素驱动电压线pl的第一源极/漏极电极、以及电连接至第三像素节点b的第二源极/漏极电极。根据发光控制信号ecs,发光控制晶体管tem可在初始化时段和数据写入时段期间截止并且可在采样时段、偏移电压形成时段和发光时段期间导通。

61.开关电路sc可将基准电压vref或数据电压vdata提供至第一像素节点q。就是说,开关电路sc可在初始化时段和采样时段期间将基准电压vref提供至第一像素节点q,并且可在数据写入时段期间将数据电压vdata提供至第一像素节点q。根据一示例性实施方式,开关电路sc可包括将数据电压vdata提供至第一像素节点q的第一开关晶体管tsw1和将基准电压vref提供至第一像素节点q的第二开关晶体管tsw2。

62.第一开关晶体管tsw1可响应于扫描控制信号ss将从数据线dl提供的实际数据电压vdata提供至第一像素节点q。就是说,第一开关晶体管tsw1可通过在数据写入时段期间提供的栅极导通电压电平的扫描控制信号ss导通,以将实际数据电压vdata提供至第一像素节点q。根据一示例性实施方式,第一开关晶体管tsw1可包括电连接至相邻栅极线gl的栅极电极、电连接至相邻数据线dl的第一源极/漏极电极、以及电连接至第一像素节点q的第二源极/漏极电极。第一开关晶体管tsw1可根据扫描控制信号ss仅在数据写入时段期间导通。

63.第二开关晶体管tsw2可响应于采样控制信号scs将从基准电压线rl提供的基准电压vref提供至第一像素节点q。就是说,第二开关晶体管tsw2可通过在初始化时段和采样时段期间提供的栅极导通电压电平的采样控制信号scs导通,以将基准电压vref提供至第一像素节点q。根据一示例性实施方式,第二开关晶体管tsw2可包括电连接至相邻采样控制线scl的栅极电极、电连接至第一像素节点q的第一源极/漏极电极、以及电连接至基准电压线rl的第二源极/漏极电极。第二开关晶体管tsw2可根据采样控制信号scs仅在初始化时段和采样时段期间导通。

64.对于驱动晶体管tdr、第一开关晶体管tsw1、第二开关晶体管tsw2、初始化晶体管tini和发光控制晶体管tem来说,第一源极/漏极电极和第二源极/漏极电极可根据电流的方向定义为源极电极或漏极电极。

65.驱动晶体管tdr、第一开关晶体管tsw1、第二开关晶体管tsw2、初始化晶体管tini和发光控制晶体管tem的每一个具有包含诸如氧化锌(zno)、氧化铟锌(inzno)或氧化铟镓锌(ingazno4)之类的氧化物半导体材料的半导体层。然而,示例性实施方式不限于此,半导体层可包含氧化物半导体材料以外的单晶硅、多晶硅或有机材料。

66.驱动晶体管tdr、第一开关晶体管tsw1、第二开关晶体管tsw2、初始化晶体管tini和发光控制晶体管tem的每一个可以是n型薄膜晶体管。然而,示例性实施方式不限于此,驱动晶体管tdr、第一开关晶体管tsw1、第二开关晶体管tsw2、初始化晶体管tini和发光控制晶体管tem的每一个可以是p型薄膜晶体管。

67.存储电容器cst连接在第一像素节点q与第二像素节点a之间。就是说,存储电容器cst连接在驱动晶体管tdr的栅极电极与源极电极之间。存储电容器cst存储第一像素节点q的电压与第二像素节点a的电压之间的、根据像素p的操作时序而变化的差电压,存储数据电压减去基准电压vref和数据偏移电压voffset(vdata-vref-voffset),并且利用存储的电压使驱动晶体管tdr进行切换。存储电容器cst设置在第一像素节点q与第二像素节点a之间的交叠区域中。存储电容器cst可包括电连接至第一像素节点q的第一电容器电极、与第一电容器电极交叠且电连接至第二像素节点a的第二电容器电极、以及设置在第一电容器电极与第二电容器电极之间的电容层。在此,驱动晶体管tdr的特征电压可包括阈值电压。

68.图3是图解图2中所示的像素的操作的操作时序图。

69.参照图1到3,根据本发明示例性实施方式的像素p可按照初始化时段ip、采样时段(或补偿时段)sp、偏移电压形成时段ovfp、数据写入时段(或数据编程时段)dwp和发光时段ep的顺序进行操作。

70.在初始化时段ip中,首先,存储电容器cst可被提供至初始化电压线il的初始化电压vini初始化。此外,在初始化时段ip中,响应于第一栅极截止电压电平voff的发光控制信号ecs、以及栅极导通电压电平von的初始化控制信号ics和采样控制信号scs,基准电压vref提供至基准电压线rl。就是说,在初始化时段ip中,发光控制晶体管tem可通过第一栅极截止电压电平voff的发光控制信号ecs截止(即,off1),并且初始化晶体管tini可通过栅极导通电压电平von的初始化控制信号ics导通,以将初始化电压vini提供至第二像素节点a。随后,第二开关晶体管tsw2可通过栅极导通电压电平von的采样控制信号scs导通,以将基准电压vref提供至第一像素节点q,并且第一开关晶体管tsw1可通过栅极截止电压电平voff的扫描控制信号ss保持截止状态。因而,存储电容器cst可利用与初始化电压vini和基准电压vref之间的差电压对应的初始化电压被初始化。

71.在采样时段sp中,通过响应于栅极导通电压电平von的采样控制信号scs和栅极导通电压电平von的发光控制信号ecs提供至像素驱动电压线pl的像素驱动电压vdd和提供至基准电压线rl的基准电压vref,与驱动晶体管tdr的阈值电压对应的采样电压可存储在存储电容器cst中。此外,在采样时段sp中,发光控制晶体管tem可通过栅极导通电压电平von的发光控制信号ecs导通(即,on),初始化晶体管tini可通过栅极截止电压电平voff的初始化控制信号ics截止,第二开关晶体管tsw2可通过栅极导通电压电平von的采样控制信号scs保持导通状态,并且第一开关晶体管tsw1可通过栅极截止电压电平voff的扫描控制信号ss保持截止状态。因而,基准电压vref可通过第二开关晶体管tsw2提供至第一像素节点q,并且第二像素节点a可根据初始化晶体管tini截止而电性浮置。因此,驱动晶体管tdr可通过第一像素节点q的基准电压vref导通,以作为源极跟随器(source follower)进行操作,并且当源极电压为通过从基准电压vref减去驱动晶体管tdr的阈值电压v

th

而获得的电压“vref-v

th”时,驱动晶体管tdr可截止,因而与驱动晶体管tdr的阈值电压对应的采样电压(或补偿电压)可充到存储电容器cst中。例如,接近驱动晶体管tdr的阈值电压v

th

的电压或驱动晶体管tdr的阈值电压v

th

与基准电压vref之间的差电压(vref-v

th

)可充到存储电容器cst中。在采样时段sp中,由于像素p之间的阈值电压变化δv

th

,可发生采样电压的变化δv(下文中称为采样电压变化δv)。

72.在偏移电压形成时段ovfp中,通过响应于栅极导通电压电平von的发光控制信号ecs从像素驱动电压线pl提供至第三像素节点b的像素驱动电压vdd和存储在存储电容器cst中的采样电压,可在第一像素节点q处形成与流过驱动晶体管tdr的电流对应的数据偏移电压。此外,在偏移电压形成时段ovfp中,发光控制晶体管tem可通过栅极导通电压电平von的发光控制信号ecs保持导通状态(即,on),初始化晶体管tini可通过栅极截止电压电平voff的初始化控制信号ics保持截止状态,第二开关晶体管tsw2可通过栅极截止电压电平voff的采样控制信号scs截止,并且第一开关晶体管tsw1可通过栅极截止电压电平voff的扫描控制信号ss保持截止状态。因而,由于基准电压vref的供给可被阻挡,所以第一像素节点q可成为电性高阻抗(或浮置)状态。此外,第二像素节点a的电压可根据流过通过存储在存储电容器cst中的采样电压而导通的驱动晶体管tdr的采样电流而变化。此外,由于第

二像素节点a的电位变化,可处于高阻抗状态的第一像素节点q的电压可根据存储电容器cst的电压耦合(或自举)而变为(或移位为)包括数据偏移电压voffset的电压。作为一示例,在偏移电压形成时段ovfp中,第一像素节点q的最终电压可高于采样时段sp的最终电压,例如,第一像素节点q的最终电压可以是通过将基准电压vref和数据偏移电压voffset相加而获得的电压(vref+voffset)。在偏移电压形成时段ovfp中,第二像素节点a的电压可根据采样电压变化δv而变化。

73.在数据写入时段dwp中,响应于栅极导通电压电平von的扫描控制信号ss和第二栅极截止电压电平voff的发光控制信号ecs,从数据线dl提供的数据电压vdata可提供至第一像素节点q。

74.在数据写入时段dwp中,第一开关晶体管tsw1可通过栅极导通电压电平von的扫描控制信号ss导通,发光控制晶体管tem可通过第二栅极截止电压电平voff的发光控制信号ecs截止(即,off2),第二开关晶体管tsw2可通过栅极截止电压电平voff的采样控制信号scs保持截止状态,并且初始化晶体管tini可通过栅极截止电压电平voff的初始化控制信号ics保持截止状态。此外,实际数据电压vdata可从数据驱动电路提供至数据线dl。因而,实际数据电压vdata可通过第一开关晶体管tsw1提供至第一像素节点q,并且第二像素节点a可根据初始化晶体管tini截止而保持电性浮置状态。因此,第一像素节点q的电压可从通过将基准电压vref和数据偏移电压voffset相加而获得的电压(vref+voffset)移位至实际数据电压vdata,第一像素节点q可移位为通过从实际数据电压vdata减去基准电压vref和数据偏移电压voffset而获得的电压(vdata-vref-voffset),如下面表达式1中所示。就是说,可通过使发光控制晶体管tem截止来阻挡已提供至驱动晶体管tdr的像素驱动电压vdd,因而没有电流流过驱动晶体管tdr。当在驱动晶体管tdr中没有电流流动的状态下给第一像素节点q施加实际数据电压vdata时,由于第一像素节点q的电压变化,与通过从实际数据电压vdata减去基准电压vref和数据偏移电压voffset而获得的数据电压(vdata-vref-voffset)成比例的电压通过耦合被附加地添加至存储电容器cst。因而,可通过存储电容器cst的电压变化(或第一像素节点q与第二像素节点a之间的电压变化)去除像素p之间的采样电压变化δv。在这种情形中,附加地添加至存储电容器cst的电压可表示为可与第一像素节点q的电压变化相耦合的电压,比如表达式α(vdata-vref-voffset)。在此α(阿尔法)是指传输率(transfer rate)。

75.δvq=v

data-(v

ref

+v

offset

)

ꢀꢀꢀ

(1)

76.在发光时段ep中,发光器件eld可响应于栅极导通电压电平von的发光控制信号ecs通过存储电容器cst的电压和像素驱动电压vdd发光。

77.在发光时段ep中,发光控制晶体管tem可通过栅极导通电压电平von的发光控制信号ecs导通(即,on),第一开关晶体管tsw1可通过栅极截止电压电平voff的扫描控制信号ss截止,并且第二开关晶体管tsw2和初始化晶体管tini可通过栅极截止电压电平voff的相应控制信号scs和ics保持截止状态。因而,存储在存储电容器cst中的电压可提供至第一像素节点q,并且像素驱动电压vdd可通过发光控制晶体管tem提供至驱动晶体管tdr的漏极电极。因此,通过使电流能够流过驱动晶体管tdr,源极电压(例如,第二像素节点的电压)可增加,存储电容器cst的电压可被保持,并且驱动晶体管tdr的栅极电压(例如,第一像素节点的电压)可与第二像素节点的电压增加相耦合地增加。因而,可通过存储电容器cst的电压

变化(或第一像素节点q与第二像素节点a之间的电压变化)消除像素p之间的阈值电压变化。结果,流过驱动晶体管tdr的源极电流(提供至发光器件的数据电流)仅取决于实际数据电压和基准电压,而不受驱动晶体管tdr的阈值电压影响。

78.如上所述,根据本发明示例性实施方式的发光显示设备可通过采样时段与数据写入时段之间的每个像素的偏移电压形成时段,在驱动晶体管的栅极电极处形成数据偏移电压。因此,可补偿像素之间的采样电压变化以及设置于像素中的驱动晶体管之间的阈值电压变化,因而可减小由设置于像素中的驱动晶体管之间的阈值电压变化导致的像素之间的采样电压变化。

79.图4是显示图1中所示的另一示例性像素的示图,其中图2中所示的像素电路pc的开关电路sc发生变化。因而,下面将仅描述开关电路及其相关元件,将省略对其余元件的重复描述。

80.图5是图解图4中所示的像素的操作的操作时序图。

81.参照图1、4和5,根据本示例性实施方式的像素p中设置的像素电路pc的开关电路sc可在初始化时段和采样时段期间导通,以将基准电压vref提供至第一像素节点q,并且可在数据写入时段期间导通,以将数据电压vdata提供至第一像素节点q。根据一示例性实施方式,开关电路sc可包括开关晶体管tsw。

82.响应于扫描控制信号ss,开关晶体管tsw可将从数据线dl提供的基准电压vref提供至第一像素节点q,然后可将从数据线dl提供的实际数据电压vdata提供至第一像素节点q。就是说,开关晶体管tsw可通过在初始化时段和采样时段期间提供的第一栅极导通电压电平的扫描控制信号ss导通(即,on1),以将基准电压vref提供至第一像素节点q,然后可通过在数据写入时段期间提供的第二栅极导通电压电平的扫描控制信号ss导通(即,on2),以将实际数据电压vdata提供至第一像素节点q。根据一示例性实施方式,开关晶体管tsw可包括电连接至相邻栅极线gl的栅极电极、电连接至相邻数据线dl的第一源极/漏极电极、以及电连接至第一像素节点q的第二源极/漏极电极。开关晶体管tsw可根据扫描控制信号ss仅在初始化时段、采样时段和数据写入时段期间导通。

83.包括开关电路sc的发光显示设备可根据扫描控制信号ss使开关晶体管tsw进行切换并且可根据开关晶体管tsw的切换将从数据线dl按顺序提供的基准电压vref和实际数据电压vdata按顺序提供至第一像素节点q。因而,通过省略设置于图1中所示的发光显示面板100中的多条采样控制线scl1到sclm和多条基准电压线rl1到rlm,并且还省略栅极驱动电路700中的用于给多条采样控制线scl1到sclm提供采样控制信号的电路,可减小栅极驱动电路700的尺寸和形成在发光显示面板100中的控制线和电压线的数量。

84.图1中所示的数据驱动电路500可以以一个(1个)水平周期或1.5个水平周期为单位给数据线dl交替提供基准电压vref和实际数据电压vdata。

85.此外,栅极驱动电路700可基于栅极控制信号gcs,给每个像素p提供具有针对每个像素p的初始化时段、采样时段、偏移电压形成时段、数据写入时段和发光时段确定的电压电平的初始化控制信号、扫描控制信号和发光控制信号。

86.栅极驱动电路700可产生具有相同周期和周期性移位的相位的扫描控制信号,并且可将扫描控制信号按顺序提供至多条栅极线gl1到glm。栅极驱动电路700还可产生具有相同周期和周期性移位的相位的初始化控制信号,并且可将初始化控制信号按顺序提供至

多条初始化控制线icl1到iclm。栅极驱动电路700可附加地产生具有相同周期和周期性移位的相位的进位信号。栅极驱动电路700可还基于至少两个不同的进位信号产生包括具有不同相位差的第一栅极截止电压电平和第二栅极截止电压电平的发光控制信号。栅极驱动电路700可附加地将发光控制信号提供至第一到第m发光控制线ecl1到eclm。

87.参照图1、4和5,根据本发明示例性实施方式的像素p可按照初始化时段ip、采样时段(或补偿时段)sp、偏移电压形成时段ovfp、数据写入时段(或数据编程时段)dwp和发光时段ep的顺序进行操作。

88.在初始化时段ip中,首先,存储电容器cst可被响应于栅极导通电压电平von的初始化控制信号ics、第一栅极导通电压电平von的扫描控制信号ss和第一栅极截止电压电平voff的发光控制信号ecs提供至初始化电压线il的初始化电压vini和提供至数据线dl的基准电压vref初始化。就是说,在初始化时段ip中,发光控制晶体管tem可通过第一栅极截止电压电平voff的发光控制信号ecs截止(即,off1),并且初始化晶体管tini可通过栅极导通电压电平von的初始化控制信号ics导通,以将初始化电压vini提供至第二像素节点a。随后,开关晶体管tsw可通过第一栅极导通电压电平von的扫描控制信号ss导通(即,on1),以将基准电压vref提供至第一像素节点q。因而,存储电容器cst可利用与初始化电压vini和基准电压vref之间的差电压对应的初始化电压被初始化。

89.在采样时段sp中,通过响应于第一栅极导通电压电平von的扫描控制信号ss和栅极导通电压电平von的发光控制信号ecs提供至像素驱动电压线pl的像素驱动电压vdd和提供至数据线dl的基准电压vref,与驱动晶体管tdr的阈值电压对应的采样电压可存储在存储电容器cst中。

90.在采样时段sp中,发光控制晶体管tem可通过栅极导通电压电平von的发光控制信号ecs导通,初始化晶体管tini可通过栅极截止电压电平voff的初始化控制信号ics截止,并且开关晶体管tsw可通过栅极导通电压电平von的扫描控制信号ss导通。因而,基准电压vref可通过开关晶体管tsw提供至第一像素节点q,并且第二像素节点a可根据初始化晶体管tini截止而电性浮置。因此,驱动晶体管tdr可通过第一像素节点q的基准电压vref导通,以作为源极跟随器进行操作,并且当源极电压为通过从基准电压vref减去驱动晶体管tdr的阈值电压v

th

而获得的电压“vref-v

th”时,驱动晶体管tdr可截止,因而与驱动晶体管tdr的阈值电压对应的采样电压(或补偿电压)可充到存储电容器cst中。例如,接近驱动晶体管tdr的阈值电压v

th

的电压或驱动晶体管tdr的阈值电压v

th

与基准电压vref之间的差电压(vref-v

th

)可充到存储电容器cst中。在采样时段sp中,由于像素p之间的阈值电压变化δv

th

,可发生采样电压的变化δv(下文中称为采样电压变化δv)。

91.在偏移电压形成时段ovfp中,通过响应于栅极导通电压电平von的发光控制信号ecs从像素驱动电压线pl提供至第三像素节点b的像素驱动电压vdd和存储在存储电容器cst中的采样电压,可在第一像素节点q处形成与流过驱动晶体管tdr的电流对应的数据偏移电压。

92.在偏移电压形成时段ovfp中,发光控制晶体管tem可通过栅极导通电压电平von的发光控制信号ecs保持导通状态,初始化晶体管tini可通过栅极截止电压电平voff的初始化控制信号ics保持截止状态,开关晶体管tsw可通过栅极截止电压电平voff的扫描控制信号ss保持截止状态。因而,由于基准电压vref的供给可被阻挡,所以第一像素节点q可成为

电性高阻抗(或浮置)状态。此外,第二像素节点a的电压可根据流过可通过存储在存储电容器cst中的采样电压而导通的驱动晶体管tdr的采样电流而变化。此外,由于第二像素节点a的电位变化,处于高阻抗状态的第一像素节点q的电压可根据存储电容器cst的电压耦合(或自举)而变为(或移位为)包括数据偏移电压voffset的电压。作为一示例,在偏移电压形成时段ovfp中,第一像素节点q的最终电压可高于采样时段sp的最终电压,例如,第一像素节点q的最终电压可以是通过将基准电压vref和数据偏移电压voffset相加而获得的电压(vref+voffset)。在偏移电压形成时段ovfp中,第二像素节点a的电压可根据采样电压变化δv而变化。

93.在数据写入时段dwp中,响应于栅极导通电压电平von的扫描控制信号ss和第二栅极截止电压电平voff的发光控制信号ecs,从数据线dl提供的数据电压vdata可提供至第一像素节点q。

94.在数据写入时段dwp中,开关晶体管tsw可通过第二栅极导通电压电平von的扫描控制信号ss导通(即,on2),发光控制晶体管tem可通过第二栅极截止电压电平voff的发光控制信号ecs截止(即,off2),并且初始化晶体管tini可通过栅极截止电压电平voff的初始化控制信号ics保持截止状态。此外,实际数据电压vdata可从数据驱动电路提供至数据线dl。因而,实际数据电压vdata可通过开关晶体管tsw提供至第一像素节点q,并且第二像素节点a可根据初始化晶体管tini截止而保持电性浮置。因此,第一像素节点q的电压可从通过将基准电压vref和数据偏移电压voffset相加而获得的电压(vref+voffset)移位至实际数据电压vdata,第一像素节点q可移位为通过从实际数据电压vdata减去基准电压vref和数据偏移电压voffset而获得的电压(vdata-vref-voffset),如上面等式1中所示。此变化与上述相同,因而将省略其重复描述。

95.在发光时段ep中,发光器件eld可响应于栅极导通电压电平von的发光控制信号ecs通过存储电容器cst的电压和像素驱动电压vdd发光。

96.在发光时段ep中,发光控制晶体管tem可通过栅极导通电压电平von的发光控制信号ecs导通,开关晶体管tsw可通过栅极截止电压电平voff的扫描控制信号ss截止,并且初始化晶体管tini可通过栅极截止电压电平voff的初始化控制信号ics保持截止状态。因而,存储在存储电容器cst中的电压可提供至第一像素节点q,并且像素驱动电压vdd可通过发光控制晶体管tem提供至驱动晶体管tdr的漏极电极。因此,通过使电流能够流过驱动晶体管tdr,源极电压(例如,第二像素节点的电压)可增加,存储电容器cst的电压可被保持,并且驱动晶体管tdr的栅极电压(例如,第一像素节点的电压)可与第二像素节点的电压增加相耦合地增加。因而,可通过存储电容器cst的电压变化(或第一像素节点q与第二像素节点a之间的电压变化)消除像素p之间的阈值电压变化。结果,流过驱动晶体管tdr的源极电流(提供至发光器件的数据电流)仅取决于实际数据电压和基准电压,而不受驱动晶体管tdr的阈值电压影响。

97.根据本发明示例性实施方式的发光显示设备可具有与图2中所示的像素相同的效果。

98.图6a和6b是图解在根据本发明示例性实施方式的发光显示设备中,具有不同阈值电压的两个驱动晶体管的采样时段和偏移电压形成时段的特性的示图。

99.首先,参照图6a,假设第一驱动晶体管tdr1和第二驱动晶体管tdr2具有δv

th

的阈

值电压变化。当参考第一驱动晶体管tdr1描述第二驱动晶体管tdr2的特性时,第一驱动晶体管tdr1的阈值电压v

th

可以是v

t

+c,第二驱动晶体管tdr2的阈值电压v

th

可以是v

t

+δv

th

+c。第一驱动晶体管tdr1的电流特性i1(v

gs

)和第二驱动晶体管tdr2的电流特性i2(v

gs

)可表示为下面的表达式(2):

100.i1(v

gs

)=l0g(v

gs-v

t

),

101.i2(v

gs

)=l0g(v

gs-v

t-δv

th

),

102.g(o)=1

ꢀꢀꢀ

(2)

103.其中v

t

表示采样电压,vgs表示栅极-源极电压。

104.在像素的采样时段中,第二像素节点a的电压va变化可表示为下面的表达式(3):

[0105][0106]

其中基准电压vref和采样电压v

t

可以是常数,c是存储电容器cst的电容cst和其他寄生电容cp之和(cst+cp)。在此,其他寄生电容cp可包括辅助电容器和/或发光器件的电容。

[0107]

此外,采样之后驱动晶体管tdr的电流id可以是“104c《id《106c”。

[0108]

对于第一驱动晶体管tdr1来说,当在采样时间ts期间进行积分时,可获得下面的等式(4)。此外,可使用下面的表达式(4)获得采样电压v

t

:

[0109][0110]

在采样时段之后,通过使用第一驱动晶体管tdr1的阈值电压变化δv

th

和采样电压变化δv,第二驱动晶体管tdr2的栅极-源极电压v

gs

和栅极电流i0g(δv)可表示为下面的表达式(5):

[0111]vgs

=v

t

+δv

th

+δv

[0112]

i=l0g(δv)

ꢀꢀꢀ

(5)

[0113]

因此,在等式(5)中,在像素的驱动晶体管之间存在阈值电压变化,因而可在采样时段期间发生采样电压变化δv,可在上述偏移电压形成时段期间补偿采样电压变化δv。

[0114]

参照图6b,当在偏移电压形成时段期间给驱动晶体管的漏极电极施加像素驱动电压时,可阻挡提供至第一像素节点q的基准电压vref。因而,在偏移电压形成时段tf期间驱动晶体管的栅极电极(或第一像素节点)处于高阻抗状态,驱动晶体管的源极电极(或第二像素节点)的电压通过由于像素驱动电压而流过驱动晶体管的电流进行变化,如下面的表达式(6)中所示,第二像素节点a的电压变化dva根据采样电压变化δv而变化。

[0115][0116]

由于提供至第一像素节点q的基准电压vref被阻挡,所以在没有电流流过第一像素节点q时第一像素节点q与第二像素节点a之间的电压变化δ(v

q-va)可表示为下面的表达式(7):

[0117]

[0118]

其中η是驱动晶体管的反向传输率,δva是第二像素节点a的电压变化。

[0119]

考虑到驱动晶体管的反向传输率η,第一像素节点q与第二像素节点a之间的电压变化dv

qa

可表示为下面的表达式(8):

[0120][0121]

此外,在偏移电压形成时段期间,可根据表达式(7)中的驱动晶体管的反向传输率η和表达式(6)中的第二像素节点a的电压变化形成数据偏移电压voffset,如下面的表达式(9)所示:

[0122][0123]

由于根据在偏移电压形成时段期间发生的第一像素节点q与第二像素节点a之间的电压变化dv

qa

,电流流过驱动晶体管,所以驱动晶体管的栅极-源极电压可逐渐减小并发生变化,但由于电压变化导致的电流的差异是微不足道的,因而可忽略。

[0124]

因此,通过在偏移电压形成时段期间添加第一像素节点q与第二像素节点a之间的电压变化,存储电容器cst的电压,即驱动晶体管的栅极-源极电压v

gs

可表示为下面的表达式(10):

[0125]vgs

=v

t

+δv

th

+δv+dv

qa

ꢀꢀꢀ

(10)

[0126]

在偏移电压形成时段之后的数据写入时段期间,可阻挡施加至驱动晶体管的漏极电极的像素驱动电压,并且数据电压vdata可施加至第一像素节点q。因而,第一像素节点q的电压变化δvq可表示为表达式(11),其可受在偏移电压形成时段期间编程的偏移电压voffset影响。

[0127]

δvq=v

data-(v

ref

+v

offset

)

[0128][0129]

在数据写入时段期间,可阻挡施加至驱动晶体管的漏极电极的像素驱动电压。因而,在没有电流流过驱动晶体管时,第一像素节点q与第二像素节点a之间的电压变化δ(v

q-va)可表示为下面的表达式(12)。当在数据写入时段期间电流流入第二像素节点a时,第二像素节点a的电压变化产生错误。因此,根据本发明的示例性实施方式,在没有电流流入第二像素节点a的同时进行数据写入时段。

[0130][0131]

其中δvq是第一像素节点q的电压变化,α是传输率。

[0132]

传输率α可由像素的电容~cp/(cp+cst)确定,与晶体管特性无关。考虑到传输率α,通过耦合并添加第一像素节点q的电压变化δvq,在没有电流流过驱动晶体管时存储电容器cst的电压,即驱动晶体管的栅极-源极电压v

gs

可表示为下面的等式(13):

[0133]vgs

=α(v

data-(v

ref

+v

offset

))+dv

qa

+v

t

+δv

th

+δv

[0134]

=α(v

data-v

ref

)+v

t

+δv

th

+dv

[0135][0136]

如表达式(13)中所表示的,在像素的数据写入时段期间添加至存储电容器cst的电压可表示为α(vdata-vref-voffset)。因而,用于补偿像素之间的采样电压变化δv的数据偏移电压voffset可被编程(或设置)为满足下面的等式(14)的条件:

[0137]

αv

offset

=δv+c1+o(δv)2ꢀꢀꢀ

(14)

[0138]

其中c1是常数,o(δv)2是采样电压变化δv的二阶函数。任选地,表达式(14)可包括采样电压变化δv以外的其他变化,这种情形也可被去除。

[0139]

此外,在采样时段、偏移电压形成时段和数据写入时段之后存储电容器cst中存储的电压vcst可表示为下面的表达式(15):

[0140]vcst

=α(v

data-v

ref

)+v

t

+δv

th

+c2ꢀꢀꢀ

(15)

[0141]

其中c2是常数。

[0142]

根据本发明一示例性实施方式,如表达式(16)中所表示的,在每个像素的数据写入时段之后驱动晶体管的电流和电压可具有由与阈值电压v

th

(v

t

+δv

th

+c)对应的采样电压变化δv导致的差。当偏移电压形成时段tf设为最佳偏移电压形成时间t0,使得在下面的表达式(17)中左侧的电压等于右侧的电压时,上述差可表示为下面的表达式(18)。

[0143]

i(v

gs

)=i0g(α(v

data-v

ref

)+dv)

[0144][0145][0146][0147]

dv=c+o(δv)2(@tf=t0)

ꢀꢀꢀ

(17)

[0148][0149][0150][0151]

因此,驱动晶体管的电流i(v

gs

)与阈值电压的变化δv

th

无关,如下面的表达式(19)中所示:

[0152]

i(v

gs

)=i0g(α(v

data-v

ref

)-g

′

(0)-1

)

ꢀꢀꢀ

(19)

[0153]

根据本发明一示例性实施方式,在偏移电压形成时段期间,第一像素节点的电压可根据噪声电压vn(例如,反冲电压)以及基于电流而编程的数据偏移电压进行变化。在这种情形中,噪声电压vn可添加至如表达式(9)和表达式(10)的数据偏移电压voffset的等

式。在这种情形中,驱动晶体管的栅极-源极电压v

gs

变化了“传输率

×

vn”,但该变化可在数据写入时段期间被去除。此外,采样时段期间的采样电流可根据由噪声电压vn导致的驱动晶体管的栅极-源极电压v

gs

的变化而变化,这可表示为表达式(5)的采样电压v

t

的变化。

[0154]

根据本发明一示例性实施方式,当在每个像素的发光时段的初始阶段添加与驱动晶体管的阈值电压成近似线性比例的附加电压时,可设定数据偏移电压voffset,以补偿(或减去)该附加电压kδv(δv

th

),如下面的表达式(20)中所示:

[0155][0156]

根据本发明一示例性实施方式,在像素的发光时段的起点(或在沉降时段期间(settling period)),根据驱动晶体管的阈值电压,可发生电压的变化(βδv

th

),如下面的表达式(21)中所示,其中β表示由驱动晶体管的迁移率和寄生电容确定的恒定值。此外,通过将数据偏移电压voffset设为满足下面表达式(22)的最佳电压形成时间t0和电压变化δv的条件,可补偿电压的变化。

[0157]

βδv

th

(=βg(vi)δv)

ꢀꢀꢀ

(21)

[0158][0159][0160]

当假设根据本发明示例性实施方式的最佳偏移电压形成时间附近的时间t为t0+δt时,采样电压变化δv对应于阈值电压变化δv

th

的栅极电压g(vi),因而电压变化dv可表示为下面的表达式(23):

[0161][0162][0163][0164][0165]

最佳偏移电压形成时间附近的时间t和阈值电压变化δv

th

(其赋予像素之间的预定变化)可具有如下面的表达式(24)所示的双曲线关系:

[0166][0167]

考虑到采样时间ts与最佳偏移电压形成时间t0之间的关系,可获得下面的表达式(25)。可通过减小采样时间ts减小最佳偏移电压形成时间t0。因此,根据本发明的示例性实施方式,偏移电压形成时段t0可设为比采样时间ts长,例如,偏移电压形成时段t0可设为是

采样时间ts的二到六倍长。在这种情形中,采样时间ts可设为等于或小于1.5个水平周期。

[0168][0169][0170][0171]

其中s是驱动晶体管的s因子(亚阈值斜率(sub-threshold slope))。

[0172]

因此,当考虑到采样时间ts设定偏移电压形成时段t0时,驱动晶体管的电流i(v

gs

)可表示为下面的表达式(26)。在这种情形中,由阈值电压的变化导致的电流的变化可根本上被消除。

[0173][0174]

结果,根据本发明示例性实施方式的发光显示设备可通过采样时段与数据写入时段之间的每个像素的偏移电压形成时段,在驱动晶体管的栅极电极(例如,第一像素节点)处形成数据偏移电压voffset。因此,可补偿像素之间的采样电压变化以及设置于像素中的驱动晶体管之间的阈值电压变化,由此减小由设置于像素中的驱动晶体管之间的阈值电压变化导致的像素之间的电压变化,允许提高图像质量。

[0175]

图7是显示在图2和3中所示的根据本发明示例性实施方式的发光显示设备中,布置在同一水平行中并且包括具有不同阈值电压的驱动晶体管的三个像素的模拟操作结果的波形图。

[0176]

从图7能够看出,当像素的驱动晶体管具有不同的阈值电压时,可在偏移电压形成时段ovfp期间在与驱动晶体管的栅极电极连接的第一像素节点处形成具有不同幅度的数据偏移电压voffset。因此,可通过在偏移电压形成时段ovfp期间形成在第一像素节点处的数据偏移电压voffset补偿像素之间的电压变化以及设置于像素中的驱动晶体管之间的阈值电压变化。

[0177]

根据本发明,发光显示设备及其驱动方法不限于图2到4中所示的像素结构。这些像素可应用于按照初始化时段、采样时段(或内部补偿时段)、数据写入时段和发光时段的顺序进行操作的任何发光显示设备及其驱动方法。在这种情形中,通过在采样时段与数据写入时段之间插入具有比采样时段长的时间的偏移电压形成时段,可具有相同的效果。

[0178]

利用根据本发明示例性实施方式的发光显示设备及其驱动方法,可补偿像素之间的采样电压变化以及设置于像素中的驱动晶体管之间的阈值电压变化,由此减小由设置于像素中的驱动晶体管之间的阈值电压变化导致的像素之间的采样电压变化,允许提高图像质量。

[0179]

本发明不限于前述示例性实施方式和附图,在不背离本发明的精神的情况下,可进行各种替换、修改和变化,这对于所属领域技术人员来说将是显而易见的。因此,本发明的范围可由所附权利要求书限定,从权利要求书的含义和范围及其等同得到的所有变化或

修改应当解释为包括在本发明的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1