像素电路、像素结构及显示面板的制作方法

本申请涉及显示,尤其涉及像素电路、像素结构及显示面板。

背景技术:

1、随着micro led技术的快速发展,用户对于车载产品实现全彩的要求也越来越高,传统的实现产品全彩显示的像素排列方式是通过三原色的rgb micro led依次排列,将三原色的led转移到驱动背板上实现全彩显示,这种实现产品全彩显示的像素排列方式存在很大的缺陷,在三原色led中红色像素会由于本身性质,造成衰减程度远大于绿色像素和蓝色像素衰减程度的问题,进而造成色偏的现象,因此,急需一种新的像素排列方式来改善因红色像素造成色偏。

技术实现思路

1、本申请的主要目的在于提供一种像素电路、像素结构及显示面板,旨在如何改善因红色像素造成色偏的技术问题。

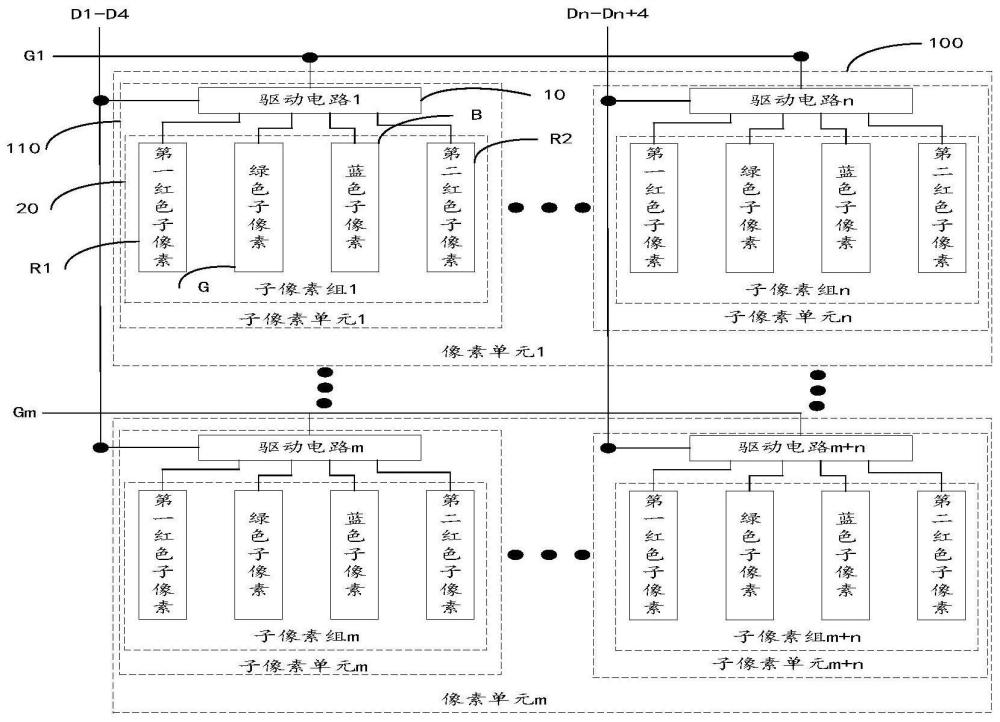

2、为实现上述目的,本申请提供一种像素电路,所述像素电路包括多行像素单元,所述像素单元通过不同数据线依次连接,所述像素单元包括多组子像素单元,所述子像素单元通过栅极驱动线依次连接,所述子像素单元包括驱动电路和子像素组,所述子像素组包括第一红色子像素、绿色子像素、蓝色子像素和第二红色子像素;

3、所述驱动电路的控制端与所述栅极驱动线连接,所述驱动电路的第一端与所述数据线连接,所述驱动电路的第二端分别与所述第一红色子像素、所述绿色子像素、所述蓝色子像素和所述第二红色子像素连接;

4、其中,所述驱动电路用于在奇数帧显示时,驱动所述第一红色子像素、所述绿色子像素和所述蓝色子像素进行显示;在偶数帧显示时,驱动所述绿色子像素、所述蓝色子像素和所述第二红色子像素进行显示。

5、可选地,所述数据线至少包括第一数据线、第二数据线、第三数据线和第四数据线,所述驱动电路包括第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管和第四薄膜晶体管;

6、所述第一薄膜晶体管的控制端与所述栅极驱动线连接,所述第一薄膜晶体管的第一端与所述第一数据线连接,所述第一薄膜晶体管的第二端与所述第一红色子像素连接,所述第二薄膜晶体管的控制端与所述栅极驱动线连接,所述第二薄膜晶体管的第一端与所述第二数据线连接,所述第二薄膜晶体管的第二端与所述绿色子像素连接,所述第三薄膜晶体管的控制端与所述栅极驱动线连接,所述第三薄膜晶体管的第一端与所述第三数据线连接,所述第三薄膜晶体管的第二端与所述蓝色子像素连接,所述第四薄膜晶体管的控制端与所述栅极驱动线连接,所述第四薄膜晶体管的第一端与所述第四数据线连接,所述第四薄膜晶体管的第二端与所述第二红色子像素连接。

7、可选地,所述像素电路还包括第一电致变色层、第一控制信号端、第二电致变色层和第二控制信号端,所述第一电致变色层设置在所述第一红色子像素上,并与所述第一控制信号端连接,所述第二电致变色层设置在所述第二红色子像素上,并与所述第二控制信号端连接。

8、可选地,在所述奇数帧显示时,所述第一数据线、所述第二数据线和所述第三数据线分别输出第一数据信号,并基于所述第一数据信号驱动所述第一红色子像素、所述绿色子像素和所述蓝色子像素进行显示。

9、可选地,所述第一控制信号端输出导通控制信号,控制所述第一电致变色层为透明状态,所述第二控制信号端输出关闭控制信号,控制所述第二电致变色层为黑态状态。

10、可选地,在所述偶数帧显示时,所述第二数据线、所述第三数据线和所述第四数据线分别输出第二数据信号,并基于所述第二数据信号驱动所述绿色子像素、所述蓝色子像素和所述第二红色子像素进行显示。

11、可选地,所述第一控制信号端输出关闭控制信号,控制所述第一电致变色层为黑态状态,所述第二控制信号端输出导通控制信号,控制所述第二电致变色层为透明状态。

12、此外,为实现上述目的,本申请还提供一种像素结构,所述像素结构包括上述阵列基板行驱动电路,所述像素结构包括驱动背板、封装层和多个电极;

13、所述封装层和所述像素电路中的驱动电路设置在所述驱动背板上,所述像素电路中的第一红色子像素的第一侧、绿色子像素的第一侧、蓝色子像素的第一侧和第二红色子像素的第一侧与所述封装层远离所述驱动背板的一侧对齐并封装在所述封装层内,所述第一红色子像素、所述绿色子像素、所述蓝色子像素和所述第二红色子像素以第一间距依次封装,所述第一红色子像素的第二侧、绿色子像素的第二侧、蓝色子像素的第二侧和第二红色子像素的第二侧分别通过所述电极与驱动背板连接,其中,所述第二侧与所述第一侧为子像素的相对侧。

14、可选地,所述像素结构还包括第一电致变色层和第二电致变色层,所述第一电致变色层设置在所述第一红色子像素的第一侧上,所述第二电致变色层设置在所述第二红色子像素的第一侧上。

15、此外,为实现上述目的,本申请还提供一种显示面板,所述显示面板包括阵列基板,所述阵列基板包括如上所述的像素结构。

16、本申请提出一种像素电路、像素结构及显示面板,本申请针对像素电路进行了优化,得到了一种像素电路,该像素电路包括:通过不同数据线依次连接的多行像素单元,像素单元中包括通过栅极驱动线依次连接的多组子像素单元,子像素单元包括驱动电路、第一红色子像素、绿色子像素、蓝色子像素和第二红色子像素。由于在三原色led中红色像素会由于本身性质,造成衰减程度远大于绿色像素和蓝色像素衰减程度的问题,进而造成色偏的问题,本申请结合上述各模块,在奇数帧显示时,驱动第一红色子像素、绿色子像素和蓝色子像素进行显示;在偶数帧显示时,驱动绿色子像素、蓝色子像素和第二红色子像素进行显示,进而降低了红色子像素的使用时间,使红色子像素的衰减程度大大降低,改善了因红色像素造成色偏的问题。

技术特征:

1.一种像素电路,其特征在于,所述像素电路包括多行像素单元,所述像素单元通过不同数据线依次连接,所述像素单元包括多组子像素单元,所述子像素单元通过栅极驱动线依次连接,所述子像素单元包括驱动电路和子像素组,所述子像素组包括第一红色子像素、绿色子像素、蓝色子像素和第二红色子像素;

2.如权利要求1所述的像素电路,其特征在于,所述数据线至少包括第一数据线、第二数据线、第三数据线和第四数据线,所述驱动电路包括第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管和第四薄膜晶体管;

3.如权利要求2所述的像素电路,其特征在于,所述像素电路还包括第一电致变色层、第一控制信号端、第二电致变色层和第二控制信号端,所述第一电致变色层设置在所述第一红色子像素上,并与所述第一控制信号端连接,所述第二电致变色层设置在所述第二红色子像素上,并与所述第二控制信号端连接。

4.如权利要求3所述的像素电路,其特征在于,在所述奇数帧显示时,所述第一数据线、所述第二数据线和所述第三数据线分别输出第一数据信号,并基于所述第一数据信号驱动所述第一红色子像素、所述绿色子像素和所述蓝色子像素进行显示。

5.如权利要求4所述的像素电路,其特征在于,所述第一控制信号端输出导通控制信号,控制所述第一电致变色层为透明状态,所述第二控制信号端输出关闭控制信号,控制所述第二电致变色层为黑态状态。

6.如权利要求3所述的像素电路,其特征在于,在所述偶数帧显示时,所述第二数据线、所述第三数据线和所述第四数据线分别输出第二数据信号,并基于所述第二数据信号驱动所述绿色子像素、所述蓝色子像素和所述第二红色子像素进行显示。

7.如权利要求6所述的像素电路,其特征在于,所述第一控制信号端输出关闭控制信号,控制所述第一电致变色层为黑态状态,所述第二控制信号端输出导通控制信号,控制所述第二电致变色层为透明状态。

8.一种像素结构,其特征在于,所述像素结构包括如权利要求1-7任一项所述的像素电路,所述像素结构包括驱动背板、封装层和多个电极;

9.权利要求8所述的像素结构,其特征在于,所述像素结构还包括第一电致变色层和第二电致变色层,所述第一电致变色层设置在所述第一红色子像素的第一侧上,所述第二电致变色层设置在所述第二红色子像素的第一侧上。

10.一种显示面板,其特征在于,所述显示面板包括阵列基板,所述阵列基板包括如权利要求8-9任一项所述的像素结构。

技术总结

本申请公开了一种像素电路、像素结构及显示面板,属于显示技术领域。本申请的像素电路包括:多行像素单元,像素单元通过不同数据线依次连接,像素单元包括多组子像素单元,子像素单元通过栅极驱动线依次连接,子像素单元包括驱动电路、第一红/绿/蓝/第二红色子像素;驱动电路的控制端与栅极驱动线连接,驱动电路的第一端与数据线连接,驱动电路的第二端与第一红/绿/蓝/第二红色子像素连接;其中,驱动电路用于在奇数帧显示时,驱动第一红/绿/蓝色子像素进行显示;在偶数帧显示时,驱动绿/蓝/第二红色子像素进行显示,进而改善了因红色像素造成色偏。

技术研发人员:王然龙,叶利丹

受保护的技术使用者:惠科股份有限公司

技术研发日:

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!