阵列基板及其制造方法、液晶面板与流程

本技术涉及显示,特别涉及一种阵列基板及其制造方法、液晶面板。

背景技术:

1、为了满足人们对大尺寸画面的观看需求,需要在显示装置中装配大尺寸的显示面板。

2、目前,在制备大尺寸的显示面板时,显示面板中的图案化的膜层结构往往需要借助拼接曝光工艺形成。例如,在需要制作大尺寸的显示面板中的一个图案化的膜层结构时,首先,需要在基板上形成整层设置的膜层结构并涂覆光刻胶;之后,采用同一个掩膜板对光刻胶中的不同的分区分别进行一次曝光;然后,对曝光后的光刻胶进行显影,并刻蚀基板上形成的整层设置的膜层结构;最后,将基板上的光刻胶进行剥离,即可在基板上形成图案化的膜层结构。

3、然而,目前在对基板上的光刻胶薄膜进行曝光时,需要在两个分区之间的拼接区内设置挡板,且在对不同分区均进行曝光后,单独再对拼接区进行曝光,如此,在制作大尺寸的显示面板中的图案化的膜层结构时,需要进行多次曝光,导致大尺寸的显示面板的制造工艺较为复杂。

技术实现思路

1、本技术实施例提供了一种阵列基板及其制造方法、液晶面板。可以解决现有技术的大尺寸的显示面板的制造工艺较为复杂的问题,所述技术方案如下:

2、一方面,提供了一种阵列基板,所述阵列基板具有显示区,以及位于所述显示区外围的非显示区;所述阵列基板包括:

3、衬底,以及位于所述衬底上的多个层叠设置的图案化的膜层结构;

4、其中,多个所述图案化的膜层结构用于组成多个子像素,所述多个子像素包括:位于所述显示区内的多个第一子像素,以及位于所述非显示区内的多个虚拟子像素;

5、所述虚拟子像素中的像素电极在所述衬底上的正投影的面积,大于所述第一子像素中的像素电极在所述衬底上的正投影的面积。

6、可选的,所述显示区包括:阵列排布的多个正常显示区,以及位于相邻的两个所述正常显示区之间的第一拼接显示区;所述正常显示区内分布有多个所述第一子像素,所述多个子像素还包括:位于所述第一拼接显示区内的多个第二子像素;

7、其中,所述第二子像素中的像素电极在所述衬底上的正投影的面积,小于或等于所述第一子像素中的像素电极在所述衬底上的正投影的面积。

8、可选的,所述多个子像素还包括:多个第三子像素,所述第三子像素中的一部分位于所述正常显示区内,另一部分位于所述第一拼接显示区内;

9、在平行于所述第一拼接显示区的长度方向上,所述第三子像素中位于所述第一拼接显示区内的部分的宽度,小于或等于所述第三子像素中位于所述正常显示区内的部分的宽度。

10、可选的,所述显示区还包括:位于沿行方向排布的两个第一拼接显示区和沿列方向排布的两个第一拼接显示区之间的第二拼接显示区,所述多个子像素还包括:位于所述第二拼接显示区内的第四子像素;

11、其中,所述第四子像素中的像素电极在所述衬底上的正投影的面积,小于或等于所述第二子像素中的像素电极在所述衬底上的正投影的面积。

12、可选的,所述正常显示区具有多个对位区域;

13、多个所述图案化的膜层结构中最靠近所述衬底的膜层结构为第一导电层,所述第一导电层包括:位于所述对位区域内的多个第一对位结构;

14、多个所述图案化的膜层结构中除所述第一导电层之外的膜层结构均包括:位于所述对位区域内的一个第二对位结构,各个所述膜层结构中的第二对位结构在所述衬底上的正投影各不重合;

15、同一个所述对位区域内的多个第一对位结构与多个第二对位结构一一对应,所述第一对位结构在所述衬底上的正投影与对应的第二对位结构在所述衬底上的正投影之间的位置关系满足预设位置关系。

16、可选的,各个所第一对位结构在所述衬底上的正投影位于不同的第一子像素在所述衬底上的正投影内,且所述第一对位结构与对应的第二对位结构在所述衬底上的正投影位于同一个第一子像素在所述衬底上的正投影内。

17、可选的,所述第一对位结构包括:至少一个第一条形结构和至少一个第二条形结构,所述第一条形结构的长度方向与所述第二条形结构的长度方向相交;

18、与所述第一对位结构对应的第二对位结构包括:至少一个第三条形结构和至少一个第四条形结构;

19、其中,所述第三条形结构的长度方向平行于所述第一条形结构的长度方向,且所述第三条形结构在所述衬底上的正投影,与所述第一条形结构在所述衬底上的正投影之间的距离在第一预设值范围内;

20、所述第四条形结构的长度方向平行于所述第二条形结构的长度方向,且所述第四条形结构在所述衬底上的正投影,与所述第二条形结构在所述衬底上的正投影之间的距离在第二预设范围内。

21、可选的,所述第一条形结构和所述第二条形结构的个数均为一个,所述第二对位结构中的第三条形结构和第四条形结构的个数均为两个;

22、所述第一条形结构位于两个所述第三条形结构之间,且两个所述第三条形结构在所述衬底上的正投影,与所述第一条形结构在所述衬底上的正投影之间的距离之差小于第一预设阈值;

23、所述第二条形结构位于两个所述第四条形结构之间,且两个所述第四条形结构在所述衬底上的正投影,与所述第二条形结构在所述衬底上的正投影之间的距离之差小于第二预设阈值。

24、可选的,所述第一对位结构为电极块,所述第一条形结构和所述第二条形结构均为位于所述电极块内的条形凹槽,所述第二对位结构在所述衬底上的正投影位于对应的第一对位结构在所述衬底上的正投影内。

25、可选的,多个所述图案化的膜层结构中除所述第一导电层之外的膜层结构分别为:有源层图案、第二导电层、平坦层和像素电极层,所述有源层图案、所述第二导电层、所述平坦层和所述像素界定层依次沿垂直且远离所述衬底的方向层叠设置;

26、所述阵列基板还包括:位于所述有源层图案和所述第一导电层之间的整层设置的栅极绝缘层;

27、所述有源层图案、所述第二导电层和像素电极层中的第三条形结构和第四条形结构均为条形凸起;所述平坦层中的第三条形结构和第四条形结构均为条形凹槽。

28、可选的,所述第一导电层还包括:所述子像素中的薄膜晶体管的栅极,以及与所述栅极电连接的栅线;

29、所述有源层图案还包括:所述子像素中的薄膜晶体管的有源层;

30、所述第二导电层还包括:所述子像素中的薄膜晶体的第一极和第二极,以及与所述第一极电连接的数据线;

31、所述平坦层还具有连接过孔;

32、所述像素电极层还包括:所述子像素中的像素电极,所述像素电极通过所述连接过孔与所述第二极电连接。

33、可选的,在所述衬底上正投影与所述像素电极层中的第二对位结构交叠的第一子像素内未设置像素电极;

34、或者,在所述衬底上正投影与所述像素电极层中的第二对位结构交叠的第一子像素内的像素电极具有镂空结构,所述像素电极层中的第二对位结构以及对应的第一对位结构在所述衬底上的正投影,均位于所述镂空结构在所述衬底上的正投影内。

35、可选的,所述第一导电层还包括:辅助信号线,所述辅助信号线在所述衬底上的正投影与至少部分子像素中的像素电极在所述衬底上的正投影存在交叠区域,且与所述第一对位结构在所述衬底上的正投影不重合。

36、可选的,所述辅助信号线包括:辅助信号线本体,以及与所述辅助信号线本体电连接的弯折绕线,所述第一对位结构中的至少部分位于所述弯折绕线所围成的区域内。

37、可选的,所述第一导电层还包括:位于所述对位区域内的多个辅助对位结构,所述多个辅助对位结构与所述多个第一对位结构一一对应,所述辅助对位结构和对应的第一对位结构在所述衬底上的正投影位于同一个第一子像素在所述衬底上的正投影内。

38、可选的,所述正常显示区中的所述多个对位区域均匀分布在所述正常显示区的边缘位置处。

39、另一方面,提供了一种阵列基板的制造方法,所述阵列基板具有显示区,以及位于所述显示区外围的非显示区;所述方法包括:

40、在衬底上依次形成多个层叠设置的图案化的膜层结构;

41、其中,多个所述图案化的膜层结构用于组成多个子像素,所述多个子像素包括:位于所述显示区内的多个第一子像素,以及位于所述非显示区内的多个虚拟子像素;

42、所述虚拟子像素中的像素电极在所述衬底上的正投影的面积,大于所述第一子像素中的像素电极在所述衬底上的正投影的面积。

43、可选的,所述显示区包括:阵列排布的多个正常显示区,以及位于相邻的两个所述正常显示区之间的第一拼接显示区;形成每个所述图案化的膜层结构,包括:

44、在所述衬底上形成整层设置的膜层结构;

45、在所述膜层结构上形成光刻胶薄膜,并采用掩膜板依次对所述光刻薄膜中位于所述多个正常显示区内的部分执行曝光操作;

46、对曝光后的所述光刻胶薄膜进行显影处理,并对所述整层设置的膜层结构进行刻蚀处理,以在所述衬底上形成图案化的膜层结构;

47、其中,对所述光刻胶薄膜中位于一个正常显示区内的部分执行的曝光操作,包括:

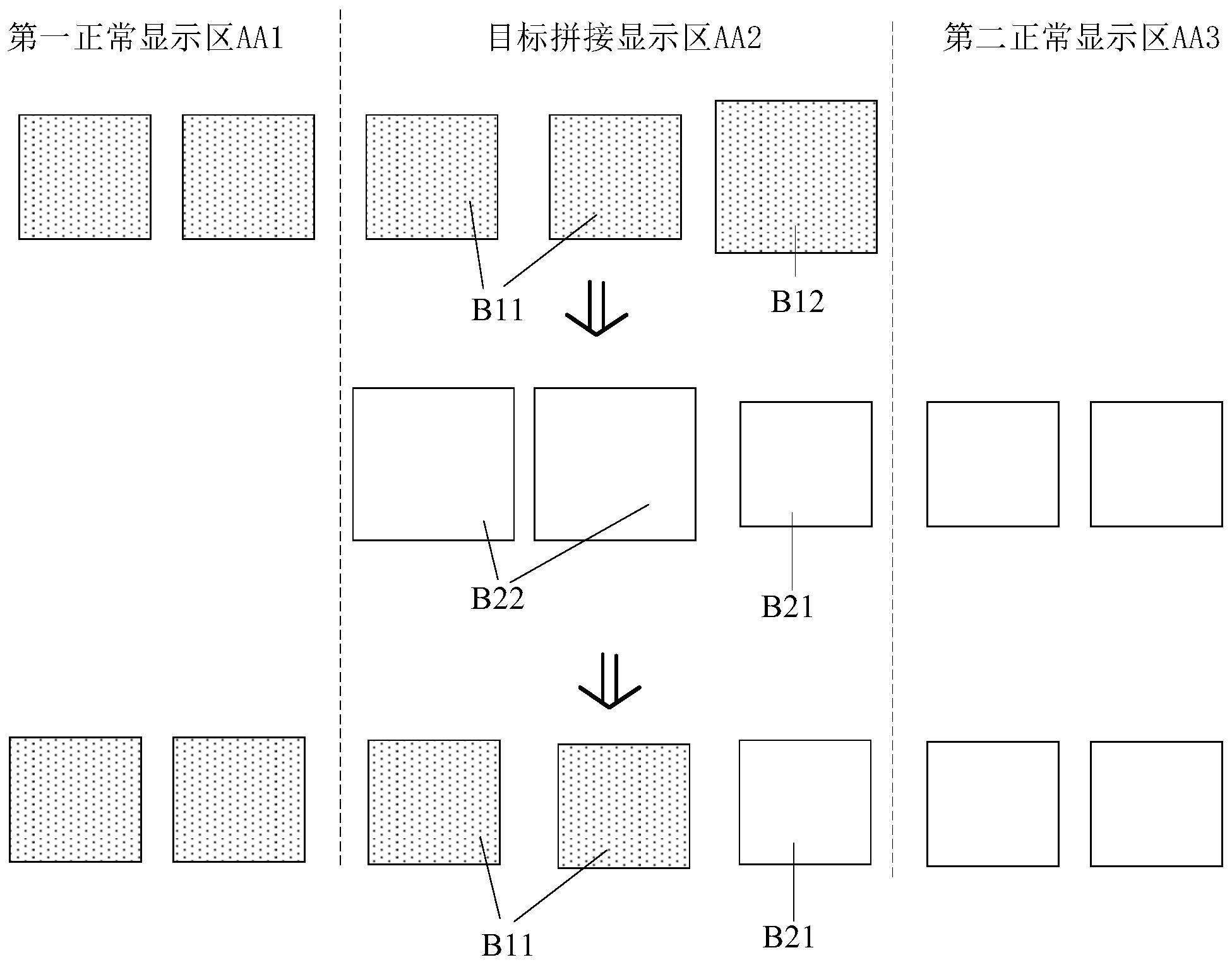

48、采用所述掩膜板中的第一掩膜在第一正常显示区和目标拼接显示区内形成第一曝光区,且采用所述掩膜板中的第二掩膜在所述非显示区和所述目标第一拼接显示区内形成第二曝光区;

49、沿朝向第二正常显示区的方向移动所述掩膜板,直至所述第一掩膜能够覆盖所述第二正常显示区以及位于所述目标拼接显示区内的第二曝光区,且所述第二掩膜能够覆盖位于所述目标拼接显示区内的第一曝光区;

50、所述第一正常显示区为所述多个正常显示区中的任一正常显示区,所述第二正常显示区为与所述第一正常显示区相邻的正常显示区,所述目标拼接显示区为位于所述第一正常显示区与所述第二正常显示区之间的第一拼接显示区。

51、可选的,所述第一曝光区的单面面积小于所述第二曝光区的单位面积。

52、又一方面,提供了一种液晶面板,包括:相对设置的阵列基板和彩膜基板,以及位于所述阵列基板和所述彩膜基板之间的液晶层,所述阵列基板为上述任意的阵列基板。

53、本技术实施例提供的技术方案带来的有益效果至少包括:

54、一种阵列基板包括:衬底,以及位于衬底上的多个层叠设置的图案化的膜层结构。由于图案化的膜层结构中位于第一拼接显示区内的部分是基于掩膜板的第一掩膜和第二掩膜形成的,且基于这个掩膜板中的第一掩膜还能够形成图案化的膜层结构中位于正常显示区内的部分,基于这个掩膜板中的第二掩膜还能够形成图案化的膜层结构中位于非显示区内的部分。因此,在形成这个阵列中的图案化的膜层结构的过程中,无需使用额外的掩膜板单独对第一拼接显示区内的光刻胶进行曝光,有效的减少了曝光次数,进而简化了后续基于这个阵列基板所制备出的大尺寸的显示面板的制造工艺。并且,在形成第一拼接显示区内的膜层结构的过程中,需要进行两次曝光,而在两次曝光的过程中均同时采用了掩膜板中的第一掩膜和第二掩膜,且在两次曝光后并对光刻胶薄膜进行显影后,均仅会保留了基于第一掩膜形成第一曝光区内的光刻胶。因此,在阵列基板中基于同一个掩膜板形成的图案化的膜层结构中,位于第一拼接显示区内的部分图案的单位面积近似等于位于正常显示区内的部分图案的单位面积。如此,本技术实施例中的阵列基板内的各个图案化的膜层结构的均匀性较好,使得后续基于这个阵列基板形成的显示面板的显示效果较好。

- 还没有人留言评论。精彩留言会获得点赞!