阵列基板和显示装置的制作方法

本说明书所公开的技术涉及阵列基板和显示装置。

背景技术:

1、作为现有的显示装置的一个例子,已知下述专利文献1所记载的显示装置。专利文献1所记载的显示装置具备:像素电极;共用电极,其隔着绝缘膜与像素电极重叠;开关元件,其连接到像素电极;像素配线,其连接到开关元件并以与像素电极相邻的方式配置;以及配线,其相对于像素电极在与像素配线相同的一侧相邻,多个配线之间空开间隔配置,并电连接到共用电极,多个配线分别具有相对于像素配线成为共用的位置关系的共用部。另外,专利文献1所记载的显示装置具备:多个位置检测电极,其将共用电极分割而成;第2像素配线,其与像素配线交叉,并配置为与将多个位置检测电极分隔开的分隔开口部重叠;以及屏蔽部,其与第2像素配线重叠,电连接到配线。

2、现有技术文献

3、专利文献

4、专利文献1:美国专利申请公开第2020/0272012号说明书

技术实现思路

1、发明要解决的问题

2、在上述的专利文献1所记载的显示装置中,第2像素配线为与分隔开口部重叠的配置,因此从第2像素配线产生的电场虽然不会被位置检测电极屏蔽,但是被与第2像素配线重叠的屏蔽部屏蔽。然而,当在与第2像素配线重叠的位置设置屏蔽部时,由于避免其它电极等与屏蔽部的短路等理由,需要确保屏蔽部的配置空间大。于是,为了防止屏蔽部附近的结构被视觉识别出,需要扩大遮光范围,像素的开口率有可能降低。若要采取用于使像素的开口率不降低的对策,则其结果会是显示亮度有可能产生不均。

3、本说明书记载的技术是基于上述的情况而完成的,其目的在于使像素的开口率不易降低,使显示亮度不易产生不均。

4、用于解决问题的方案

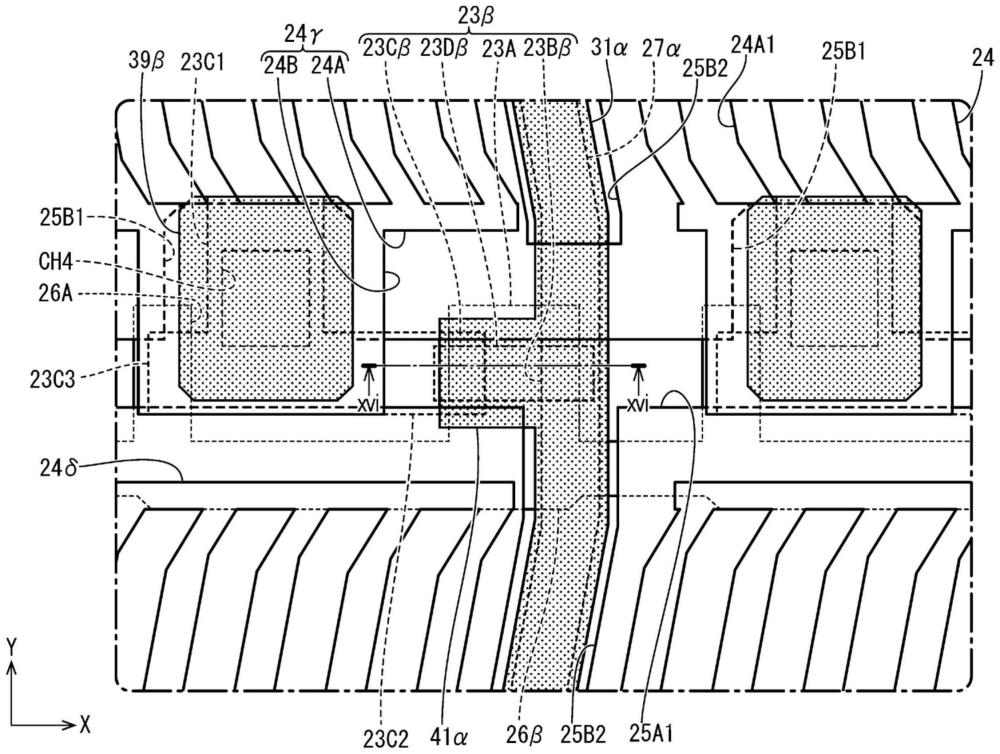

5、(1)本说明书记载的技术所涉及的阵列基板具备:多个共用电极;多个像素电极,其配置为隔着第1绝缘膜与所述多个共用电极重叠;多个开关元件,其连接到所述多个像素电极;以及多个配线,其连接到所述多个共用电极中的任意一个共用电极或者所述多个开关元件中的任意一个开关元件,所述多个像素电极包含:第1像素电极;第2像素电极,其相对于所述第1像素电极在第1方向上空开间隔配置;第3像素电极;以及第4像素电极,其相对于所述第3像素电极在所述第1方向上空开间隔配置,所述多个配线包含:第1配线,其在所述第1方向上位于所述第1像素电极与所述第2像素电极之间,沿着与所述第1方向交叉的第2方向延伸;以及第2配线,其在所述第1方向上位于所述第3像素电极与所述第4像素电极之间,沿着所述第2方向延伸,所述多个开关元件包含:第1开关元件,其连接到所述第1配线和所述第1像素电极;以及第2开关元件,其连接到所述第2配线和所述第3像素电极,所述多个共用电极包含:第1共用电极;以及第2共用电极,其相对于所述第1共用电极在所述第1方向上空开间隔配置,所述第1开关元件具有第1半导体部,所述第2开关元件具有第2半导体部,所述第1共用电极配置为与所述第1像素电极、所述第2像素电极、所述第3像素电极、所述第1配线以及所述第1开关元件中的至少所述第1半导体部重叠,所述第2共用电极配置为与所述第4像素电极和所述第2配线重叠,具备配置为与所述第2开关元件中的至少所述第2半导体部重叠并被设为与所述多个共用电极中的任意一个共用电极相同的电位的重叠部。

6、(2)另外,上述阵列基板在上述(1)的基础上也可以是,所述多个共用电极是多个位置检测电极,所述第1共用电极是第1位置检测电极,所述第2共用电极是第2位置检测电极,所述多个配线包含:第3配线,其沿着所述第1方向延伸,连接到所述多个位置检测电极中的任意一个位置检测电极;以及第4配线,其沿着所述第1方向延伸,至少连接到所述第2开关元件,所述第3配线的至少一部分配置为隔着第2绝缘膜与所述第4配线重叠,所述第3配线的一部分配置为与所述第2半导体部重叠,所述重叠部包含第1重叠部,所述第1重叠部由所述第3配线中的与所述第2半导体部重叠的部分构成。

7、(3)另外,上述阵列基板在上述(2)的基础上也可以是,所述第2开关元件具有第1电极,所述第1电极连接到所述第2半导体部的一部分,并配置为与所述第3像素电极的一部分重叠,具备配置为与所述第1电极的一部分和所述第3像素电极的一部分重叠的第2电极,所述第3配线包括相对于所述多个位置检测电极和所述多个像素电极均隔着第3绝缘膜位于下层侧的第1导电膜,所述第4配线包括相对于所述第1导电膜隔着所述第2绝缘膜位于下层侧的第2导电膜,所述第1电极包括所述第2导电膜中的与所述第4配线不同的部分,所述第2电极包括所述第1导电膜中的与所述第3配线和所述第1重叠部不同的部分,连接到所重叠的所述第3像素电极和所述第1电极,所述第1重叠部相对于所述第2电极在所述第2方向上空开间隔排列配置。

8、(4)另外,上述阵列基板在上述(3)的基础上也可以是,所述第2开关元件具有第3电极,所述第3电极连接到所述第2半导体部中的不同于与所述第1电极的连接部位的部位,所述第3电极由所述第4配线的一部分构成,所述第1电极具有:第1部,其与所述第2电极重叠;以及第2部,其从所述第1部沿着所述第2方向伸出并连接到所述第2半导体部的一部分。

9、(5)另外,上述阵列基板在上述(2)至上述(4)中的任意一项的基础上也可以是,所述多个配线包含:第5配线,其沿着所述第1方向延伸,配置为与所述第1位置检测电极重叠而与所述第2位置检测电极不重叠并连接到所述第1位置检测电极;第6配线,其沿着所述第1方向延伸,配置为与所述第2位置检测电极重叠而与所述第1位置检测电极不重叠并连接到所述第2位置检测电极;以及第7配线,其沿着所述第1方向延伸,至少一部分配置为隔着所述第2绝缘膜与所述第5配线和所述第6配线重叠,所述多个开关元件包含连接到所述第2配线和所述第7配线的第3开关元件,所述第3开关元件具有第3半导体部,所述第5配线或者所述第6配线的一部分配置为与所述第3半导体部重叠,所述重叠部包含第2重叠部,所述第2重叠部由所述第5配线或者所述第6配线中的与所述第3半导体部重叠的部分构成。

10、(6)另外,上述阵列基板在上述(2)至上述(5)中的任意一项的基础上也可以是,所述多个位置检测电极包含相对于所述第1位置检测电极在所述第2方向上空开间隔排列的第3位置检测电极,所述多个配线包含:第8配线,其沿着所述第1方向延伸,配置为夹在所述第1位置检测电极与所述第3位置检测电极之间,并被设为与所述第1位置检测电极和所述第3位置检测电极不重叠的配置;以及第9配线,其沿着所述第1方向延伸,至少一部分配置为隔着所述第2绝缘膜与所述第8配线重叠,所述第8配线直接或者间接地连接到所述多个位置检测电极中的任意一个位置检测电极,所述多个开关元件包含连接到所述第2配线和所述第9配线的第4开关元件,所述第4开关元件具有第4半导体部,所述第8配线的一部分配置为与所述第4半导体部重叠,所述重叠部包含第3重叠部,所述第3重叠部由所述第8配线中的与所述第4半导体部重叠的部分构成。

11、(7)另外,上述阵列基板在上述(1)的基础上也可以是,所述多个共用电极是多个位置检测电极,所述第1共用电极是第1位置检测电极,所述第2共用电极是第2位置检测电极,所述多个配线包含:第10配线,其沿着所述第1方向延伸,连接到所述多个位置检测电极中的任意一个位置检测电极;以及第11配线,其沿着所述第1方向延伸,至少连接到所述第2开关元件,所述第11配线包括相对于所述多个位置检测电极和所述多个像素电极均隔着第4绝缘膜位于下层侧的第3导电膜,所述第10配线包括所述第3导电膜中的与所述第11配线不同的部分,相对于所述第11配线在所述第2方向上空开间隔排列配置,所述多个像素电极包括第4导电膜,所述重叠部包含第4重叠部,所述第4重叠部包括所述第4导电膜中的与所述多个像素电极不同的部分。

12、(8)另外,上述阵列基板在上述(7)的基础上也可以是,所述第4重叠部包含第5重叠部,所述第5重叠部具有与所述第1位置检测电极或者所述第2位置检测电极重叠的第3部,所述第5重叠部的所述第3部连接到所述第1位置检测电极或者所述第2位置检测电极。

13、(9)另外,上述阵列基板在上述(7)或上述(8)的基础上也可以是,所述第4重叠部包含第6重叠部,所述第6重叠部具有与所述第10配线重叠的第4部,所述第6重叠部的所述第4部连接到所述第10配线。

14、(10)另外,上述阵列基板在上述(1)至上述(9)中的任意一项的基础上也可以是,所述第1共用电极和所述第2共用电极被设为在所述第1方向上将所述第2半导体部夹在中间并与所述第2半导体部不重叠的配置,所述重叠部配置在与所述多个共用电极不同的层。

15、(11)另外,上述阵列基板在上述(1)的基础上也可以是,所述第1共用电极或者所述第2共用电极的一部分配置为与所述第2半导体部重叠,所述重叠部由所述第1共用电极或者所述第2共用电极中的与所述第2半导体部重叠的部分构成。

16、(12)本说明书记载的技术所涉及的显示装置具备:上述(1)至上述(11)中的任意一项所述的阵列基板;以及相对基板,其以与所述阵列基板相对的方式配置。

17、发明效果

18、根据本说明书记载的技术,能够使像素的开口率不易降低,使显示亮度不易产生不均。

- 还没有人留言评论。精彩留言会获得点赞!