半导体装置的制作方法

本发明涉及一种半导体装置,例如,执行神经网络的处理的半导体装置。

背景技术:

1、专利文件1(日本专利申请特开no.2019-207458)示出了一种通过使用具有多个存储体的存储器对多个中间层(配置卷积神经网络)执行操作的方法。在该方法中,基于针对多个中间层中的每个中间层的输入数据和输出数据所需的传送量和传送速率来适当地确定要作为输入数据的存储源或输出数据的存储目的地的存储体的分配。

技术实现思路

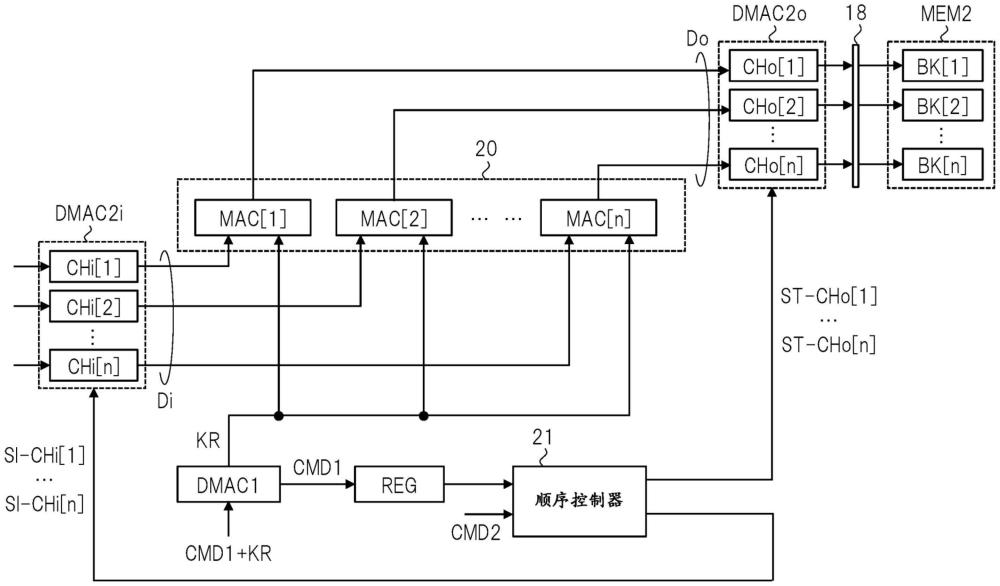

1、例如,在诸如cnn(卷积神经网络)的神经网络的处理中,通过使用安装在半导体装置上的多个dma(直接存储器访问)控制器和多个乘法-累加单元等来执行大量的算术处理。具体地,dma控制器通过将被存储在存储器中的特定卷积层的像素数据和权重参数传送到乘法-累加单元来使乘法-累加单元执行乘法-累加运算。此外,dma控制器将乘法-累加单元的(多个)运算结果作为下一卷积层的像素数据传送到存储器。半导体装置重复地执行这种处理。

2、为了灵活地处理神经网络的各种配置,这种半导体装置通常基于简单命令来操作。例如,如专利文件1中所公开的,记载了用于指定作为输入数据的存储源的存储体和作为输出数据的存储目的地的存储体的命令。然而,当使多个乘法-累加单元基于这种命令执行乘法-累加运算时,可能不总是有效地使用多个乘法-累加单元。结果,神经网络的处理时间可能比预期增加得多。

3、鉴于上述内容做出了后续所描述的实施例,并且根据本说明书的描述和附图,其它问题和新颖特征将变得明显。

4、根据一个实施例的半导体装置包括存储器、n个乘法-累加单元、输入dma控制器、输出dma控制器和顺序控制器,其中n是2或更大的整数。存储器具有可并行访问的n个存储体,并且存储像素数据。n个乘法-累加单元中的每个乘法-累加单元对多个像素数据片段和多个权重参数执行乘法-累加运算。输入dma控制器通过使用n个输入通道将被存储在存储器中的像素数据传送到n个乘法-累加单元中的每个乘法-累加单元。输出dma控制器通过使用n个输出通道分别将来自n个乘法-累加单元的像素数据传送到存储器。顺序控制器控制输入dma控制器,以使第一输入通道将输入存储体的第一像素空间中的像素数据传送到第一乘法-累加单元,并且使第二输入通道将同一输入存储体的第二像素空间中的像素数据传送到第二乘法-累加单元。

5、使用一个实施例的半导体装置使得可以缩短神经网络的处理时间。

技术特征:

1.一种半导体装置,包括:

2.根据权利要求1所述的半导体装置,

3.根据权利要求2所述的半导体装置,

4.根据权利要求1所述的半导体装置,

5.根据权利要求1所述的半导体装置,

6.一种由一个半导体芯片配置的半导体装置,所述半导体装置包括:

7.根据权利要求6所述的半导体装置,

8.根据权利要求7所述的半导体装置,

9.根据权利要求6所述的半导体装置,

10.根据权利要求6所述的半导体装置,

技术总结

本公开涉及一种半导体装置。第二存储器具有可并行访问的n个存储体,并且存储像素数据。输入DMA控制器通过使用n个输入通道将被存储在第二存储器中的像素数据分别传送到n个乘法‑累加单元。顺序控制器控制输入DMA控制器,以使第一输入通道将输入存储体的第一像素空间中的像素数据传送到第一乘法‑累加单元,并且使第二输入通道将同一输入存储体的第二像素空间中的像素数据传送到第二乘法‑累加单元。

技术研发人员:寺岛和昭,中村淳,R·吉米雷

受保护的技术使用者:瑞萨电子株式会社

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!