一种双次曝光方法与流程

本发明属于半导体制造,尤其涉及一种双次曝光方法。

背景技术:

1、曝光是集成电路制造中光刻工艺的重要工序之一,其目的是将掩模上的图案转移到涂有光刻胶的晶圆上。曝光过程中,掩模版上的图案通过投影透镜和光线的照射,在晶圆表面的光刻胶上形成对应的图形。

2、目前常用的曝光技术包括步进式曝光和扫描式曝光。其中,步进式曝光是将整个晶圆分为多个小区域,每个区域分别进行曝光,这种技术在一定程度上确保了曝光的高精度和低误差。然而,步进式曝光中通常采用单次曝光的方法,在不改变曝光机台结构的情况下单次曝光出的掩膜图形精度仍存在限制,使用现有的曝光机台无法进一步提高电路图形的分辨率、减小电路图形的特征尺寸,同时,现有的掩模版机台的开口大小存在限制,最大仅为26mm*33mm,导致常规机台无法曝光比26mm*33mm更大面积的掩模版。

3、当一些特殊制程中需曝光出更高精度的电路图形或需曝光比26mm*33mm更大面积的掩模版时,一种解决方法是通过定制化机台提高机台的曝光精度或增大掩模版机台的开口尺寸,但是定制化机台设备成本较高,且无法与常规尺寸的掩模版公用,这种解决方法极大提高了半导体芯片的生产成本;另一解决方法是通过双次曝光的方法提高曝光精度或曝光出大尺寸电路图形,然而,步进式曝光机台双次曝光的图形之间易存在偏移问题,导致产品的良品率降低。

技术实现思路

1、本发明的目的在于解决上述技术问题之一,提供一种双次曝光方法。

2、为实现上述目的,本发明采用的技术方案是:

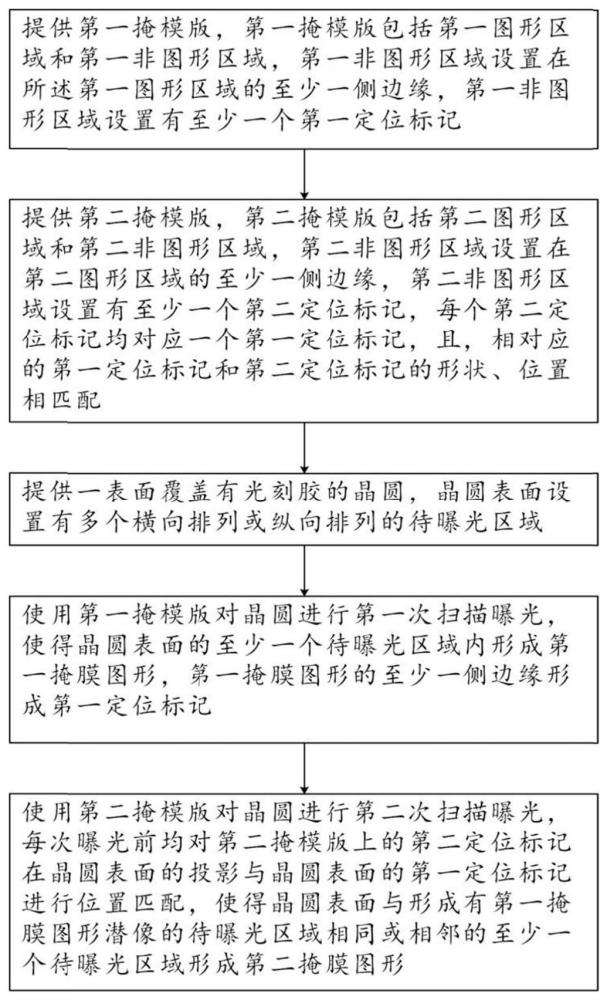

3、一种双次曝光方法,包括以下步骤:

4、提供第一掩模版,第一掩模版包括第一图形区域和第一非图形区域,第一非图形区域设置在第一图形区域的至少一侧边缘,第一非图形区域设置有至少一个第一定位标记;

5、提供第二掩模版,第二掩模版包括第二图形区域和第二非图形区域,第二非图形区域设置在第二图形区域的至少一侧边缘,第二非图形区域设置有至少一个第二定位标记,每个第二定位标记均对应一个第一定位标记,且,相对应的第一定位标记和第二定位标记的形状、位置相匹配;

6、提供一表面覆盖有光刻胶的晶圆,晶圆表面设置有多个横向排列或纵向排列的待曝光区域;

7、使用第一掩模版对晶圆进行第一次扫描曝光,使得晶圆表面的至少一个待曝光区域内形成第一掩膜图形,第一掩膜图形的至少一侧边缘形成第一定位标记;

8、使用第二掩模版对晶圆进行第二次扫描曝光,每次曝光前均对第二掩模版上的第二定位标记在晶圆表面的投影与晶圆表面的第一定位标记进行位置匹配,使得晶圆表面与形成有第一掩膜图形的待曝光区域相同或相邻的至少一个待曝光区域形成第二掩膜图形。

9、本发明一些实施例中,第一图形区域内形成有第一掩膜图形,第二图形区域内形成有第二掩膜图形,第二掩膜图形与第一掩膜图形相匹配;

10、第一次扫描曝光时,第一掩膜图形经投影透镜在晶圆表面形成按预定比例缩小的第一掩膜图形;第二次扫描曝光时,第二掩膜图形经投影透镜在晶圆表面形成按预定比例缩小的第二掩膜图形。

11、本发明一些实施例中,第一掩模版和第二掩模版拼接设置,第一掩模版的拼接端和第二掩模版的拼接端对应设置有第一定位标记和第二定位标记;

12、第一掩模版和第二掩模版拼接时,检测第一定位标记和第二定位标记之间的偏移量,基于偏移量调整第一掩模版和第二掩模版的相对位置;

13、第一次扫描曝光和第二次扫描曝光时,第一掩模版和第二掩模版先后在晶圆表面相邻的待曝光区域形成相拼接的第一掩膜图形和第二掩膜图形。

14、本发明一些实施例中,第一掩模版和第二掩模版分体设置;

15、第一次扫描曝光和第二次扫描曝光时,第一掩模版和第二掩模版先后在晶圆表面相同的待曝光区域形成相重叠的第一掩膜图形和第二掩膜图形。

16、本发明一些实施例中,第一掩膜图形为空白图形,第二掩模图形为电路图形。

17、本发明一些实施例中,待曝光区域包括多个横向排列或纵向排列的子待曝光区域;

18、第一次扫描曝光时,使用第一掩模版沿子待曝光区域的排列方向在待曝光区域内进行步进曝光,使得待曝光区域的每一子待曝光区域均形成第一掩膜图形;

19、第二次扫描曝光时,使用第二掩模版沿子待曝光区域的排列方向在待曝光区域内进行步进曝光,使得待曝光区域的每一子待曝光区域均形成第二掩膜图形。

20、本发明一些实施例中,对第二掩模版上的第二定位标记在晶圆表面的投影与晶圆表面的第一定位标记进行位置匹配的方法包括:

21、使用测量机台检测第二掩模版上的第二定位标记在晶圆表面的投影与晶圆表面的第一定位标记在x轴方向和y轴方向的偏移量,基于测得的偏移量在对掩模版进行x轴方向和y轴方向的位置偏移补偿。

22、本发明一些实施例中,第一定位标记包括第一矩形框;第二定位标记包括第二矩形框;第一定位标记和第二定位标记相匹配时,第二矩形框嵌套在第一矩形框的外部,且第二矩形框的中心点和第一矩形框的的中心点相重合。

23、本发明一些实施例中,第一掩模版和第二掩模版尺寸相同。

24、本发明一些实施例中,进行双次扫描曝光后,使用与光刻胶对应的显影液对晶圆进行显影操作,在晶圆表面的光刻胶上留下双次曝光后的掩膜图形。

25、本发明的有益效果在于:

26、1、本发明在不改变掩模版机台原有结构的基础上,通过拼接掩模版与双次曝光相配合的方式,解决了现有曝光机台中掩模版放置台的开口限制,使得现有的常规曝光机台能够曝光比26mm*33mm掩模版更大尺寸的掩模版,在晶圆表面曝光出更大尺寸的电路图形;

27、2、本发明在不改变曝光机台原有结构的基础上,通过使用两个掩模版进行重叠双次曝光的方式,解决了单次曝光掩膜图形的精度限制,在同一个晶圆上能够曝光出更高分辨率和更小特征尺寸的电路图形;

28、3、本发明通过在第一掩模版和第二掩模版上的对应位置设置相互匹配的第一定位标记和第二定位标记,使得两次曝光的图形能够拼接对准或重叠对准,解决了双次曝光图形之间的偏移问题。

技术特征:

1.一种双次曝光方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的双次曝光方法,其特征在于,所述第一图形区域内形成有第一掩膜图形,所述第二图形区域内形成有第二掩膜图形,所述第二掩膜图形与所述第一掩膜图形相匹配;

3.根据权利要求1或2所述的双次曝光方法,其特征在于,所述第一掩模版和所述第二掩模版拼接设置,所述第一掩模版的拼接端和所述第二掩模版的拼接端对应设置有第一定位标记和第二定位标记;

4.根据权利要求1或2所述的双次曝光方法,其特征在于,所述第一掩模版和所述第二掩模版分体设置;

5.根据权利要求4所述的双次曝光方法,其特征在于,所述第一掩膜图形为空白图形,所述第二掩模图形为电路图形。

6.根据权利要求1所述的双次曝光方法,其特征在于,所述待曝光区域包括多个横向排列或纵向排列的子待曝光区域;

7.根据权利要求1所述的双次曝光方法,其特征在于,对所述第二掩模版上的第二定位标记在所述晶圆表面的投影与所述晶圆表面的第一定位标记进行位置匹配的方法包括:

8.根据权利要求1所述的双次曝光方法,其特征在于,所述第一定位标记包括第一矩形框;所述第二定位标记包括第二矩形框;所述第一定位标记和所述第二定位标记相匹配时,所述第二矩形框嵌套在所述第一矩形框的外部,且所述第二矩形框的中心点和所述第一矩形框的的中心点相重合。

9.根据权利要求1所述的双次曝光方法,其特征在于,所述第一掩模版和所述第二掩模版尺寸相同。

10.根据权利要求1所述的双次曝光方法,其特征在于,进行双次扫描曝光后,使用与所述光刻胶对应的显影液对所述晶圆进行显影操作,在所述晶圆表面的光刻胶上留下双次曝光后的掩膜图形。

技术总结

本发明涉及一种双次曝光方法,包括以下步骤:提供第一掩模版和第二掩模版,两个掩模版均包括图形区域和非图形区域,且非图形区域对应设置第一定位标记和第二定位标记;使用第一掩模版对晶圆进行第一次曝光,使晶圆表面的至少一个待曝光区域内形成第一掩膜图形;使用第二掩模版对晶圆进行第二次曝光,每次曝光前均对第二定位标记与第一定位标记进行位置匹配,使晶圆表面形成与第一掩膜图形重叠或拼接的第二掩膜图形。本发明在不改变曝光机台结构的基础上,解决了掩模版放置台的开口限制以及单次曝光掩膜图形的精度限制,同时,通过定位标记的匹配解决了双次曝光图形之间的偏移问题,实现了在晶圆表面曝光出更大尺寸和更高精度的电路图形。

技术研发人员:陈呈,邱杰振,颜天才

受保护的技术使用者:物元半导体技术(青岛)有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!