一种Micro-CT探测器镀膜方法、一种掩膜

一种micro-ct探测器镀膜方法、一种掩膜

技术领域

1.本发明涉及镀膜技术领域,尤其涉及一种micro-ct探测器镀膜方法、一种掩膜。

背景技术:

2.精细金属掩模版(fine metal mask,fmm)在集成电路制造工艺流程中是必不可少的。但由于精细金属掩模版的研发周期长,并且很难在短时间内开发,无论是传统的湿法化学刻蚀与光刻工艺、激光加工工艺、亦或是通过电溶解将基板镀金制作薄板的电铸(electro-forming)工艺,都使得fmm的造价极为昂贵。

3.micro-ct探测是使用x射线进行探测,来获得微米级甚至更小尺度物体的内部细节信息,多用于医疗、生物及地质等相关行业的显微样品观测。现有micro-ct探测器的镀膜是先将多个小的探测器组放置在平面,经过显微对准后,统一进行大面积的像素化电极蒸镀工艺,再分别将各个小探测器阵列与后端电路进行倒装连接,该过程中需要使用精细金属掩膜板,因而导致现有micro-ct探测器镀膜成本较高。

4.目前主流的micro-ct的像素大小多为几十微米的数量级,由于micro-ct探测器单个探测器组的尺寸较小,不需要制备大尺寸的探测器阵列,使得micro-ct探测器的镀膜工艺不一定需要fmm。

技术实现要素:

5.本发明实施例通过提供一种micro-ct探测器镀膜方法、一种掩膜,解决了当前对micro-ct探测器进行镀膜过程存在成本高的技术问题。

6.第一方面,本发明通过本发明的一实施例,提供了一种micro-ct探测器镀膜方法,包括:将预制电子显微镜载网掩盖在micro-ct探测器单晶上,所述预制电子显微镜载网暴露有所述micro-ct探测器单晶需要镀膜的目标晶面;对所述目标晶面进行真空镀膜,以制备得到micro-ct探测器像素化电极阵列。

7.可选的,在所述将预制电子显微镜载网掩盖在micro-ct探测器单晶上之前,所述方法还包括:对所述micro-ct探测器单晶进行预处理;将所述预处理后的micro-ct探测器单晶嵌入真空镀膜设备的预制模具中。

8.可选的,所述对所述micro-ct探测器单晶进行预处理,包括:对所述micro-ct探测器单晶进行切割、打磨以及抛光,以使所述micro-ct探测器单晶需要镀膜的一面变为矩形。

9.可选的,所述将预制电子显微镜载网掩盖在micro-ct探测器单晶上,包括:利用磁吸力将所述预制电子显微镜载网吸附在所述micro-ct探测器单晶需要镀膜的一面上。

10.可选的,在所述将预制电子显微镜载网掩盖在micro-ct探测器单晶上之后,所述方法还包括:检查所述预制电子显微镜载网的方向是否与参考方向平行;若否,则将所述预制电子显微镜载网的方向对准所述参考方向。

11.可选的,在所述对所述目标晶面进行真空镀膜之后,所述方法还包括:制备所述micro-ct探测器单晶的像素化电极阵列,并建立所述像素化电极阵列与所述micro-ct探测

器单晶之间的电连接,以制备得到micro-ct探测器像素化电极阵列。

12.可选的,在所述对所述目标晶面进行真空镀膜之后,所述方法还包括:清洗真空镀膜后的micro-ct探测器单晶,并检查其镀膜的完整性。

13.第二方面,本发明通过本发明的一实施例,提供了一种用于micro-ct探测器镀膜的掩膜,所述掩膜为电子显微镜载网。

14.可选的,所述掩膜由电镀工艺制备得到,所述掩膜的材质为铜或镍。

15.可选的,所述掩膜包括多个矩形中空结构,相邻两个所述矩形中空结构之间的距离相等。

16.本发明实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

17.将预制电子显微镜载网掩盖在micro-ct探测器单晶上,由于预制电子显微镜载网暴露有micro-ct探测器单晶需要镀膜的目标晶面,因而可以直接对目标晶面进行真空镀膜,来制备得到micro-ct探测器像素化电极阵列。由于电子显微镜载网的制造成本较精细金属掩模版低,能有效降低对micro-ct探测器进行镀膜过程的成本。

附图说明

18.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

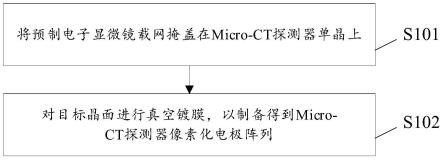

19.图1为本发明实施例中micro-ct探测器镀膜方法的流程图。

具体实施方式

20.申请人在提出本技术的过程中发现:相比较造价昂贵的fmm,透射电子显微镜载网(transmission electron microscope grid,tem grid)的制造成本要低很多。透射电子显微镜载网普遍采用电镀法工艺制成,其材质多为铜或镍,因而透射电子显微镜载网具有磁性,也就能够对透射电子显微镜载网进行精细加工以及位置调节。

21.目前,透射电子显微镜载网是透射电子显微镜测试时用于承接样品的常见耗材,透射电子显微镜载网经常与高分子、碳等材料制成载网膜的结构。现有透射电子显微镜载网一般做成直径3mm(或者更大尺寸)的多孔结构,其厚度大多在10-20μm范围内,单个孔洞的尺大多在几十微米的量级上,而这个尺寸与现有micro-ct半导体探测器的像素大小非常接近。

22.并且,micro-ct探测器由多个探测器组按照环形拼接构成整个探测器阵列,单个探测器组的尺寸较小,多为毫米或厘米级别,因而无需制备大尺寸的探测器阵列,使用小型的掩膜板就可以对单个micro-ct探测器单晶进行真空镀膜。

23.基于上述发现,本发明实施例通过提供一种micro-ct探测器镀膜方法、一种掩膜,解决了当前对micro-ct探测器进行镀膜过程存在成本高的技术问题。

24.本发明实施例提供的技术方案为解决上述技术问题,总体思路如下:

25.将预制电子显微镜载网掩盖在micro-ct探测器单晶上,由于预制电子显微镜载网暴露有micro-ct探测器单晶需要镀膜的目标晶面,因而可以直接对目标晶面进行真空镀

膜,来制备得到micro-ct探测器像素化电极阵列。

26.为了更好的理解上述技术方案,下面将结合说明书附图以及具体的实施方式对上述技术方案进行详细的说明。

27.需要说明的是,本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本发明的实施例,能够按照除了在这里图示或描述的那些以外的顺序实施。

28.第一方面,本发明通过本发明的一实施例,提供了一种micro-ct探测器镀膜方法,请参见如图1所示,该镀膜方法可以包括如下步骤s101~步骤s102:

29.步骤s101:将预制电子显微镜载网掩盖在micro-ct探测器单晶上。

30.其中,预制电子显微镜载网暴露有micro-ct探测器单晶需要镀膜的目标晶面。

31.在将预制电子显微镜载网掩盖在micro-ct探测器单晶上之前,可以对micro-ct探测器单晶进行预处理,并将预处理后的micro-ct探测器单晶嵌入真空镀膜设备的预制模具中。

32.针对如何对micro-ct探测器单晶进行预处理,具体的,可以对micro-ct探测器单晶进行切割、打磨以及抛光,以使micro-ct探测器单晶需要镀膜的一面变为矩形。

33.在具体实施过程中,真空镀膜设备的预制模具不会掩盖micro-ct探测器单晶需要镀膜的一面,预制模具能够支撑预制电子显微镜载网,并使micro-ct探测器单晶不会变形。

34.针对如何将预制电子显微镜载网掩盖在micro-ct探测器单晶上,具体的,可以利用磁吸力将预制电子显微镜载网吸附在micro-ct探测器单晶需要镀膜的一面上。

35.在具体实施过程中,预制电子显微镜载网可以使用镍电镀制备得到,因而能够利用磁力将预制电子显微镜载网吸附在micro-ct探测器单晶需要镀膜的一面上,使得预制电子显微镜载网成为后续镀膜过程的掩膜。

36.在一些实施方式中,预制电子显微镜载网的中空结构可以是正方形,且中空结构的边长可以是42微米,相邻两个中空结构之间的距离(即肋宽)可以是12微米。

37.在将预制电子显微镜载网掩盖在micro-ct探测器单晶上之后,还可以检查预制电子显微镜载网的方向是否与参考方向平行;若否,则将预制电子显微镜载网的方向对准参考方向。

38.在具体实施过程中,参考方向可以是micro-ct探测器单晶的边长方向,预制电子显微镜载网的方向可以是中空结构的排列方向。将预制电子显微镜载网的方向与参考方向平行,能够使得后续像素化的镀膜边长能够与micro-ct探测器单晶的边长方向平行,提高对micro-ct探测器单晶的利用率。

39.另外,还需要区分预制电子显微镜载网的正反面,防止因预制电子显微镜载网朝向不正确导致蒸镀阴影出现。

40.步骤s102:对目标晶面进行真空镀膜,以制备得到micro-ct探测器像素化电极阵列。

41.作为一种可选的实施方式,在对目标晶面进行真空镀膜之后,可以制备micro-ct探测器单晶的像素化电极阵列,并建立像素化电极阵列与micro-ct探测器单晶之间的电连接,以制备得到micro-ct探测器像素化电极阵列,进而制备得到镀膜后的micro-ct探测器。

42.作为一种可选的实施方式,在对目标晶面进行真空镀膜之后,还可以清洗真空镀膜后的micro-ct探测器单晶,并检查其镀膜的完整性。

43.在具体实施过程中,可以利用电子显微镜检查像素化电极边缘是否完整,像素化电极的排列是否一致。

44.第二方面,基于同一发明构思,本发明通过本发明的一实施例,提供了一种用于micro-ct探测器镀膜的掩膜,该掩膜可以是电子显微镜载网。

45.作为一种可选的实施方式,该掩膜可以由电镀工艺制备得到,且该掩膜的材质为铜或镍。

46.作为一种可选的实施方式,该掩膜可以包括多个矩形中空结构,相邻两个矩形中空结构之间的距离相等。

47.上述本发明实施例中的技术方案,至少具有如下的技术效果或优点:

48.本发明实施例使用电子显微镜载网作为镀膜过程的掩膜,由于电子显微镜载网的制造成本较精细金属掩模版低,因而能有效降低对micro-ct探测器进行镀膜过程的成本。

49.本领域内的技术人员应明白,本发明的实施例可提供为方法、系统、或计算机产品。因此,本发明可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本发明可采用在一个或多个其中包含有计算机可用代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机产品的形式。

50.本发明是参照根据本发明实施例的方法、设备(系统)、和计算机产品的流程图和/或方框图来描述的。应理解可由计算机指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

51.这些计算机指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

52.这些计算机指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

53.尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

54.显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1