拼接金刚石晶片与异质半导体的接合体及其制造方法、以及用于拼接金刚石晶片与异质半导体的接合体的拼接金刚石晶片与流程

本公开涉及拼接金刚石晶片与异质半导体的接合体及其制造方法、以及用于拼接金刚石晶片与异质半导体的接合体的拼接金刚石晶片。本技术主张基于2021年5月31日向日本技术的特愿2021-091708号的优先权,其内容引用于本文中。

背景技术:

1、gan器件等功率器件的冷却是必不可少的,但尚未开发出一种充分的冷却方法。在这种情况下,关于将具有高导热率的金刚石材料用作散热基材进行了研究讨论。

2、专利文献1记载了一种具有生长或接合于gan上的多晶金刚石层的晶片。

3、非专利文献1公开了一种将单晶金刚石基板用作散热基板的gan-hemt(高电子迁移率晶体管)。

4、现有技术文献

5、专利文献

6、专利文献1:日本特表2015-533774号公报

7、专利文献2:日本专利第4849691号公报

8、非专利文献

9、非专利文献1:s.hiza,m.fujikawa,y.takiguchi,k.nishimura,e.yagyu,t.matsumae,y.kurashima,h.takagi和m.yamamuka:extendedabstracts of the2019international conference on solid state devices and materials,467(2019).

10、非专利文献2:目黑、西林、今井,sei技术综述163,53(2003)

技术实现思路

1、发明所要解决的问题

2、由于晶界的存在,多晶金刚石的导热性一般比单晶金刚石低。当所需的导热性与单晶相同时,需要在生长条件上下功夫,但生长速度却停留在单晶的1/10以下。另外,对于生长面的平坦化而言,机械研磨等是必不可少的,但由于金刚石的研磨速度的各向异性较大,因此在多晶的情况下,与单晶相比,研磨速度显著较慢。基于以上理由,可以认为:在将多晶金刚石用作接合晶片的情况下,与单晶金刚石相比,制造成本极高。而且,在多晶的情况下,由于存在因生长气氛的不均匀性等引起的晶粒方位或粒径分布,容易产生翘曲等,在技术上很难将其降低。另外,由于上述的各向异性,通过机械研磨难以获得适于晶片接合的表面。其结果,出现了下述问题:为了对gan晶片与多晶晶片进行接合,需要较厚的中间层,而其会成为热屏障从而使器件的散热效果显著降低。

3、另一方面,就单晶金刚石基板而言,虽然其能经由极薄的中间层(<5nm)实际上与gan晶片直接接合,但英寸级尺寸的单晶金刚石晶片并不存在,因此出现了下述问题:晶片级别的贴合无法实现,成本较高。

4、本公开是鉴于上述情况而完成的,其目的在于提供一种散热特性高且可大型化的拼接金刚石晶片与异质半导体的接合体及其制造方法、以及用于拼接金刚石晶片与异质半导体的接合体的拼接金刚石晶片。

5、用于解决问题的手段

6、所谓拼接金刚石晶片,是通过气相法使金刚石晶体在排列于同一面上的多个单晶金刚石基板上生长从而将这些单晶金刚石基板接合,由此构成为大型的金刚石单晶晶片的拼接状的金刚石晶片(例如参照非专利文献2)。

7、图9表示通过专利文献2记载的方法得到的典型的拼接金刚石晶片的接合边界部附近的光学显微镜图像。在图9中,箭头所示的部分为单晶金刚石基板间的接合边界部。

8、在拼接金刚石晶片中,即使在将多个单晶金刚石基板以晶体方位彼此一致的方式配置于晶体生长装置内的情况下,接合边界部也会异常生长(多晶化),晶体方位容易呈现非均质性。在图9中,可以看出接合边界部反映出异常生长(多晶化)而与除其之外的部分显著不同。

9、图10表示拼接金刚石晶片的接合边界部附近的阴极发光映射图像。阴极发光映射图像的一边的长度为125μm。

10、在阴极发光映射图像中,不发光的区域存在晶体缺陷(非发光中心)。在阴极发光映射图像中,可以看出复杂结构的非发光中心集中在接合边界部附近。

11、拼接金刚石晶片具有接近单晶金刚石的质量,同时,相比于单晶金刚石,比较容易大面积化。因此,如果能将拼接金刚石晶片用作散热基材,就能解决上述的单晶金刚石基板所存在的问题。但是,由于构成拼接金刚石晶片的单晶金刚石基板间的接合边界相当于多晶金刚石的晶界,因此本领域技术人员认为其与多晶金刚石相同,不能与gan晶片直接接合。此外,如图9及图10所示,接合边界部还存在缺陷或应变集中这样的拼接金刚石晶片所特有的问题,因此对于本领域技术人员来说,能将拼接金刚石晶片与gan晶片直接接合是无法想象的。

12、本发明人经过深入研究之后,实现了拼接金刚石晶片与gan晶片的直接接合,并完成了本公开。

13、为了解决上述问题,本公开提供了以下手段。

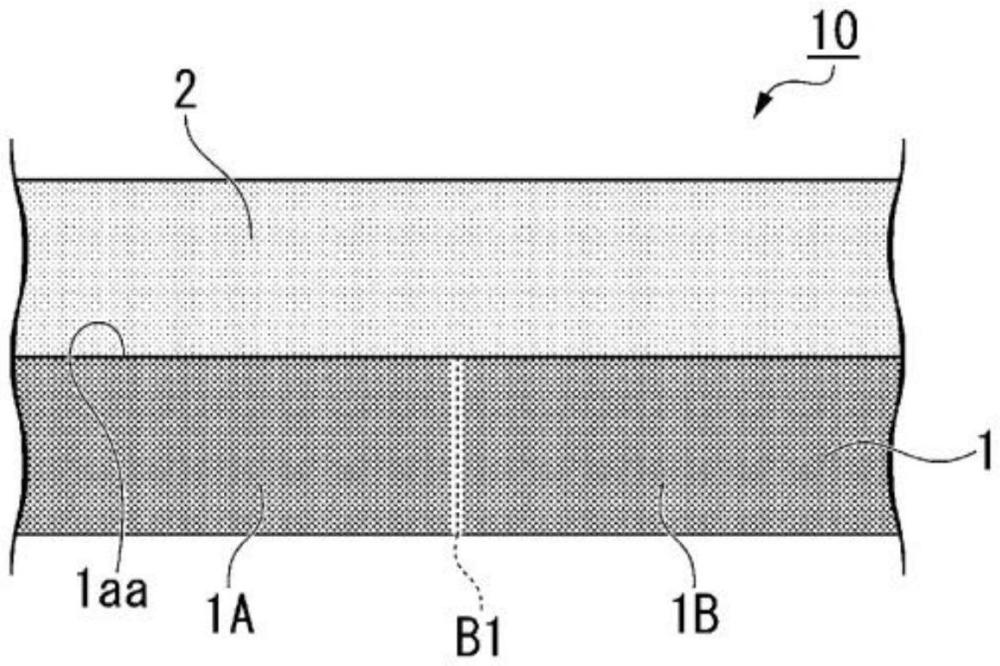

14、本公开的第一方面涉及一种拼接金刚石晶片与异质半导体的接合体,其由具有多个单晶金刚石基板间的接合边界部的拼接金刚石晶片与异质半导体接合而成,其中,所述拼接金刚石晶片与所述异质半导体的接合面上的最大起伏差为10nm以下。

15、根据上述方面所涉及的拼接金刚石晶片与异质半导体的接合体,其中,所述异质半导体可以是选自由氮化镓、氧化镓、硅及碳化硅组成的组中的一种。

16、根据上述方面所涉及的拼接金刚石晶片与异质半导体的接合体,其中,所述接合体可以由所述拼接金刚石晶片与所述异质半导体直接接合而成。

17、根据上述方面所涉及的拼接金刚石晶片与异质半导体的接合体,其中,所述接合体可以由所述拼接金刚石晶片与所述异质半导体经由中间层接合而成。

18、本发明的第二方面涉及一种拼接金刚石晶片与异质半导体的接合体的制造方法,所述制造方法具有如下工序:筛选拼接金刚石晶片,该拼接金刚石晶片具有多个单晶金刚石基板间的接合边界部,且所述拼接金刚石晶片与所述异质半导体的接合面上的最大起伏差为10nm以下。

19、本发明的第三方面涉及一种拼接金刚石晶片与异质半导体的接合体的制造方法,所述制造方法具有如下工序:准备拼接金刚石晶片,该拼接金刚石晶片具有多个单晶金刚石基板间的接合边界部;以及对所述拼接金刚石晶片的表面进行研磨,直到所述接合边界部上的最大起伏差为10nm以下。

20、根据上述方面所涉及的拼接金刚石晶片与异质半导体的接合体的制造方法,所述制造方法具有如下工序:通过在生长基板的主面上使异质半导体层外延生长来制备外延基板;经由粘接层将所述外延基板贴合到支撑基板上;除去所述生长基板,使所述异质半导体层露出;将所述异质半导体层与所述拼接金刚石晶片的研磨面接合;以及除去所述粘接层,得到拼接金刚石晶片与异质半导体的接合体。

21、本发明的第四方面涉及一种用于拼接金刚石晶片与异质半导体的接合体的拼接金刚石晶片,该接合体由具有多个单晶金刚石基板间的接合边界部的拼接金刚石晶片与异质半导体接合而成,所述拼接金刚石晶片与所述异质半导体的接合面上的最大起伏差为10nm以下。

22、发明的效果

23、根据本公开所涉及的拼接金刚石晶片与异质半导体的接合体,能够提供散热特性高且可大型化的拼接金刚石晶片与异质半导体的接合体。

- 还没有人留言评论。精彩留言会获得点赞!