半导体装置的制作方法

[0001]

本发明涉及一种能够对向负载的供电进行开关的装置,特别是涉及具备在接地端子脱落的情况下能够向外部发出通知的功能的半导体装置。

背景技术:

[0002]

在汽车大多搭载有对马达等负载进行开关控制的半导体装置。作为这样的车载用的半导体装置,使用将向负载供电的功率半导体开关及其控制电路集成在同一芯片上而成的ips(intelligent power switch:智能功率开关)。通常,在这样的ips中,作为功率半导体开关,使用单位面积的导通电阻的值小的n沟道的mosfet(metal-oxide-semiconductor field-effect transistor:金属氧化物半导体场效应晶体管)。

[0003]

图9是表示现有的ips的构成例的图,图10是表示现有的ips的动作的逻辑表。应予说明,在图9的说明中,端子名及该端子的电压、信号等有时使用相同的符号。

[0004]

如图9所示,现有的ips100具备主mosfet110、逻辑电路120、驱动电路130,并作为状态检测功能,具备负载开路检测电路140和状态通知用的n沟道的mosfet150。ips100还具有in端子、vcc端子、out端子、gnd端子、st端子。

[0005]

ips100的in端子与逻辑电路120的输入端子连接,逻辑电路120的输出端子与驱动电路130的输入端子连接,驱动电路130的输出端子与主mosfet110的栅极端子连接。主mosfet110的漏极端子、逻辑电路120的电源端子及驱动电路130的电源端子连接于vcc端子,vcc端子连接于提供电压vcc的电池160的正极端子,电池160的负极端子连接于汽车的底盘。主mosfet110的源极端子连接于out端子,out端子连接于负载170的一个端子,负载170的另一端子连接于汽车的底盘。逻辑电路120的低电位侧端子及驱动电路130的低电位侧端子连接于gnd端子。

[0006]

out端子还连接于负载开路检测电路140的输入端子,负载开路检测电路140的输出端子连接于逻辑电路120的输出负载开路检测信号lo的端子。负载开路检测电路140的电源端子连接于vcc端子,低电位侧端子连接于gnd端子。逻辑电路120还连接于mosfet150的栅极端子,mosfet150的漏极端子连接于st端子,mosfet150的源极端子连接于gnd端子。

[0007]

在此,ips100的in端子及st端子连接于控制用的微型计算机,in端子被输入对主mosfet110进行导通、关断控制的信号。在此,作为导通控制的信号,例如,被输入5v的高(h)电平的逻辑信号,作为关断控制的信号,被输入0v的低(l)电平的逻辑信号。st端子还经由外部电阻180连接于例如5v的外部电源190,被上拉至5v的电压。

[0008]

在该ips100正常动作时,如图10所示,如果向in端子输入l电平的逻辑输入信号,则因为主mosfet110被关断控制,所以out端子为l电平。此时,逻辑电路120将h电平的信号供给至mosfet150的栅极端子,将mosfet150导通控制,因此st端子为l电平。

[0009]

在该ips100正常动作时,如果向in端子输入h电平的逻辑输入信号,则主mosfet110被导通控制而向out端子施加电压vcc,因此out端子变为h电平。此时,逻辑电路120将l电平的信号供给到mosfet150的栅极端子,将mosfet150关断控制,因此st端子变为h

电平。

[0010]

接着,在向ips100的in端子输入l电平的逻辑输入信号时,如果负载开路检测电路140检测到负载开路,则out端子变为h电平。即,如果变为负载开路,则因为out端子的电位不会被负载170拉低,所以out端子变为h电平。此时,逻辑电路120将l电平的信号供给至mosfet150的栅极端子,将mosfet150关断控制,因此st端子变为h电平。在主mosfet110被关断控制时,如果检测到st端子的h电平,则微型计算机能够判断出负载170处于开路状态。

[0011]

应予说明,在该ips100中,虽然负载开路检测电路140检测out端子与负载开路的状态,但是在gnd端子,也可能因焊料接合部剥离等原因导致gnd端子被断开。在该gnd端子开路的情况下,以往,与输入到in端子的逻辑电平无关,而将主功率半导体开关进行关断控制(例如,参照专利文献1)。

[0012]

但是,在近年来的ips中,对于gnd端子的开路异常,也要求向微型计算机发出通知的功能。如果ips能够向微型计算机通知gnd端子的开路状态,则微型计算机能够事先知道ips的异常,并且能够采取适当的措施。

[0013]

现有技术文献

[0014]

专利文献

[0015]

专利文献1:日本特开2009-10477号公报

技术实现要素:

[0016]

技术问题

[0017]

在现有的ips中,仅在正常动作时向in端子输入h电平的逻辑输入信号的情况下,以及在向in端子输入l电平的逻辑输入信号时检测到负载开路的情况下,在st端子输出的信号会变为h电平。因此,如果在gnd端子开路时在st端子输出h电平的信号,则存在如下不良情况:在微型计算机侧,不能区别h电平的信号是因负载开路而引起还是因gnd端子开路而引起。

[0018]

本发明是鉴于上述情况而做出的,其目的在于,提供一种能够区别gnd端子的开路与负载开路并将其输出的半导体装置。

[0019]

技术方案

[0020]

在本发明中,为了解决上述课题,在1个方案中提供一种半导体装置,其具备:功率半导体开关,其连接在电源端子与输出端子之间;逻辑电路,其根据输入到输入端子的信号而生成使功率半导体开关导通、关断的逻辑输出信号;接地端子开路检测电路,其基于接地端子的电位的上升而检测接地端子的开路状态;状态输出端子,其在接地端子开路检测电路检测到接地端子的开路状态时输出检测信号。

[0021]

发明效果

[0022]

在上述构成的半导体装置中,接地端子开路检测电路在检测到接地端子的开路状态时能够向状态输出端子输出检测信号。由此,微型计算机能够与其他检测信号相区别地进行识别。

附图说明

[0023]

图1是表示第一实施方式的ips的构成例的图。

[0024]

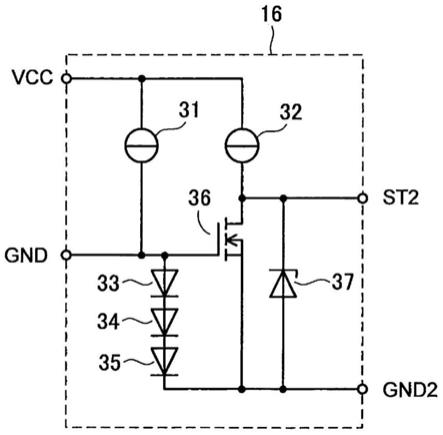

图2是表示第一实施方式的ips中的接地端子开路检测电路的构成例的电路图。

[0025]

图3是表示第一实施方式的ips的动作的逻辑表。

[0026]

图4是表示第二实施方式的ips中的接地端子开路检测电路的构成例的电路图。

[0027]

图5是表示第二实施方式的ips的动作的逻辑表。

[0028]

图6是表示第三实施方式的ips的构成例的图。

[0029]

图7是表示第三实施方式的ips中的接地端子开路检测电路的构成例的电路图。

[0030]

图8是表示第三实施方式的ips的动作的逻辑表。

[0031]

图9是表示现有的ips的构成例的图。

[0032]

图10是表示现有的ips的动作的逻辑表。

[0033]

符号说明

[0034]

10,10a ips(半导体装置)

[0035]

11 主mosfet

[0036]

12 逻辑电路

[0037]

13 驱动电路

[0038]

14 负载开路检测电路

[0039]

15 mosfet

[0040]

16、16a、16b 接地端子开路检测电路

[0041]

21 电池

[0042]

22 负载

[0043]

23 外部电阻

[0044]

24 外部电源

[0045]

25 外部电阻

[0046]

26 外部电源

[0047]

31 恒流电路(上拉电路)

[0048]

32 恒流电路

[0049]

33、34、35 二极管

[0050]

36 mosfet

[0051]

37 齐纳二极管

[0052]

38 mosfet

[0053]

39 二极管(防回流二极管)

[0054]

40 电阻(保护电阻)

具体实施方式

[0055]

以下,参照附图,以适用于对汽车用电气设备进行导通、关断的ips的情况为例,对本发明的实施方式的半导体装置进行详细说明。应予说明,在所有附图中,以同一符号表示的构成要素表示同一构成要素。另外,在以下说明中,端子名及该端子的电压、信号等有可能使用相同的符号。

[0056]

图1是表示第一实施方式的ips的构成例的图,图2是表示第一实施方式的ips中的接地端子开路检测电路的构成例的电路图,图3是表示第一实施方式的ips的动作的逻辑

表。

[0057]

如图1所示,ips10具有作为功率半导体开关的主mosfet11、逻辑电路12、驱动电路13,并作为状态检测功能,具备负载开路检测电路14、mosfet15及接地端子开路检测电路16。ips10还具有in端子、vcc端子、out端子、gnd端子、st端子、st2端子、gnd2端子。

[0058]

在ips10中,in端子连接于逻辑电路12的输入端子,逻辑电路12的输出端子连接于驱动电路13的输入端子,驱动电路13的输出端子连接于主mosfet11的栅极端子。主mosfet11的漏极端子、逻辑电路12的电源端子及驱动电路13的电源端子连接于vcc端子,vcc端子连接于提供电压vcc的电池21的正极端子,电池21的负极端子连接于汽车的底盘。主mosfet11的源极端子连接于out端子,out端子连接于负载22的一个端子,负载22的另一端子连接于汽车的底盘。逻辑电路12的低电位侧端子及驱动电路13的低电位侧端子连接于gnd端子。

[0059]

out端子还连接于负载开路检测电路14的输入端子,负载开路检测电路14的输出端子连接于逻辑电路12的输出负载开路检测信号lo的端子。另外,负载开路检测电路14的电源端子连接于vcc端子,低电位侧端子连接于gnd端子。逻辑电路12还连接于状态通知用的n沟道的mosfet15的栅极端子,mosfet15的漏极端子连接于st端子,mosfet15的源极端子连接于gnd端子。

[0060]

vcc端子还连接于接地端子开路检测电路16的电源端子,接地端子开路检测电路16的输入端子连接于gnd端子,接地端子开路检测电路16的输出端子连接于st2端子和gnd2端子。st2端子是状态输出端子,gnd2端子是第2接地端子。

[0061]

在此,ips10的in端子、st端子、st2端子及gnd2端子连接于控制用的微型计算机,从微型计算机向in端子输入将主mosfet11进行导通、关断控制的l电平或h电平的逻辑输入信号。st端子还经由外部电阻23连接于外部电源24。外部电源24的电压是例如5v,因此,st端子以被上拉到5v的电压的状态而被使用。应予说明,gnd2端子是相对于gnd端子另行设置的第2接地端子,连接于微型计算机的gnd端子(电池21的负极端子)。

[0062]

如图2所示,接地端子开路检测电路16具有恒流电路31、32、二极管33、34、35、mosfet36、齐纳二极管37。mosfet36是接地端子开路检测用的开关元件,是n沟道的mosfet。

[0063]

恒流电路31的一个端子连接于电压vcc的线,另一端子连接于gnd端子、二极管33的阳极端子及mosfet36的栅极端子。二极管33的阴极端子连接于二极管34的阳极端子,二极管34的阴极端子连接于二极管35的阳极端子,二极管35的阴极端子连接于gnd2端子。

[0064]

恒流电路32的一个端子连接于电压vcc的线,另一端子连接于mosfet36的漏极端子和st2端子,mosfet36的源极端子连接于gnd2端子。

[0065]

mosfet36以与其并联的方式连接有齐纳二极管37。即,mosfet36的漏极端子连接于齐纳二极管37的阴极端子,mosfet36的源极端子连接于齐纳二极管37的阳极端子。

[0066]

恒流电路31是在gnd端子被断开时,将gnd端子的电位上拉的上拉电路。因此,如果有作为ips10中的电路且能够将gnd端子的电位上拉那样的内部电路,则能够利用该内部电路来代替恒流电路31。

[0067]

二极管33、34、35是用于保护mosfet36不因gnd端子开路时gnd端子的电压变得不安定而使mosfet36的栅极-源极间电压异常变高而损坏的栅极保护用二极管。二极管33、34、35的正向电压的和被设定为比使mosfet36导通的阈值电压大的值,例如被设定为2v左

右。

[0068]

齐纳二极管37是用于根据电压vcc来生成作为gnd端子开路的检测信号的5v的逻辑信号的元件。因此,齐纳二极管37使用击穿电压为5v的齐纳二极管。

[0069]

根据具备以上结构的接地端子开路检测电路16的ips10,如图3所示,在ips10正常动作时,如果向in端子输入l电平的逻辑输入信号,则因为主mosfet11被关断控制,所以out端子为l电平。此时,逻辑电路12将h电平的信号提供给mosfet15的栅极端子,对mosfet15进行导通控制,因此,st端子为l电平。针对接地端子开路检测电路16而言,gnd端子的电位为0v,gnd端子开路检测用的mosfet36被关断控制,因此,st2端子为h电平。

[0070]

在该ips10正常动作时,如果向in端子输入h电平的逻辑输入信号,则主mosfet11被导通控制而向out端子施加电压vcc,因此,out端子变为h电平。此时,逻辑电路12将l电平的信号提供给mosfet15的栅极端子,对mosfet15进行关断控制,因此,st端子变为h电平。针对接地端子开路检测电路16而言,gnd端子的电位为0v,mosfet36被关断控制,因此,st2端子依然为h电平。

[0071]

接着,在向ips10的in端子输入有l电平的逻辑输入信号时,如果负载开路检测电路14检测到负载开路,则out端子由于没有被负载22拉低电位,所以变为h电平。此时,逻辑电路12将l电平的信号提供给mosfet15的栅极端子,将mosfet15关断控制,因此,st端子变为h电平。针对接地端子开路检测电路16而言,gnd端子的电位为0v,mosfet36被关断控制,因此,st2端子依然为h电平。

[0072]

接着,在gnd端子被开路时,在接地端子开路检测电路16中,因为mosfet36的栅极端子的电位被恒流电路31上拉,所以mosfet36被导通控制。因此,因为齐纳二极管37被mosfet36短路,所以st2端子变为l电平。此时,逻辑电路12因gnd端子悬空而无法正常动作,因此与in端子的信号的电平无关,使主mosfet11处于关断状态,而out端子变为l电平。另外,逻辑电路12使mosfet15的栅极端子为l电平而使mosfet15处于关断状态,所以st端子被外部电源24上拉而变为h电平。在该情况下,虽然st端子是与负载开路检出时相同的h电平,但是st2端子在检测到负载开路时为h电平,在检测到gnd端子开路时为l电平,因此,微型计算机能够将gnd端子开路与负载开路相区别地进行识别。

[0073]

图4是表示第二实施方式的ips中的接地端子开路检测电路的构成例的电路图,图5是表示第二实施方式的ips的动作的逻辑表。在第二实施方式中,ips的结构与图1所示的结构相同。另外,在图4中,对与图2所示的构成要素相同或者等价的构成要素标注相同的符号而省略其详细说明。

[0074]

第一实施方式的ips10仅检测gnd端子的开路,相对于此,该第二实施方式的ips还能够检测gnd2端子的开路。

[0075]

如图4所示,第二实施方式的接地端子开路检测电路16a具有恒流电路31、32、二极管33、34、35、mosfet36、齐纳二极管37、mosfet38。mosfet38是状态通知用的n沟道的mosfet。

[0076]

在该接地端子开路检测电路16a中,恒流电路32的另一端子、mosfet36的漏极端子及齐纳二极管37的阴极端子的连接部连接于mosfet38的栅极端子。mosfet38的漏极端子连接于st2端子,mosfet38的源极端子连接于gnd2端子。

[0077]

该接地端子开路检测电路16a的st2端子与st端子的情况同样地,在外部连接上拉

用的电源而进行使用。即,st2端子连接于外部电阻25的一个端子,外部电阻25的另一端子连接于外部电源26的正极端子,外部电源26的负极端子连接于微型计算机的gnd端子。外部电源26的电压是例如5v,因此,st2端子被上拉至5v的电压。

[0078]

根据具备以上结构的接地端子开路检测电路16a的ips,如图5所示,在ips正常动作时,如果向in端子输入l电平的逻辑输入信号,则out端子为l电平,st端子为l电平。针对接地端子开路检测电路16a而言,gnd端子的电位为0v,mosfet36被关断控制,并且mosfet38被导通控制,因此,st2端子为l电平。

[0079]

在ips正常动作时,如果向in端子输入h电平的逻辑输入信号,则out端子为h电平,st端子为h电平。针对接地端子开路检测电路16a而言,gnd端子的电位为0v,mosfet36被关断控制,并且mosfet38被导通控制,因此,st2端子依然为l电平。

[0080]

接着,在向ips的in端子输入有l电平的逻辑输入信号时,如果负载开路检测电路14检测到负载开路,则out端子为h电平,st端子为h电平。针对接地端子开路检测电路16a而言,gnd端子的电位为0v,mosfet36被关断控制,并且mosfet38被导通控制,因此,st2端子依然为l电平。

[0081]

接着,在gnd端子被开路时,在接地端子开路检测电路16a中,因为mosfet36的栅极端子的电位被恒流电路31上拉,所以mosfet36被导通控制,并且mosfet38被关断控制。因此,st2端子由于被外部电源26上拉,所以变为h电平。此时,逻辑电路12因gnd端子悬空而无法正常动作,因此,与in端子的信号的电平无关,使主mosfet11处于关断状态,out端子变为l电平。另外,逻辑电路12将mosfet15的栅极端子设为l电平而使mosfet15处于关断状态,因此,st端子被外部电源24上拉而变为h电平。虽然与检测到负载打开时同样地,gnd端子被开路时的st端子变为h电平,但是在检测到负载开路时,st2端子为l电平,在检测到gnd端子开路时,st2端子为h电平,因此,微型计算机能够将gnd端子开路与负载开路相区别地进行识别。

[0082]

接着,对gnd端子正常地连接而gnd2端子被开路时进行说明。此时,因为gnd端子正常地连接,所以in端子、st端子及out端子的逻辑与正常动作时相同。但是,如果gnd2端子被开路,则与mosfet38的导通、关断控制无关,st2端子被外部电源26上拉而变为h电平。在此,在ips正常动作且in端子为h电平时、以及in端子为l电平且负载开路检测电路14检测到负载开路时,st端子和out端子为h电平,与gnd2端子开路时相同。但是,在ips正常动作时、以及in端子为l电平且负载开路检测电路14检测到负载开路时,st2端子为l电平,相对于此,在gnd2端子开路时,st2端子为h电平。因此,微型计算机能够将gnd2端子的开路与负载开路相区别而进行识别。

[0083]

图6是表示第三实施方式的ips的构成例的图,图7是表示第三实施方式的ips中的接地端子开路检测电路的构成例的电路图,图8是表示第三实施方式的ips的动作的逻辑表。应予说明,在图6及图7中,对与图1及图2所示的构成要素相同或等价的构成要素标注相同的符号而省略其详细说明。

[0084]

第一实施方式的ips10和第二实施方式的ips是基于gnd2端子的电位来进行接地端子开路检测,相对于此,该第三实施方式的ips10a基于out端子的电位来进行接地端子开路检测。

[0085]

如图6所示,第三实施方式的ips10a具备主mosfet11、逻辑电路12、驱动电路13,并

作为状态检测功能,具备负载开路检测电路14、mosfet15、接地端子开路检测电路16b。ips10a还具有in端子、vcc端子、out端子、gnd端子、st端子、st2端子。

[0086]

在此,接地端子开路检测电路16b的电源端子连接于vcc端子,输入端子连接于gnd端子,输出端子连接于st2端子,接地侧端子连接于out端子。

[0087]

控制用的微型计算机连接于in端子、st端子及st2端子,将以gnd端子的电位为基准的逻辑输入信号提供给in端子,并从st端子获取以gnd端子的电位为基准的检测信号,从st2端子获取以out端子的电位为基准的检测信号。

[0088]

如图7所示,接地端子开路检测电路16b具有恒流电路31、32、二极管33、34、35、mosfet36、齐纳二极管37、二极管39、电阻40。在此,在主mosfet11被导通控制时,向out端子输出作为电池21的电压的13v,因此,二极管39是用于防止检测接地端子的开路的电路不受out端子的高电压影响的防回流用的二极管。电阻40是用于限制从恒流电路32经由齐纳二极管37及二极管39而向out端子流动的电流的保护电阻。

[0089]

根据具备以上构成的接地端子开路检测电路16b的ips10a,如图8所示,在ips10a正常动作时,如果向in端子输入l电平的逻辑输入信号,则因为主mosfet11被关断控制,所以out端子为l电平。此时,逻辑电路12将h电平的信号提供给mosfet15的栅极端子,将mosfet15导通控制,因此st端子为l电平。针对接地端子开路检测电路16b而言,gnd端子的电位为0v,mosfet36被关断控制,因此,st2端子为h电平。应予说明,因为out端子为l电平,所以此时的st2端子的h电平是比out端子的电位高出齐纳二极管37的击穿电压、二极管39的正向电压及电阻40的电压降之和的电压的电压(≈5v)。

[0090]

在ips10a正常动作时,如果向in端子输入h电平的逻辑输入信号,则主mosfet11被导通控制而向out端子施加电压vcc,因此,out端子变为h电平。此时,逻辑电路12将l电平的信号提供给mosfet15的栅极端子,将mosfet15关断控制,因此,st端子变为h电平。针对接地端子开路检测电路16b而言,gnd端子的电位为0v,mosfet36被关断控制,并因为out端子输出电压vcc,所以st2端子为h电平。因为out端子的电压为电压vcc,所以此时的st2端子的h电平等于电压vcc(≈13v)。

[0091]

接着,在向ips10a的in端子输入有l电平的逻辑输入信号时,如果负载开路检测电路14检测到负载开路,则out端子因为没有被负载22拉低电位,所以变为h电平。此时,逻辑电路12将l电平的信号提供给mosfet15的栅极端子,将mosfet15关断控制,因此,st端子变为h电平。针对接地端子开路检测电路16b而言,因为gnd端子的电位为0v,mosfet36被关断控制,所以st2端子依然为h电平(≈13v)。

[0092]

接着,在gnd端子开路时,逻辑电路12因为gnd端子悬空而无法正常动作,所以与in端子的信号的电平无关,使主mosfet11处于关断状态,out端子变为l电平(=0v)。在接地端子开路检测电路16b中,因为mosfet36的栅极端子的电位被恒流电路31上拉,所以mosfet36被导通控制。因此,因为齐纳二极管37被mosfet36短路,所以st2端子变为l电平。在out端子被设为l电平(=0v)时,虽然在st2端子输出二极管39的正向电压与由恒流电路32而产生的电阻40的电压降之和的电压,但是由于该电压是接近0v的值,所以该st2端子是l电平。在检测到gnd端子开路的情况下,st端子与检测到负载开路时同样为h电平,但是,st2端子在检测到负载开路时为h电平,在检测到gnd端子开路时为l电平,因此,微型计算机能够将gnd端子开路与负载开路相区别而识别。

[0093]

以上,对优选实施方式进行了说明,但是不言而喻,本发明不限于该特定的实施方式,在不脱离本发明的精神的范围内,能够进行各种变化变形。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1