用于集成电路中的电压检测的电路和方法与流程

1.本公开涉及电子电路,并且更特别地,涉及用于集成电路中的电压检测的电路和方法。

背景技术:

2.黑客(hacker)可以通过降低提供到集成电路的供应电压以创建电压毛刺(glitch)来尝试集成电路的电压窜改(tampering)。减少的供应电压可能引起集成电路中的电路违反定时(timing)要求,例如,如果由减少的供应电压引起的逻辑减慢(slow down)大于时钟信号的频率的减少,则引起定时故障。如果安全功能响应于电压窜改而失败,则安全逻辑可能被损害(compromise),潜在地允许从集成电路的安全区域窃取内容。

附图说明

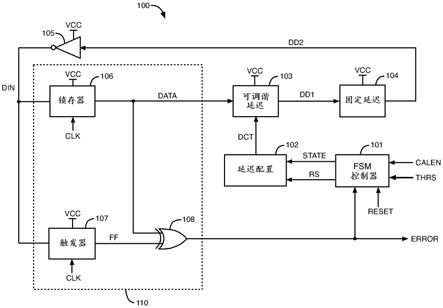

3.图1示出了根据实施例的电压攻击检测电路的示例。

4.图2示出了根据实施例的图1的错误检测时序(eds:error detection sequential)电路的进一步细节。

5.图3是示出根据实施例的图1的电压攻击检测电路在错误检测模式期间可以执行的操作的示例的流程图。

6.图4是示出根据实施例的图1的有限状态机(fsm)控制器电路中的fsm的状态以及这些状态之间的进展的状态图。

7.图5a是示出根据实施例的由图1的电压攻击检测电路生成的各种信号的波形的示例的定时图。

8.图5b示出了根据实施例的在错误检测模式中供应电压可以如何相对于上阈值电压uth和下阈值电压lth变化的示例。

9.图6示出了根据实施例的图1的可调谐(tunable)延迟电路的示例。

10.图7示出了根据实施例的图6的可调谐延迟电路中的延迟单元电路的示例。

11.图8示出了根据实施例的包括电压攻击检测电路的集成电路(ic)管芯的示例的平面图的俯视图。

具体实施方式

12.根据一些实施例,可以使用可调谐延迟电路、错误检测时序电路和控制电路(其从与被监视和保护的逻辑电路相同的供应电压操作)来检测集成电路中的电压攻击。可调谐延迟电路延迟错误检测时序电路的输出信号以生成延迟信号(delayed signal)。可调谐延迟电路接收供应电压。控制电路响应于使能信号而引起对由可调谐延迟电路提供到延迟信号的延迟的第一调整。所述错误检测时序电路响应于延迟信号相对于时钟信号的定时的改变而在错误信号中生成错误的指示,所述定时的改变由提供到延迟信号的延迟中的第一调整中的至少一个引起。控制电路响应于错误信号中的错误的指示并且基于由控制输入指示

的回归值而引起对由可调谐延迟电路提供到延迟信号的延迟的第二调整。在对延迟的第二调整之后,当供应电压已经达到阈值电压时,错误检测时序电路在错误信号中生成攻击指示。作为示例,可以通过从标称供应电压添加或减去基于控制输入确定的回归电压来计算阈值电压。

13.图1示出了根据实施例的电压攻击检测电路100的示例。图1的电压攻击检测电路100包括自校准可调谐复制电路(sc-trc),如下面将进一步详细描述的。如图(fig)1中示出的,电压攻击检测电路100包括有限状态机(fsm)控制器电路101、延迟配置电路102、可调谐延迟电路103、固定延迟电路104、反相器电路105、锁存器(latch)电路106、触发器(flip-flop)电路107和异或(xor)逻辑门电路108。锁存器电路106、触发器电路107和异或逻辑门电路108是错误检测时序(eds)电路110的一部分。

14.图2示出了根据实施例的图1的错误检测时序(eds)电路110的进一步细节。如图2中示出的,eds电路110包括主锁存器(master latch)电路201、从锁存器(slave latch)电路202、与非(nand)逻辑门电路203、触发器电路107和异或逻辑门电路108。图1-2中示出的电路可以在任何类型的集成电路(ic)(例如可编程逻辑ic、微处理器ic、图形处理单元(gpu)ic或专用ic)中提供。作为不旨在是限制性的具体示例,可以使用可重新配置的现场可编程门阵列(fpga)中的未使用的查找表基元(primitive)以创建动态的且机会性的资源感知安全传感器来构建电路100。

15.fsm控制器电路101和延迟配置电路102作为控制可调谐延迟电路103的可调整延迟的延迟控制电路起作用,如下面详细描述的。如图1中示出的,复位(reset)信号reset、校准使能信号calen和阈值回归控制信号thrs被提供到有限状态机(fsm)控制器电路101的输入。来自异或逻辑门电路108的输出的错误信号error被提供到fsm控制器电路101的附加输入。

16.fsm控制器电路101生成指示有限状态机(fsm)控制器电路101中的fsm的当前状态的输出信号state。fsm控制器电路101基于提供到fsm控制器电路101的输入信号来调整fsm的当前状态,如下面相对于图3进一步详细描述的。state信号被提供到延迟配置电路102的输入。延迟配置电路102部分地基于由state信号指示的fsm的状态来生成延迟码调谐(tuning)信号dct。延迟码调谐信号dct可以包括一个或多个信号(位)。延迟配置电路102可以包括编码器,所述编码器基于由state信号指示的状态来生成编码的延迟码调谐信号dct。作为不旨在是限制性的具体示例,编码器可以将延迟码调谐信号dct编码为二进制码、温度计码、格雷码或独热码。

17.可调谐延迟电路103、固定延迟电路104、反相器105和锁存器106在回路(loop)中耦合在一起以形成时钟除二(divide by two)电路,现在详细描述所述时钟除二电路。延迟码调谐信号dct被提供以控制可调谐延迟电路103的输入。可调谐延迟电路103是可调整延迟电路。可调谐延迟电路103延迟数字输入信号data以生成延迟数字输出信号(delayed digital output signal)dd1。可调谐延迟电路103提供到延迟输出信号(delayed output signal)dd1的相对于输入信号data的延迟基于延迟码调谐信号dct的值来设置。可调谐延迟电路103基于延迟码调谐信号dct的值的改变来调整提供到延迟信号dd1的相对于信号data的延迟。供应电压vcc被提供到可调谐延迟电路103中的延迟单元电路中的每个。可调谐延迟电路103中的电路由供应电压vcc供电。

18.可调谐延迟电路103可以例如是复制电路,其复制相同集成电路(ic)中的某一其它部分中的延迟。可调谐延迟电路103可以例如复制ic中的数据路径中的延迟,并且物理上接近所述数据路径。根据更具体的示例,由延迟电路103复制的数据路径可以是正由电压攻击检测电路100监视的逻辑电路中的关键定时路径。包括数据路径的逻辑电路接收与电压攻击检测电路100相同的供应电压vcc。可调谐延迟电路103可以例如通过包含以与数据路径相同的顺序连接的相同类型的逻辑门,或通过使用被选择用于复制数据路径的延迟的不同类型的逻辑门,来复制数据路径中的延迟。

19.可调谐延迟电路103的延迟输出信号dd1被提供到固定延迟电路104的输入。固定延迟电路104延迟所述延迟信号dd1以生成第二延迟数字输出信号dd2。固定延迟电路104提供到延迟输出信号dd2的相对于延迟输入信号dd1的延迟基于控制输入而不是可调整的。然而,固定延迟电路104提供到延迟输出信号dd2的相对于延迟输入信号dd1的延迟可以基于集成电路的工艺、电压和温度(pvt)变化而变化。还将供应电压vcc提供到固定延迟电路104中的延迟电路中的每个。

20.延迟输出信号dd2被提供到反相器电路105的输入。反相器电路105将信号dd2反相以生成反相的数字输出信号din。反相器电路105引起信号din的逻辑状态是信号dd2的逻辑状态的逻辑反相。信号din被提供到触发器电路107和锁存器电路106的数据输入,如图1中示出的。锁存器106是异步双稳态多谐振荡器电路。锁存器电路106引起信号din的当前逻辑状态作为数字信号data传播到其输出,同时输入时钟信号clk处于第一逻辑状态。信号data被提供到可调谐延迟电路103的输入。由反相器105提供到信号din的反相引起信号din、data、dd1和dd2在时钟除二电路中在二进制逻辑状态之间连续振荡。因此,信号din、data、dd1和dd2是周期性信号。锁存器106可以作为时钟分频器电路起作用。锁存器106可以例如引起信号dd2具有时钟信号clk的频率的一半,使得锁存器电路106作为时钟除二电路起作用。

21.参考图2,mode信号和时钟信号clk被提供到与非逻辑门电路203的输入。与非逻辑门电路203对时钟信号clk和mode信号的逻辑状态执行与非布尔逻辑功能,以生成提供到主锁存器201的时钟输入的输出时钟信号clkm的逻辑状态。时钟信号clk还被提供到从锁存器202和触发器107的时钟输入。在电路100的错误检测模式期间,mode信号被设置成逻辑低状态(即mode=0),以引起主锁存器201对信号din透明。因此,当mode信号处于逻辑低状态时,与非逻辑门203引起时钟信号clkm保持处于逻辑高状态。当时钟信号clkm在错误检测模式期间保持处于逻辑高状态时(即,当mode信号为低时),主锁存器201连续地引起信号din的当前逻辑状态作为信号dsl传播到从锁存器202的数据输入。在正常的主从模式中,mode信号处于逻辑高状态(即mode=1),并且与非逻辑门203提供时钟信号clk到时钟信号clkm的反相逻辑转换(transition)。

22.当输入时钟信号clk处于第一逻辑状态(例如,逻辑高状态)时,从锁存器电路202引起主锁存器201的输出信号dsl的当前逻辑状态作为数字信号data传播到其输出。当时钟信号clk处于第二逻辑状态(例如,逻辑低状态)时,从锁存器电路202防止信号dsl的当前逻辑状态作为信号data传播到其输出。

23.触发器电路107是同步双稳态多谐振荡器电路。触发器电路107捕获信号din的逻辑状态,并仅在时钟信号clk中在预定义方向上发生(occur)的每个逻辑状态转换上将所捕

获的信号din的逻辑状态传递到在信号ff中的其输出。例如,触发器电路107可以仅在时钟信号clk的每个上升沿上捕获信号din的逻辑状态并将其传递到信号ff。备选地,触发器电路107可以仅在时钟信号clk的每个下降沿上捕获信号din的逻辑状态并将其传递到信号ff。

24.锁存器106的输出信号data和触发器107的输出信号ff被提供到异或逻辑门电路108的输入。异或逻辑门电路108对信号data和ff的当前逻辑状态执行异或布尔逻辑功能,以生成其输出信号error的逻辑状态。如上面所提到的,异或逻辑门电路108的输出信号error被提供到fsm控制器电路101的输入。error信号也可以作为电路100的输出提供。

25.现在在图1、3和4的上下文中讨论在错误检测模式期间电压攻击检测电路100的操作的示例的进一步细节。在错误检测模式期间,电路100检测处于或低于(或高于)阈值电压的供应电压vcc的减小(或增加)。基于阈值回归控制信号thrs来确定阈值电压。图3是示出根据实施例的电压攻击检测电路100可以在错误检测模式期间执行的操作的示例的流程图。图4是示出根据实施例的有限状态机(fsm)控制器电路101中的fsm的状态以及这些状态之间的进展的状态图。

26.当供应电压vcc稳定时(例如,在ic中复位之后以及工作负荷执行之前),在ic的静止状态(quiescent condition)期间理想地执行相对于图3-4公开的错误检测模式。在静止状态期间执行错误检测模式确保了针对延迟电路103的第一故障点、回归延迟和完全校准的延迟确定一致的值。

27.在电压检测电路100的示例性实施例中,电路101-102将可调谐延迟电路103初始设置成其最小延迟值,并且然后增加延迟电路103的延迟,直到error信号被断言(assert)为止。可调谐延迟电路103的最小延迟值是电路103可以提供到信号dd1的相对于信号data的最小延迟。在另一示例性实施例中,电路101-102在error信号被断言时将可调谐延迟电路103初始设置成其最大延迟值,并且然后减小延迟电路103的延迟,直到error信号被解除断言(de-assert)为止。可调谐延迟电路103的最大延迟值是电路103可以提供到信号dd1的相对于信号data的最大延迟。

28.参考图1和4,reset信号被初始地断言,并且calen信号被初始地解除断言,从而引起fsm控制器电路101处于未校准状态(0)401(图4中示出)并且处于复位。在图3中示出的操作301中,reset被解除断言(例如,转换成逻辑低状态)。响应于reset信号被解除断言,fsm控制器电路101不再处于复位。在图3中示出的操作302中,fsm控制器电路101和延迟配置电路102将可调谐延迟电路103设置成其最小或最大延迟值。此外,fsm控制器电路101使用阈值回归控制信号thrs在操作302中确定回归延迟值。阈值回归控制信号thrs可以例如基于用户输入而生成或者从存储装置中检索。

29.在图3中示出的操作303中,calen信号被断言(例如,转换到逻辑高状态)。响应于calen信号被断言,fsm控制器电路101从未校准状态401转换到延迟码校准状态(1)402,如图4中示出的。在操作303中,fsm控制器电路101调整state信号的值以向延迟配置电路102指示fsm处于延迟码校准状态402。在延迟码校准状态402中,fsm控制器电路101和延迟配置电路102执行自校准循环(loop)以校准可调谐延迟电路103的延迟。

30.在操作303之后,fsm控制器电路101确定error信号是否指示在图3中示出的判定操作304中已经达到第一故障点(poff)。作为示例,error信号中的逻辑状态转换可以向电

路101指示已经达到第一故障点。作为另一示例,切换(toggle)预定义次数(number of times)的error可以向电路101指示已经达到第一故障点。作为又一示例,对于时钟信号clk的每个周期的全部或大部分,保持处于逻辑高状态的error信号可以向电路101指示已经达到第一故障点。

31.如果fsm控制器电路101在判定操作304中确定error信号不指示poff,则在图3中示出的操作305中,fsm控制器电路101和延迟配置电路102增加(或减小)可调谐延迟电路103提供到信号dd1的相对于信号data的延迟。作为示例,延迟配置电路102可以响应于指示有限状态机(fsm)处于延迟码校准状态402的state信号而在操作305中调整延迟码调谐信号dct的值。响应于由延迟配置电路102提供的延迟码调谐信号dct的值的调整,可调谐延迟电路103增加(或减小)提供到信号dd1的相对于信号data的延迟。作为更具体的示例,延迟配置电路102可以包含计数器电路,其响应于指示fsm处于延迟码校准状态402的state信号而在操作305中增加(或减小)计数值。在此示例中,延迟配置电路102可以在延迟码调谐信号dct中提供计数值。

32.在自校准循环期间,fsm控制器电路101连续地或不时地确定在操作303中是否仍断言calen信号。在自校准循环期间,如果calen信号被解除断言或者如果reset信号被断言,则fsm控制器电路101中的fsm在操作308中返回到未校准状态401,并且自校准循环终止。

33.还在自校准循环期间,fsm控制器电路101连续地或不时地确定在判定操作304中error信号是否指示已经达到第一故障点(poff)。只要error信号指示尚未达到poff,fsm控制器电路101中的fsm保持处于状态402,并且延迟配置电路102继续在操作305的附加迭代中增加(或减小)可调谐延迟电路103提供到信号dd1的相对于信号data的延迟。

34.响应于可调谐延迟电路103增加(或减小)提供到信号dd1的相对于信号data的延迟,固定延迟电路104和反相器电路105将提供到信号dd2和din的延迟分别增加(或减小)提供到信号dd1的延迟增加(或减小)的相同的量。当提供到信号dd1的延迟增加(或减小)时,如果ic的温度和供应电压vcc不存在改变,则信号din的周期增加(或减小),并且时钟信号clk的周期保持恒定。

35.图5a是示出根据实施例的由图1的电压攻击检测电路100生成的各种信号的波形的示例的定时图。在图5a中示出的示例中,当时钟信号clk处于逻辑高状态时,锁存器106/202将信号din的逻辑状态传递到信号data,触发器107响应于时钟信号clk中的每个上升沿而捕获信号din的逻辑状态,并且可调谐延迟电路103在自校准循环期间增加提供到信号dd1的延迟。在图5a的示例中,当振荡信号din中的上升沿出现(occur)在时钟信号clk中的上升沿之前时,error信号保持处于逻辑低状态。error信号响应于在时钟信号clk中的上升沿之后出现的信号din中的上升沿而转换成逻辑高状态,如图5a中由虚线示出的。error信号中的附加逻辑状态转换可以发生在error信号中的此初始上升沿之后,如图5a中示出的。fsm控制器电路101可以编程成将error信号中的第一逻辑状态转换解释为第一故障点(poff)。作为其它示例,fsm控制器电路101可以被编程成将切换预定义次数的error信号或者对于时钟信号clk的每个周期的全部或大部分保持处于逻辑高状态的error信号解释为第一故障点。

36.如果fsm控制器电路101在判定操作304中确定error信号指示poff,则自校准循环

终止,并且fsm控制器电路101中的fsm转换到图4中示出的回归状态(2)403。在不旨在是限制性的示例性实施例中,到可调谐延迟电路103中具有数量为n个的延迟单元的自校准电路100的最大时钟时延是n+2个时钟周期。在回归状态(2)403中,fsm控制器电路101和延迟配置电路102停止增加(或减小)可调谐延迟电路103提供到信号dd1的相对于信号data的延迟。而且,在回归状态(2)403中,fsm控制器电路101根据操作306确定可调谐延迟电路103的最终延迟值。

37.在操作306中,如果在自校准循环期间通过增加电路103的延迟来生成当前延迟值cd,则fsm控制器电路101和/或延迟配置电路102通过从可调谐延迟电路103的当前延迟值(cd)减去回归延迟值(rs)来确定可调谐延迟电路103的最终延迟值(f)。因此,最终延迟值f=cd-rs。如果在自校准循环期间通过减小电路103的延迟来生成当前延迟值cd,那么fsm控制器电路101和/或延迟配置电路102通过将回归延迟值(rs)添加到可调谐延迟电路103的当前延迟值(cd)来确定可调谐延迟电路103的最终延迟值(f)(即,f=cd+rs)。回归延迟值rs基于阈值回归控制信号thrs中的一个或多个的值来确定。可调谐延迟电路103的当前延迟值cd是当error信号首先指示已经达到poff时电路103提供到信号dd1的相对于信号data的延迟。fsm控制器电路101可以将回归延迟值rs提供到延迟配置电路102。fsm控制器电路101和延迟配置电路102然后将可调谐延迟电路103的延迟设置成在操作306中确定的最终延迟值f。如果calen信号被解除断言或者如果reset信号被断言处于回归状态403,则fsm控制器电路101中的fsm返回到未校准状态401。

38.在操作307中,fsm控制器电路101中的fsm从图4中示出的回归状态(2)403转换到校准状态(3)404。在校准状态(3)404中,电压攻击检测电路100被装备并且准备好感测对集成电路(ic)的电压攻击。

39.标称供应电压指vcc的目标供应电压。标称供应电压通常是恒定电压。然而,实际供应电压vcc可以例如响应于对ic的电压攻击或者响应于由ic中的其它电路从供应电压vcc得到的供应电流而从标称供应电压变化。

40.在校准状态(3)404中,电压攻击检测电路100感测实际供应电压vcc何时达到或超过(即,减小到低于或增加到高于)阈值电压th。使用回归电压rv计算阈值电压th。fsm控制器电路101使用由阈值回归控制信号thrs指示的值来确定回归电压rv。在其中电压检测电路100检测到实际供应电压vcc中的下冲(undershoot)的实施例中,阈值电压th被设置成等于标称供应电压vcc减去回归电压rv(即th=vcc-rv)。在其中电压检测电路100检测到实际供应电压vcc中的过冲(overshoot)的实施例中,阈值电压th被设置成等于标称供应电压vcc加上回归电压rv(即th=vcc+rv)。

41.在其它实施例中,电压检测电路100可以检测在校准状态404中的电压范围之外的实际供应电压vcc的变化。电压的范围可以包括大于和小于vcc的标称供应电压的电压。在这些实施例中,电压检测电路100可以在校准状态404中的错误检测模式期间检测实际供应电压vcc中的过冲和实际供应电压vcc中的下冲。fsm控制器电路101计算上阈值电压uth和下阈值电压lth。作为示例,可以通过将标称供应电压vcc添加到回归电压rv来计算上阈值电压uth,并且可以通过从标称供应电压减去回归电压rv来计算下阈值电压lth。电压检测电路100响应于实际供应电压vcc中高于上阈值电压uth或低于下阈值电压lth的变化,而在错误检测模式期间断言error信号。图5b示出了根据实施例的在错误检测模式中实际供应

电压vcc可以如何相对于上阈值电压uth和下阈值电压lth变化的示例。在图5b的示例中,上阈值电压uth是1.2伏,标称供应电压vcc是1.0伏,并且下阈值电压lth是0.8伏。时间以纳秒(ns)示出。

42.下面的表1示出了对于阈值回归控制信号thrs的5个示例性值,阈值电压(th)和从0.8伏的标称供应电压vcc的下垂(droop)百分比(%)的5个示例性值。在表1中的这5个示例中的每个示例中,回归电压rv等于标称供应电压vcc(0.8伏)减去阈值电压th。跨这5个示例的下垂百分比的变化几乎是线性的。

43.表1thrs下垂%th(伏)01h20.78402h120.70403h200.6404h280.57605h380.496当实际供应电压vcc达到或超过阈值电压th(包括或上阈值电压或下阈值电压)时,可调谐延迟电路103的延迟(以及可能地固定延迟电路104的延迟)已经增加或减小了足以超出定时容限(margin)的量,所述定时容限引起eds电路110在error信号中生成一个或多个逻辑状态转换。当电路100正在错误检测模式中并且在校准状态404中操作时,error信号中的这些一个或多个逻辑状态转换作为向fsm控制器电路101(以及可能地ic中的其它电路)指示ic中已经发生电压攻击的警报起作用。在实施例中,电路100可以快速地在error信号中(例如在被超出的定时容限的1个时钟周期(clk)内)生成警报。在校准状态404中,如果calen信号被解除断言或者如果reset信号被断言,则fsm控制器电路101中的fsm返回到未校准状态401,如图4中示出的。

44.如上面讨论的,在示例性实施例中,图1的可调谐延迟电路103可以是复制数据切片电路,其复制相同ic中的数据路径中的延迟,并且物理上接近复制的数据路径。复制数据切片电路和数据路径接收相同的供应电压vcc。在此示例性实施例中,在第一故障点由延迟码调谐信号dct指示的数字码指示了针对特定供应电压vcc和时钟频率(v、f)对的集成电路(ic)的速度等级,因为可调谐延迟电路103从复制数据切片导出,并且物理上接近实际数据路径。作为具体示例,在快速集成电路管芯中,延迟码调谐信号dct可以指示在第一故障点(poff)处的更大数字码,因为更大数量的延迟单元被用于达到poff。作为另一示例,在更慢的集成电路管芯中,延迟码调谐信号dct可以指示poff处的更小码,因为更少数量的延迟单元被用于达到poff。在此实施例中,延迟码调谐信号dct可以用于在制造之后使用频率驱动的硅分级(binning)基于集成电路管芯的速度来对集成电路管芯进行分类。

45.在第一故障点由延迟码调谐信号dct指示的数字码依赖于ic的工艺、电压和温度(pvt)。出于此原因,在第一故障点由延迟码调谐信号dct指示的数字码是用于安全使用(例如使用动态电压和频率缩放的功率优化和能量恢复)的有价值的参考点。当电压攻击检测电路100嵌入在集成电路(ic)内部时,可调谐延迟电路103在ic的操作期间跟踪ic的pvt状况。ic中的瞬态电压和温度改变(如果有的话)可以由可调谐延迟电路103的延迟的改变以及由error信号的改变来指示,特别是当din信号中的转换靠近时钟信号的转换(或在其之

后)发生时,如例如图5a中示出的。error信号的周期性也是定时容限恢复和定时违反的程度的极好指示符。可以创建电路100的多个实例以在ic中实现紧凑电压传感器的网络,以诊断ic中的供应电压电力网的状况,从而指示ic中的电压故障,并且标记对ic的电压攻击以用于使ic更安全。电压攻击检测电路100还可以用于最大化供应电压vcc和定时保护带,并以动态的、工作负荷依赖的方式改进硅能量效率。

46.本文中相对于图6和7公开了电压攻击检测电路100中的可调谐延迟电路103的详细示例。图6-7中示出的示例性可调谐延迟电路103为了说明性目的而提供并且不旨在是限制性的。许多其它类型的可调整延迟电路可以用于实现图1的可调谐延迟电路103。

47.图6示出了根据实施例的图1的可调谐延迟电路103的示例。在图6的示例性实施例中,可调谐延迟电路103是可调整复制延迟链电路。图6的可调谐延迟电路103是对称且线性化的延迟电路,其包括可调整延迟单元电路的双向、折叠、伸缩延迟链。在图6的实施例中,可调谐延迟电路103包括以折叠的双向延迟链配置耦合的8个延迟单元电路601-608。尽管在图6的示例中示出8个延迟单元电路601-608,应该理解图1的可调谐延迟电路103可以具有匹配任何具体时延要求所需要的任何数量的延迟单元电路。

48.作为另一具体示例,可调谐延迟电路103可以具有53个延迟单元电路,所述延迟单元电路耦合在双向折叠延迟链中,正如图6的实施例。在一些实施例中,延迟单元电路601-608是完全可合成的,并且可以使用任何过程节点(process node)上的本地标准库单元来构建。更快的延迟单元电路允许在捕获电压改变方面更精细的分辨率以及更快的error信号生成。可调谐延迟电路103中的延迟单元电路中的每个延迟单元电路接收相同的供应电压vcc,如图6中示出的。

49.在图6的实施例中,由锁存器106生成的输入data信号被提供到延迟单元电路601的输入,并且在延迟单元电路601的输出处生成延迟输出信号dd1。延迟单元电路601-608中的每个延迟单元电路具有数据转发电路和数据返回电路,它们由通过图1的延迟配置电路102生成的延迟码调谐信号dct控制。延迟单元电路601-608中的数据转发电路中的一个或多个数据转发电路将data信号中接收的上升沿和下降沿沿着通过延迟链的第一延迟路径传播。延迟单元电路601-608中的数据返回电路中的一个或多个数据返回电路将从耦合在延迟链中的最后数据转发电路接收的上升沿和下降沿沿着通过延迟链的第二延迟路径传播到信号dd1中的输出。

50.延迟码调谐信号dct的数字码确定多少延迟单元电路601-608被耦合在延迟链中,所述延迟链将从信号data接收的上升沿和下降沿传播到信号dd1中的输出。延迟配置电路102调整延迟码调谐信号dct的值,以将延迟单元电路601-608中的更多或更少的延迟单元电路耦合到延迟链中,所述延迟链将信号data处的输入耦合到信号dd1处的输出。例如,延迟码调谐信号dct的值的增加可以引起延迟电路103将延迟单元电路601-608中的更多延迟单元电路耦合到延迟链中,从而增加提供到信号dd1的相对于信号data的延迟。作为另一示例,延迟码调谐信号dct的值的减小可以引起延迟电路103将延迟单元电路601-608中的更少延迟单元电路耦合到延迟链中,从而减小提供到信号dd1的相对于信号data的延迟。

51.延迟码调谐信号dct的值确定耦合在延迟链中的最后延迟单元电路。耦合在延迟链中的最后延迟单元电路通过其数据转发和数据返回电路将第一延迟路径中的延迟信号传递到第二延迟路径,从而使后续延迟单元电路与延迟链去耦合,如下面进一步详细讨论

的。

52.图6的可调谐延迟电路103具有由延迟码调谐信号dct配置的8个可能的延迟设置。当信号dct将可调谐延迟电路103配置成具有最小延迟设置时,延迟单元电路601是耦合在延迟链中的仅有延迟单元电路,并且信号data中的转换通过延迟单元电路601中的数据转发和数据返回电路作为信号dd1传播回到输出,而不通过其它延迟单元电路602-608中的任何一个延迟单元电路传递。

53.当信号dct将可调谐延迟电路103配置成具有第二最小延迟设置时,延迟单元电路601和602是耦合在延迟链中的仅有延迟单元电路。利用第二最小延迟设置,信号data中的转换通过延迟单元电路601中的数据转发电路传播,然后作为信号d1传播到延迟单元电路602,然后通过延迟单元电路602中的数据转发和数据返回电路传播,然后作为信号d14传播回到延迟单元电路601,并且最终通过延迟单元电路601中的数据返回电路作为信号dd1传播到输出。

54.当信号dct将可调谐延迟电路103配置成具有第三最小延迟设置时,延迟单元电路601-603是耦合在延迟链中的仅有延迟单元电路。利用第三最小延迟设置,信号data中的转换通过延迟单元电路601中的数据转发电路传播,然后作为信号d1传播到延迟单元电路602,然后通过延迟单元电路602中的数据转发电路传播,然后作为信号d2传播到延迟单元电路603,然后通过延迟单元电路603中的数据转发和数据返回电路传播,然后作为信号d13传播回到延迟单元电路602,然后通过延迟单元电路602中的数据返回电路传播,然后作为信号d14传播回到延迟单元电路601,并且最终通过延迟单元电路601中的数据返回电路作为信号dd1传播到输出。

55.当信号dct将可调谐延迟电路103配置成具有最大延迟设置时,延迟单元电路601-608中的全部8个延迟单元电路耦合在延迟链中。利用最大延迟设置,信号data中的转换通过延迟单元电路601-607中的数据转发电路传播到信号d7,作为信号d1-d7沿第一延迟路径在延迟单元电路之间传递,如图6中示出的。然后信号d7中的转换通过延迟单元电路608中的数据转发和数据返回电路传播到信号d8。然后信号d8中的转换通过延迟单元电路607、606、605、604、603、602和601中的数据返回电路传播回到信号dd1,作为信号d8-d14沿第二延迟路径在延迟单元电路之间传递,如图6中示出的。

56.图7示出了根据实施例的延迟单元电路700的示例。图7的延迟单元电路700是图6的可调谐延迟电路103中的延迟单元电路601-608中的每个延迟单元电路的示例。延迟单元电路700包括两个2对1复用器电路701和702。复用器电路701-702中的每个复用器电路的a数据输入耦合到延迟单元电路700的左输入dil。复用器电路701-702中的每个复用器电路的b数据输入耦合到延迟单元电路700的右输入dir。复用器电路701的输出耦合到延迟单元电路700的左输出dol。复用器电路702的输出耦合到延迟单元电路700的右输出dor。图6中示出的延迟单元电路601-608中的每个延迟单元电路的输入dil和dir以及输出dor和dol分别对应于延迟单元电路700的dil和dir输入以及dor和dol输出。复用器电路701的选择输入s被耦合以接收延迟码调谐信号dct的第一个dct1。复用器电路702的选择输入s被耦合以接收延迟码调谐信号dct的第二个dct2。

57.为了将延迟单元电路700配置成耦合在延迟链中的最后延迟单元电路,将延迟码调谐信号dct1设置成引起复用器电路701将在输入dil处接收的信号转换传递到输出dol的

逻辑状态。例如,如上面所描述的,当可调谐延迟电路103具有最大延迟设置时,延迟单元电路608是耦合在延迟链中的最后延迟单元电路,并且当可调谐延迟电路103具有最小延迟设置时,延迟单元电路601是耦合在延迟链中的最后延迟单元电路。

58.为了将延迟单元电路700配置成耦合在延迟链中的延迟单元电路中的一个延迟单元电路而不是耦合在延迟链中的最后延迟单元电路,将延迟码调谐信号dct2设置成引起复用器702将在输入dil处接收的信号转换传递到输出dor的逻辑状态,并且将延迟码调谐信号dct1设置成引起复用器701将在输入dir处接收的信号转换传递到输出dol的逻辑状态。当延迟单元电路700处于这种配置时,复用器702是数据转发电路,并且复用器701是数据返回电路。因此,延迟单元电路700可配置成针对可调谐延迟电路103中的8个可配置延迟设置中的每个可配置延迟设置而实现图6的延迟单元电路601-608中的每个延迟单元电路。

59.图8示出了根据实施例的包括电压攻击检测电路100的集成电路(ic)管芯800的示例的平面图的俯视图。ic管芯800的部分810在图8的右侧以扩大的细节示出。ic管芯800的部分810包括环形振荡器(ro)的四个攻击群组801-804。环形振荡器的攻击群组801-804中的每个攻击群组包括一个或多个环形振荡器电路。ic管芯800还包括电压攻击检测电路100。

60.攻击群组801-804中的每个攻击群组可以响应于供应电压减少攻击而减少其输出时钟信号中的一个或多个输出时钟信号的频率。电路100位于攻击群组801-804之间,并且被耦合以接收提供到攻击群组801-804中的每个攻击群组中的环形振荡器的相同供应电压。电路100检测对供应电压的电压攻击,并在电压攻击导致可能损害ic管芯800中的安全功能的定时故障之前,在error信号中指示电压攻击的发生,如上面相对于图1-7所描述的。

61.本文中公开的实施例可以结合到任何适合的集成电路或系统中。例如,本文中公开的实施例可以结合到许多类型的装置(例如处理器集成电路、中央处理单元、存储器集成电路、图形处理单元集成电路、专用标准产品(assp)、专用集成电路(asic)和可编程逻辑集成电路)中。可编程逻辑集成电路的示例包括可编程阵列逻辑(pal)、可编程逻辑阵列(pla)、现场可编程逻辑阵列(fpla)、电可编程逻辑装置(epld)、电可擦除可编程逻辑装置(eepld)、逻辑单元阵列(lca)、复杂可编程逻辑装置(cpld)和现场可编程门阵列(fpga),仅举几例。根据示例性实施例,电压检测电路100可以使用可编程逻辑集成电路中的可配置逻辑电路中的本地查找表来构建。

62.在本文中的一个或多个实施例中公开的集成电路可以是数据处理系统的一部分,所述数据处理系统包括以下部件中的一个或多个:处理器;存储器;输入/输出电路;以及外围装置。数据处理系统可以用在各种各样的应用(例如计算机联网(networking)、数据联网、仪器使用(instrumentation)、视频处理、数字信号处理或任何适合的其它应用)中。集成电路可以用于执行各种不同的逻辑功能。

63.以下示例涉及进一步的实施例。示例1是一种电压检测电路,所述电压检测电路包括:可调谐延迟电路,所述可调谐延迟电路响应于输入信号而生成第一延迟信号,其中所述可调谐延迟电路接收供应电压;控制电路,所述控制电路引起由所述可调谐延迟电路提供到所述第一延迟信号的延迟中的第一调整;以及错误检测电路,所述错误检测电路响应于所述第一延迟信号相对于时钟信号的定时的改变而在错误信号中生成错误指示,所述定时的改变由提供到所述第一延迟信号的所述延迟中的所述第一调整引起,其中所述控制电路

响应于所述错误指示而引起由所述可调谐延迟电路提供到所述第一延迟信号的所述延迟中的第二调整,并且其中所述错误检测电路引起所述错误信号指示在所述延迟中的所述第二调整之后所述供应电压达到阈值电压。

64.在示例2中,示例1的电压检测电路可以可选地包括,其中所述错误检测电路是错误检测时序电路,包括:锁存器电路,所述锁存器电路响应于所述时钟信号而存储第二延迟信号的值作为所述输入信号,其中所述第二延迟信号响应于所述第一延迟信号而生成;触发器电路,所述触发器电路响应于所述时钟信号而存储所述第二延迟信号的值;以及异或逻辑门电路,所述异或逻辑门电路响应于存储在所述锁存器电路和所述触发器电路中的所述值而生成所述错误信号。

65.在示例3中,示例2的电压检测电路可以可选地进一步包括:固定延迟电路,所述固定延迟电路耦合到所述可调谐延迟电路的输出,其中所述固定延迟电路响应于所述第一延迟信号而生成第三延迟信号;以及反相器电路,所述反相器电路耦合在所述固定延迟电路与所述锁存器电路之间,其中所述反相器电路响应于所述第三延迟信号而生成所述第二延迟信号。

66.在示例4中,示例1-3中的任何一个的电压检测电路可以可选地包括,其中所述控制电路包括:有限状态机控制器电路,所述有限状态机控制器电路响应于所述错误信号而提供指示有限状态机的状态的控制输出。

67.在示例5中,示例4的电压检测电路可以可选地包括,其中所述控制电路进一步包括:延迟配置电路,所述延迟配置电路响应于指示所述有限状态机的第一状态的所述控制输出而引起所述可调谐延迟电路增加提供到所述第一延迟信号的所述延迟,其中所述延迟配置电路响应于指示所述有限状态机的第二状态的所述控制输出而引起所述可调谐延迟电路将提供到所述第一延迟信号的所述延迟调整基于控制输入确定的量,并且其中所述阈值电压基于所述控制输入而确定。

68.在示例6中,示例1-5中的任何一个的电压检测电路可以可选地包括,其中所述电压检测电路在现场可编程门阵列集成电路中,并且其中所述电压检测电路使用可编程逻辑电路中的查找表来构建。

69.在示例7中,示例1-6中的任何一个的电压检测电路可以可选地包括,其中所述可调谐延迟电路包括双向折叠延迟链,所述双向折叠延迟链包括可调整延迟单元电路,并且其中所述可调整延迟单元电路中的每个可调整延迟单元电路包括耦合在所述可调整延迟单元电路的第一输入与第一输出之间的数据转发电路以及耦合在所述可调整延迟单元电路的第二输入与第二输出之间的数据返回电路。

70.在示例8中,示例1-7中的任何一个的电压检测电路可以可选地包括,其中所述电压检测电路在集成电路中,其中所述可调谐延迟电路包括复制电路,所述复制电路复制所述集成电路中的数据路径中的延迟,并且其中所述数据路径在所述集成电路中并且在所述电压检测电路之外。

71.示例9是一种集成电路,所述集成电路包括:第一存储电路,所述第一存储电路响应于时钟信号而生成第一振荡信号;可调整延迟电路,所述可调整延迟电路使用供应电压延迟所述第一振荡信号以生成第二振荡信号;控制电路,所述控制电路引起对所述可调整延迟电路提供到所述第二振荡信号的相对于所述第一振荡信号的延迟的第一改变;逻辑门

电路,所述逻辑门电路响应于对提供到所述第二振荡信号的所述延迟的所述第一改变而在错误信号中生成错误的指示,其中所述控制电路响应于所述错误信号中的所述错误的所述指示而引起对所述可调整延迟电路提供到所述第二振荡信号的相对于所述第一振荡信号的所述延迟的第二改变,其中所述逻辑门电路引起所述错误信号指示在对提供到所述第二振荡信号的所述延迟的所述第二改变之后所述供应电压何时达到阈值电压。

72.在示例10中,示例9的集成电路可以可选地进一步包括:第二存储电路,所述第二存储电路响应于所述时钟信号而生成第三振荡信号,其中所述逻辑门电路响应于所述第一振荡信号和第三振荡信号而生成所述错误信号。

73.在示例11中,示例10的集成电路可以可选地包括:固定延迟电路,所述固定延迟电路响应于所述第二振荡信号而生成第四振荡信号,其中所述第一存储电路和第二存储电路响应于所述时钟信号而存储由第五振荡信号指示的值,并且其中所述第五振荡信号基于所述第四振荡信号而生成。

74.在示例12中,示例9-11中的任何一个的集成电路可以可选地包括,其中所述控制电路包括:有限状态机控制器电路,所述有限状态机控制器电路提供指示有限状态机的状态的控制输出;以及延迟配置电路,所述延迟配置电路响应于指示所述有限状态机的第一状态的所述控制输出而引起所述可调整延迟电路提供对所述第二振荡信号相对于所述第一振荡信号的所述延迟的所述第一改变。

75.在示例13中,示例12的集成电路可以可选地包括,其中所述延迟配置电路响应于指示所述有限状态机的第二状态的所述控制输出而引起所述可调整延迟电路提供对所述第二振荡信号相对于所述第一振荡信号的所述延迟的所述第二改变达基于控制输入的量,并且其中所述阈值电压基于所述控制输入而确定。

76.在示例14中,示例9-13中的任何一个的集成电路可以可选地包括,其中所述可调整延迟电路包括双向折叠延迟链,所述双向折叠延迟链包括可调整延迟单元电路,并且其中所述可调整延迟单元电路中的每个可调整延迟单元电路包括耦合在所述可调整延迟单元电路的第一输入和第二输入和第一输出之间的第一复用器电路以及耦合在所述可调整延迟单元电路的所述第一输入和第二输入和第二输出之间的第二复用器电路。

77.在示例15中,示例9-14中的任何一个的集成电路可以可选地包括,其中所述可调整延迟电路包括复制电路,所述复制电路复制所述集成电路中的数据路径中的延迟。

78.示例16是一种用于检测集成电路中的电压攻击的方法,所述方法包括:利用可调谐延迟电路生成第一延迟信号,其中所述可调谐延迟电路接收供应电压;利用控制电路引起对由所述可调谐延迟电路提供到所述第一延迟信号的延迟的第一调整;响应于对提供到所述第一延迟信号的所述延迟的所述第一调整而利用错误检测电路在错误信号中生成错误的指示;响应于所述错误信号中的所述错误的所述指示而利用所述控制电路引起对由所述可调谐延迟电路提供到所述第一延迟信号的所述延迟的第二调整;以及在对所述延迟的所述第二调整之后,当所述供应电压已经达到阈值电压时利用所述错误检测电路在所述错误信号中生成攻击指示。

79.在示例17中,示例16的方法可以可选地包括,其中利用所述错误检测电路在所述错误信号中生成所述错误的所述指示包括:响应于时钟信号而将第二延迟信号的值存储在第一存储电路中,其中所述第二延迟信号响应于所述第一延迟信号而生成;响应于所述时

钟信号而将所述第二延迟信号的值存储在第二存储电路中;以及响应于存储在所述第一存储电路和第二存储电路中的所述值而使用逻辑门电路生成所述错误信号。

80.在示例18中,示例16-17中的任何一个的方法可以可选地包括,其中利用所述控制电路引起对由所述可调谐延迟电路提供到所述第一延迟信号的所述延迟的所述第一调整包括:使用控制器电路提供指示有限状态机的状态的控制输出;以及响应于指示所述有限状态机的第一状态的所述控制输出而利用延迟配置电路引起所述可调谐延迟电路提供对提供到所述第一延迟信号的所述延迟的所述第一调整。

81.在示例19中,示例18的方法可以可选地包括,其中响应于所述错误的所述指示而利用所述控制电路引起对由所述可调谐延迟电路提供到所述第一延迟信号的所述延迟的所述第二调整包括:响应于指示所述有限状态机的第二状态的所述控制输出而利用所述延迟配置电路引起所述可调谐延迟电路提供对提供到所述第一延迟信号的所述延迟的所述第二调整达基于控制输入确定的量。

82.在示例20中,示例16-19中的任何一个的方法可以可选地包括,其中利用所述可调谐延迟电路生成所述第一延迟信号进一步包括:使用复制所述集成电路中的数据路径中的延迟的复制电路来相对于所述错误检测电路的输出信号延迟所述第一延迟信号,其中引起对由所述可调谐延迟电路提供到所述第一延迟信号的所述延迟的所述第一调整和第二调整进一步包括生成使用所述控制电路来控制所述延迟的延迟码调谐信号,并且其中所述方法进一步包括使用当所述错误信号指示所述错误时在所述延迟码调谐信号中出现的值作为用于硅分级的所述集成电路的速度等级的指示。

83.在示例21中,示例16-20中的任何一个的方法可以可选地包括,其中利用所述控制电路引起对由所述可调谐延迟电路提供到所述第一延迟信号的所述延迟的所述第一调整进一步包括:使用所述控制电路确定所述错误信号是否指示所述错误;以及如果所述错误信号不指示所述错误,则在由所述控制电路执行的自校准循环期间,调整由所述可调谐延迟电路提供到所述第一延迟信号的相对于输入信号的所述延迟。

84.在示例22中,示例16-21中的任何一个的方法可以可选地包括,其中在对所述延迟的所述第二调整之后,当所述供应电压已经达到所述阈值电压时利用所述错误检测电路在所述错误信号中生成所述攻击指示进一步包括:使用所述错误检测电路来检测所述供应电压中的大于上阈值电压的过冲;以及使用所述错误检测电路来检测所述供应电压中的小于下阈值电压的下冲。

85.为了说明的目的,已经呈现了本发明的示例性实施例的前述描述。前述描述不旨在是穷举的或者将本发明限制到本文中公开的示例。在一些实例中,可以在没有如阐述的其它特征的对应使用的情况下采用本发明的特征。在不脱离本发明的范围的情况下,依据以上教导,许多修改、替换和变化是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1