一种SoC芯片固件下载装置的制作方法

一种soc芯片固件下载装置

技术领域

[0001]

本实用新型涉及芯片存储领域,具体涉及一种片上系统芯片 (system-on-a-chip,soc)固件下载装置。

背景技术:

[0002]

soc芯片内部集成了非易失性存储器,非易失性存储器用于存储固件信息。芯片在实际应用产品当中,需要将固件信息下载到芯片内部的非易失性存储器,才能够正常使用。

[0003]

传统芯片固件下载方法,通常由人工手动下载固件,容易导致下载出错,未下载成功,下载速度慢等问题。不同的封装芯片,需要使用不同的下载装置,人工使用过程当中容易出错。

技术实现要素:

[0004]

(一)要解决的技术问题

[0005]

针对上述问题,本实用新型提供了一种soc芯片固件下载装置,用于至少部分解决传统固件下载方法容易出错、容易下载失败、下载速度慢等技术问题。

[0006]

(二)技术方案

[0007]

本实用新型一方面提供了一种soc芯片固件下载装置,包括:至少一个上板100,每个上板100设有至少一个用于放置soc芯片的socket测试座101,其中,不同上板100中的socket测试座101类型不同,用于对应不同封装类型的soc芯片;下板200,其以可拆卸方式与至少一个上板100 中的一个通信连接,下板200还设有fpga主控制器201及存储器202, fpga主控制器201用于将存储器202中的固件信息发送到soc芯片中。

[0008]

可选地,上板100中多个socket测试座101用于放置相同或不同类型的soc芯片,存储器202存储有至少一种固件信息,其中,fpga主控制器201用于将至少一种固件信息并行发送到相对应的soc芯片中。

[0009]

可选地,fpga主控制器201包括第一ip核421a,第一ip核421a 与存储器202通信连接,以将固件信息发送到soc芯片中。

[0010]

可选地,下板200还与一机械手臂403连接,fpga主控制器201 还包括第二ip核421b,第二ip核421b用于控制机械手臂403将soc芯片放置到socket测试座101中。

[0011]

可选地,fpga主控制器201还包括:第三ip核421c,用于传输下载、测试结果;第四ip核421d,用于外部的手动控制;第五ip核421e,用于显示测试状态和测试结果;第六ip核421f,用于与上板100进行连接。

[0012]

本实用新型另一方面提供了一种基于上述soc芯片固件下载装置的 soc芯片固件下载的方法,包括:s1,根据soc芯片的封装类型,选择 socket测试座101符合该封装类型的上板100,并将该上板100与下板200 通信连接s2,fpga主控制器201根据socket测试座101中soc芯片的类型,从存储器202中选择相应的固件信息发送到该soc芯片中。

[0013]

可选地,soc芯片固件下载的方法还包括:s3,fpga主控制器201 读取该soc芯片固

件信息,并判定该固件信息与s2中发送的固件信息是否一致,否则,重新执行s2~s3。

[0014]

可选地,重试流程包括:多次执行s2~s3,其中每次执行时,选择存储器202中不同的芯片类型的固件信息。

[0015]

可选地,在s2之前,还包括:删除soc芯片中原有的固件信息。

[0016]

可选地,fpga主控制器201根据多个socket测试座101中多个soc 芯片的类型,从存储器202中选择相应的固件信息并行发送到多个soc芯片中。

[0017]

(三)有益效果

[0018]

本实用新型的面向soc芯片的固件下载装置,通过设置至少一个上板 100,不同上板100中的socket测试座101类型不同,可满足不同型号封装、不同类型芯片的固件下载需求;同时,该装置的上板100可替换,在保证了多类型封装芯片可下载的前提下,简化了不同封装芯片固件下载的装置更换流程。本实用新型的soc芯片的固件下载方法,s1-s3以及删除芯片中原有的固件信息,融合了芯片固件信息下载、固件信息删除、固件信息测试三种功能,与传统人工手动下载相比,提高了固件信息下载的准确度,简化了固件下载的装置配置;同时,该方法通过并行方式向多个 socket测试座101中的多个soc芯片发送固件信息,提高了固件信息的下载效率,减少了信息传输的延时。

附图说明

[0019]

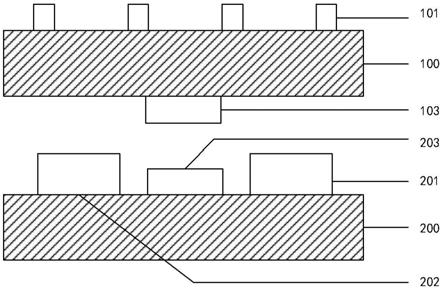

图1示意性示出了根据本实用新型实施例soc芯片固件下载装置的结构示意图;

[0020]

图2示意性示出了根据本实用新型实施例soc芯片固件下载装置中上板的结构示意图;

[0021]

图3示意性示出了根据本实用新型实施例soc芯片固件下载装置中上板连接器母座的两排引脚连接示意图;

[0022]

图4示意性示出了根据本实用新型实施例soc芯片固件下载装置的硬件结构示意图;

[0023]

图5示意性示出了根据本实用新型实施例soc芯片固件下载装置中下板的结构示意图;

[0024]

图6示意性示出了根据本实用新型实施例soc芯片固件下载装置中存储器的内部存储分布;

[0025]

图7示意性示出了根据本实用新型实施例soc芯片固件下载方法的流程示意图;

[0026]

图8示意性示出了根据本实用新型实施例soc芯片固件下载方法全流程示意图;

[0027]

图9示意性示出了根据本实用新型实施例soc芯片固件下载方法中多个芯片并行测试流程示意图。

具体实施方式

[0028]

为使本实用新型的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本实用新型进一步详细说明。

[0029]

本实用新型采用现场可编程门阵列(field programmable gate array,fpga)主控制器构成了一种soc芯片固件下载装置,fpga是一种新型可编程逻辑器件,适合于数字逻辑控制,通过自定义ip软核,设计灵活、集成度高、系统成本低等,可以实现多个芯片的固件

自动下载功能。

[0030]

图1为本实用新型实施例提供的一种soc芯片固件下载装置的结构示意图,包括:上板100,socket测试座101,第一连接端103;下板200, fpga主控制器201,存储器202,第二连接端203。

[0031]

至少一个上板100,每个上板100设有至少一个用于放置soc芯片的 socket测试座101,其中,不同上板100中的socket测试座101类型不同,用于对应不同封装类型的soc芯片;

[0032]

这里所说的至少一个上板100可以是一个上板,也可以是两个或者多个上板,采用不同上板100主要是适配不同封装类型的soc芯片需要采用的不同socket测试座101,例如常用的封装方式有无引线四方扁平封装 (quad flat non-leaded package,qfn)和晶圆片级芯片规模封装(wafer levelchip scale packaging,wlcsp),qfn和wlcsp与外界的连接方式不同,需要使用不同socket测试座101。当然,本实施例适用的芯片封装方式不仅包括qfn和wlcsp,还包括其它封装方式。

[0033]

还需要说明的是至少一个用于放置soc芯片的socket测试座101,当芯片需要下载不同的固件信息时,可以放在不同的socket测试座101上。上板100结构示意图如图2所示,包括连接器母座1031和多个ic socket 测试座101,分别是ic socket测试座i 1011,ic socket测试座ii 1012, ic socket测试座iii1013,ic socket测试座n1014等。其中连接器母座1031 是放置在上板100的反面,ic socket测试座101是放置在上板100的正面,当然,这里,这里并不限定于连接器母座1031只能放置在上板100的反面、ic socket测试座101只能放置在上板100的正面。

[0034]

芯片需要下载不同的固件信息时的放置方式请参见图6和图9,芯片 a1、芯片a2等需要下载芯片类型a的固件信息,放置在ic socket测试座i 1011上;芯片b1、芯片b2等需要下载芯片类型b的固件信息,放置在ic socket测试座ii 1012上;芯片c1、芯片c2等需要下载芯片类型 b的固件信息,放置在ic socket测试座iii1013上。当然,本实施例不仅包括a、b、c三种固件信息,还包括其它可供下载的固件信息。

[0035]

下板200,其以可拆卸方式与至少一个上板100中的一个通信连接,下板200还设有fpga主控制器201及存储器202,fpga主控制器201 用于将存储器202中的固件信息发送到soc芯片中。

[0036]

这里所说的下板200以可拆卸方式与上板100通信连接,请参见图1,是通过设置在上板100反面的第一连接端106和下板200正面的第二连接端107连接,当然,这里并不限定于第一连接端106设置在上板100的反面、第二连接端107设置在下板200的正面,第一连接端106也可以设置在上板100的正面,第二连接端107也可以设置在下板200的反面。其次,第一连接端106和第二连接端107可以是通过连接器连接,例如第一连接端106为连接器母座、第二连接端107为连接器公座。

[0037]

还需要说明的是当上板100和下板200通过连接器连接时,连接器母座1031如图3所示,定义了两排引脚,定义内容如下:第一列左排301 是vcc引脚,该引脚是给待测芯片的电源供电;第一列右排302是gnd 引脚,与待测芯片的gnd相连接;第二列左排303是scl1引脚,与icsocket测试座i 1011的芯片的scl时钟引脚相连;第二列右排304是sda1 引脚,与ic socket测试座i 1011的芯片的sda数据引脚相连;其他列类似定义,分别与ic socket测

试座n的芯片相连。

[0038]

上板100中多个socket测试座101用于放置相同或不同类型的soc芯片,存储器202存储有至少一种固件信息,其中,fpga主控制器用于将至少一种固件信息并行发送到相对应的soc芯片中。

[0039]

这里所说的存储器202存储有至少一种固件信息,存储器202中可以只存储一种固件信息,只供需要该固件信息的芯片下载,也可以存储多种固件信息,供不同类型的芯片下载(请参见图6和图9),固件信息的数量是可以人为设定的。

[0040]

还需要说明的是存储器202的内部存储分布如图6所示,包含了fpgajic固件信息和芯片类型n的固件。

[0041]

①

地址从0到a,是fpga jic固件文件;

[0042]

②

地址从a到b,是芯片类型a的固件;

[0043]

③

地址从b到c,是芯片类型b的固件;

[0044]

④

地址从n到n+1,是芯片类型n的固件。

[0045]

fpga主控制器201根据待测芯片的类型,在存储器202内部,选择需要下载的固件信息,再通过通讯接口,下载到芯片内部。

[0046]

综上所述,本实用新型通过设置至少一个上板100,不同上板100中的socket测试座101类型不同,可满足不同型号封装、不同类型芯片的固件下载需求;同时,该装置的上板100可替换,在保证了多类型封装芯片可下载的前提下,简化了不同封装芯片固件下载的装置更换流程。

[0047]

fpga主控制器201包括第一ip核421a,第一ip核421a与存储器202通信连接,以将固件信息发送到soc芯片中。

[0048]

需要说明的是,fpga主控制器201通过自定义ip软核第一ip核421a,与外部存储器202通信连接,以执行soc芯片固件下载流程。

[0049]

下板200还与一机械手臂403连接,fpga主控制器201还包括第二 ip核421b,第二ip核421b用于控制机械手臂403将soc芯片放置到socket 测试座101中。

[0050]

需要说明的是,fpga主控制器201通过自定义ip软核第二ip核421b,与机械手臂403连接,以执行soc芯片固件拿取、放置操作。

[0051]

在本实施例中第二ip核421b可以为handler通信ip核,机械手臂 403可以为handler机台机械手臂。handler通信ip核控制handler机台机械手臂的步骤包括:

[0052]

①

获取机械手臂将芯片放置就绪,准备开始测试状态;

[0053]

②

告知机械手臂测试结束的状态;

[0054]

③

告知机械手臂将测试成功芯片、超时失败芯片、其他失败芯片分别放置在指定区域。

[0055]

fpga主控制器201还包括:第三ip核421c,用于传输下载结果、测试结果;第四ip核421d,用于外部的手动控制;第五ip核421e,用于显示测试状态和测试结果;第六ip核421f,用于与上板100进行连接。

[0056]

这里所说的fpga主控制器201包括多个ip核,请参见图4的硬件结构示意图,fpga主控制器201包括计算机程序421,该计算机程序421 可以包括代码/计算机可执行指令,计算机程序421中的代码可以包括一个或多个程序模块,例如包括第一ip核421a、第二ip核

421b、第三ip核 421c、第四ip核421d、第五ip核421e、第六ip核421f

……

。当这些ip核组合被fpga主控制器201执行时,使得fpga主控制器201可以执行soc芯片固件下载流程及其任何变形。

[0057]

图5为本实用新型实施例提供的soc芯片固件下载装置的下板200的结构示意图;在本实施例中fpga主控制器201还包括第三ip核421c,第三ip核421c可以为串口通信ip核,通过电平转换器件,与外部串口座404相连。该部分的作用是,将测试结果成功或者失败的信息,传输给制造机台的电脑主机。

[0058]

在本实施例中fpga主控制器201还包括第四ip核421d,第四ip 核421d可以为按键识别ip核,与外部的按键阵列405相连,包括一个复位键reset和n个手动测试控制键keyx_sot。复位键reset,其作用是fpga主控制器201的全局复位;手动测试控制键keyx_sot,其作用是用于手动控制,进行芯片的固件下载,下标x表示不同组的按键的编号。

[0059]

在本实施例中fpga主控制器201还包括第五ip核421e,第五ip核 421e可以为led显示ip核,与外部的led显示阵列406相连,用于显示测试状态和测试结果。每组包含状态显示灯ledx_status和测试结果灯 ledx_results,下标x表示不同组的led指示灯。其状态显示灯 ledx_status,显示固件下载的状态,定义了三种固件下载状态,分别是:

[0060]

①

ledx_status_idle空闲状态,指示灯灯灭;

[0061]

②

ledx_status_blink下载状态,指示灯以1khz闪烁;

[0062]

③

ledx_status_done完成状态,指示灯灯亮。

[0063]

其测试结果灯ledx_results,显示固件下载测试结果状态,定义了2 种结果状态,分别是:

[0064]

①

ledx_results_pass成功状态,指示灯灯亮;

[0065]

②

ledx_results_fail失败状态,指示灯灯灭。

[0066]

在本实施例中fpga主控制器201还包括第六ip核421f,第六ip核 421f可以为i2c通讯ip核,与外部的连接器公座407相连。其引脚定义与连接器母座1031图3中的引脚定义一致,传输vcc,gnd,sclx, sdax等信号。下标x表示不同组的芯片的i2c信号。

[0067]

本实用新型基于以上soc芯片固件下载装置还提供了一种soc芯片固件下载方法,参见图7,包括:

[0068]

s1,根据soc芯片的封装类型,选择socket测试座101符合该封装类型的上板100,并将该上板100与下板200通信连接;

[0069]

s2,fpga主控制器201根据socket测试座101中soc芯片的类型,从存储器202中选择相应的固件信息发送到该soc芯片中。

[0070]

本实施例中的固件下载方法还包括,s3,fpga主控制器201读取该 soc芯片固件信息,并判定该固件信息与s2中发送的固件信息是否一致,否则,重新执行s2~s3。多次执行s2~s3,其中每次执行时,选择存储器202中不同的芯片类型的固件信息。

[0071]

本实施例中的固件下载方法还包括,删除soc芯片中原有的固件信息。

[0072]

这里所说的s1选择合适的上板100,将上板100与下板200通信连接后,即进入图8的开始流程;接收到开始信号后,擦除内部存储单元,即这里所说的删除soc芯片中原有的固件信息;获取芯片类型、基于芯片类型主控制器选择相关联的固件信息、通过i2c接口写入到芯片内部存储单元,即对应这里所说的s2;主控制器通过i2c接口读取芯片内部存储单

元、对比读取数据和写入数据是否一致,即对应这里所说的s3。

[0073]

图8为本实用新型实施例soc芯片固件下载方法全流程示意图。图8 描述的是其中一个ic socket测试座1011,其他的ic socket测试座1011 的流程是类似的,fpga主控制器201根据多个socket测试座101中多个 soc芯片的类型,从存储器202中选择相应的固件信息并行发送到多个 soc芯片中。

[0074]

1)程序开始,fpga主控制器201,等待hander机台的handlerx_sot 起始信号。如果接收到信号,进入下一步操作;如果未接收到信号,继续进入等待状态。

[0075]

2)由于待测芯片内部固件在写入之前,需要先进行擦除的流程。所以fpga主控制器201,通过i2c通讯ip核,擦除芯片内部的固件。该操作成功后,进入下一步操作;如果芯片固件擦除失败,进入失败状态。

[0076]

3)获取芯片类型信息。根据芯片的类型,从存储器202中选择相应的固件信息。该操作成功后,进入下一步操作;如果获取芯片类型出错,进入失败状态。

[0077]

4)fpga主控制器201通过i2c通信ip核,将固件信息下载到芯片内部的存储单元中。该操作成功后,进入下一步操作;如果写入数据出错,进入失败状态。

[0078]

5)fpga主控制器201通过i2c通信ip核,读取芯片内部的存储单元的信息。该操作成功后,进入下一步操作;如果读取数据出错,进入失败状态。

[0079]

6)fpga主控制器201判断读取数据和写入数据,是否一致。该操作成功后,进入下一步操作,串口座404传输成功信息,led显示pass状态;通过handler通信ip核,告知机械手臂403将测试成功芯片放置在测试成功芯片区域;如果数据不一致,进入重试流程状态。

[0080]

7)重试流程状态,判断当前重试次数是否超过了n。如果未超过n 次,再次进入到擦除芯片操作。如果超过n次,串口座404传输超时信息, led显示fail状态;通过handler通信ip核,告知机械手臂403将测试成功芯片放置在超时失败芯片区域。

[0081]

8)上面在2)、3)、4)、5)描述的失败状态下,串口座404传输失败信息,led显示fail状态;通过handler通信ip核,告知机械手臂403 将测试成功芯片放置在其他失败芯片区域。

[0082]

9)最后,fpga主控制器201,通过handler通信ip核,向机台handler 传输结束状态,handlerx_eot,测试结束。

[0083]

图8描述了一个芯片的测试流程,多个芯片并行测试流程如图9所示,横坐标是测试时间t,纵坐标是n个ic socket测试座。从图中可以看到,由于芯片在某个步骤出错导致测试时间缩短,比如图中芯片a1、b2、c2、 n1;或者重试多次导致测试时间加长,如图中芯片的c1。本实用新型采用并行测试,fpga主控制器201根据多个socket测试座101中多个soc芯片的类型,从存储器202中选择相应的固件信息并行发送到多个soc芯片中,每个ic socket测试座的固件下载都是相互独立的,互相不受影响,从而缩短了测试时间。

[0084]

本实用新型不限于特定的通讯接口,使用i2c接口只是为了描述本装置的通讯接口,本装置采用i2c接口访问芯片内部的存储器202,所以icsocket测试座n1014与连接器母座1031,通过i2c接口相连接。

[0085]

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保

护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1