堆栈式半导体封装构件的测试方法及测试设备与流程

本发明涉及一种堆栈式(package on package)半导体封装构件的测试方法及测试设备,尤指一种适用于检测堆栈式半导体封装构件的电性特性或功能的测试设备及其测试方法。

背景技术:

1、随着对于电子产品轻薄短小的体积要求、及效能的需求,要如何在有限空间内放入更多电子组件则成了现今半导体封装技术的发展重点。堆栈式半导体封装(package onpackage,pop)技术就是一种发展出来的解决方案,也就是将至少两个封装体(package)在三维空间(高度)堆栈,而形成三维系统封装(3d system in package sip)。据此,堆栈式封装的优势在于,比传统并排排列的封装方式占用更少的印刷电路板(pcb)空间并简化电路板设计,且又可透过内存与逻辑电路的直接联机来改善频率效能表现。

2、再者,于半导体封装测试的制程中,一般堆栈式半导体封装构件通常是在堆栈封装前,先将上层芯片与下层芯片分别测试,待两者都通过测试后,再予层迭、打线、封装而完成最终产品。然而,目前下层芯片的测试通常需要搭配上层的内存芯片方可进行功能性测试,故下层芯片的测试方式明显较一般单纯的电子组件测试为繁复。

3、在现有技术中,相关测试设备及其测试方法请参阅美国专利us9,519,024b2「堆栈式半导体封装构件的测试设备及其测试方法(apparatus for testing package-on-package semiconductor device and method for testing the same)」,其揭露了当要进行测试时,升降旋臂将驱使容纳有上层芯片(内存芯片)的芯片置放模块移位至升降取放装置与测试座之间,而升降取放装置再连同芯片置放模块下降去电性接触下层芯片,以进行测试;另外,当测试完毕时,升降取放装置再连同芯片置放模块上升后,升降旋臂将驱使芯片置放模块移位而脱离升降取放装置,并位于该升降取放装置的一侧。

4、为了实现堆栈式半导体封装构件的测试,很明显地,上述先前技术特别设置升降旋臂,其除了可升降动作外,还必须旋转动作,如此将造成整体设备的机构复杂且体积庞大,而且整个测试流程也过于繁复,测试效率不佳。

技术实现思路

1、本发明的主要目的是提供一种堆栈式半导体封装构件的测试方法及测试设备,其能以全自动化的方式检测堆栈式半导体封装构件,可显著地简化设备的组成构件,以提高可靠度并降低成本,又可大幅提升测试效率、以及测试准确率。

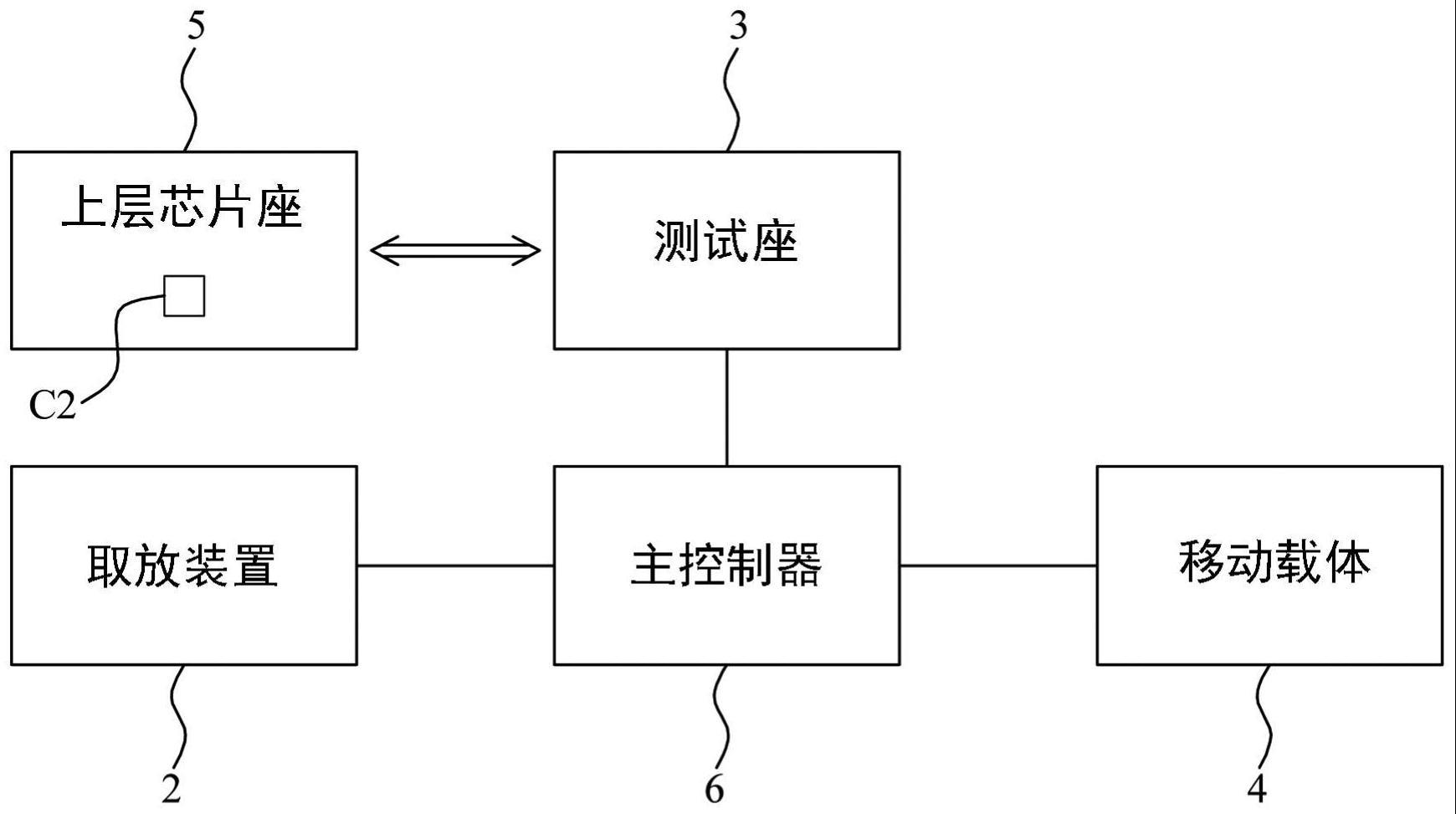

2、为达成上述目的,本发明一种堆栈式半导体封装构件的测试设备,主要包括取放装置、测试座、上层芯片座、以及主控制器;测试座用于容纳第一封装组件,上层芯片座容纳有第二封装组件,主控制器电性连接取放装置、及测试座;其中,当要测试第一封装组件时,主控制器控制取放装置于测试座上加载第一封装组件后,主控制器控制取放装置移载上层芯片座而电性接触测试座上的第一封装组件,以使第二封装组件电性连接于第一封装组件并进行测试。

3、据此,本发明的上层芯片座为独立的零部件,当要进行测试时,取放装置才将上层芯片座移载到测试座上,而使第二封装组件电性连接第一封装组件,由此构成完整的堆栈式芯片架构,以供进行测试。因此,本发明大幅简化了现有堆栈式芯片测试设备的复杂的机构组件,显著降低了成本,同时也增加了可靠度;而且当有变更待测物规格的需求时,也只要简单地替换上层芯片座或测试座就可以了,相当弹性。

4、为达成上述目的,本发明的一种堆栈式半导体封装构件的测试方法,其包括以下步骤:首先,主控制器控制取放装置于测试座上加载第一封装组件;接着,主控制器控制取放装置取得上层芯片座,而上层芯片座容纳有第二封装组件;再者,主控制器控制取放装置移载上层芯片座而电性接触测试座上的第一封装组件,以使第二封装组件电性连接于第一封装组件以进行测试。

5、据此,本发明的测试方法有效地简化了现有堆栈式半导体封装构件的复杂检测步骤,只有在要进行检测时才将上层芯片座移载到测试座上,而当检测完毕后又将上层芯片座移出测试座上,充分实现了检测效率优化。

技术特征:

1.一种堆栈式半导体封装构件的测试设备,其包括:

2.根据权利要求1所述的测试设备,其还包括移动载体,该移动载体用于运载该第一封装组件、及该上层芯片座;该移动载体电性连接于该主控制器,并受控而可选择地移位于该取放装置与该测试座之间或远离该取放装置与该测试座。

3.根据权利要求2所述的测试设备,其中,当要测试该第一封装组件时,该主控制器控制该移动载体移位至该取放装置与该测试座之间,该取放装置自该移动载体取得该第一封装组件,该主控制器控制该移动载体远离该取放装置与该测试座,并控制该取放装置将该第一封装组件置入该测试座后;该主控制器控制该移动载体移位至该取放装置与该测试座之间,该取放装置自该移动载体取得该上层芯片座,该主控制器控制该移动载体远离该取放装置与该测试座,并控制该取放装置连同该上层芯片座下降并电性接触于该测试座上的该第一封装组件并进行测试。

4.根据权利要求1所述的测试设备,其中,该上层芯片座的下表面设有复数接触端子,该第二封装组件电性连接至该复数接触端子;当要测试该第一封装组件时,该主控制器控制该取放装置连同该上层芯片座移动使该复数接触端子电性接触于该测试座上的该第一封装组件并进行测试。

5.根据权利要求1所述的测试设备,其中,该取放装置包括至少一个吸嘴,其设置于该取放装置的下表面并连通至气体负压源。

6.一种堆栈式半导体封装构件的测试方法,其包括以下步骤:

7.根据权利要求6所述的测试方法,其中,于该步骤(a)中,该主控制器控制移动载体移位至该取放装置与该测试座之间,该主控制器控制该取放装置下降并自该移动载体取得该第一封装组件后上升,该主控制器控制该移动载体远离该取放装置与该测试座,并控制该取放装置下降而将该第一封装组件置入该测试座后上升。

8.根据权利要求7所述的测试方法,其中,于该步骤(b)中,该主控制器控制该移动载体移位至该取放装置与该测试座之间,并控制该取放装置下降而自该移动载体取得该上层芯片座后上升,该主控制器控制该移动载体远离该取放装置与该测试座。

9.根据权利要求8所述的测试方法,其中,于该步骤(c)中,该主控制器控制该取放装置连同该上层芯片座下降,并使该上层芯片座电性接触于该测试座上的该第一封装组件而进行测试。

10.根据权利要求9所述的测试方法,其中,于该步骤(c)后还包括步骤(d)、及步骤(e);该步骤(d)是当该第一封装组件测试完毕,该主控制器控制该取放装置连同该上层芯片座上升,该主控制器控制该移动载体移位至该取放装置与该测试座之间,并控制该取放装置下降而将该上层芯片座置于该移动载体后上升,该主控制器控制该移动载体远离该取放装置与该测试座;该步骤(e)是该主控制器控制该取放装置下降并自该测试座取得该第一封装组件后上升,该主控制器控制该移动载体移位至该取放装置与该测试座之间,并控制该取放装置下降而将该第一封装组件置入该移动载体后上升。

技术总结

本发明涉及一种堆栈式半导体封装构件的测试设备,主要包括取放装置、取放装置、上层芯片座及主控制器;其中,当要测试第一封装组件时,主控制器控制取放装置于测试座上加载第一封装组件后,主控制器控制取放装置移载上层芯片座而电性接触测试座上的第一封装组件,以使上层芯片座内的第二封装组件电性连接于第一封装组件并进行测试。据此,本发明的上层芯片座为独立的零部件,当要进行测试时,取放装置才将上层芯片座移载到测试座上,而使第二封装组件电性连接第一封装组件,由此构成完整的堆栈式芯片架构,以供进行测试。

技术研发人员:欧阳勤一,吴信毅,陈建名,吕孟恭,简嘉宏

受保护的技术使用者:致茂电子(苏州)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!