一种基于ZYNQ的星载高重频激光雷达光子计数系统

一种基于zynq的星载高重频激光雷达光子计数系统

技术领域

1.本发明涉及数据采集与处理的技术领域,尤其涉及一种基于zynq的星载高重频激光雷达光子计数系统。

背景技术:

2.激光雷达以激光为载体,通过激光与大气中的微粒或各种气体分子相互作用,进而得到后向散射回波信号,最终通过数据反演和分析得到大气参数。它具有高时空分辨率和高探测精度等优点,因此广泛用于探测大气气溶胶、水汽、臭氧或温度等参量。激光雷达主要由激光发射单元、光学接收单元、采集单元和控制单元组成,其中采集单元与控制单元是激光雷达的重要组成部分。回波光信号通过光电传感器(如apd/pmt等)转换为电信号,经数据采集与预处理(如累加),之后发送到控制单元。控制单元除了接收并存储回波数据外,还需实时监控激光器的运行状态,设置采集卡参数,配置光电探测器增益和高压等,控制单元一般使用通用性强的工控机来实现,从而使激光雷达按设定的步骤有序工作。

3.根据平台的不同,激光雷达可分为地基、车载、机载和星载激光雷达。各种激光雷达对采集控制系统的要求不同,如地基激光雷达要求相对较低,为获得较高的空间分辨率,通常采用商业数据采集卡与工控机(控制单元)配合工作,采集与控制系统一般不是专用的,这使得地基激光雷达采集与控制系统相对较大。而星载激光雷达所处环境相比地基激光雷达复杂得多,如在外太空采用太阳能供电,且在轨运行时无法人工调节或维修,因此要求电子系统具有较低的功耗和较高的稳定性,这就需要硬件结构稳定、器件集成度高的电子系统。由于体积、功耗、稳定性等因素的限制,数据采集与控制系统的软硬件架构均与地基激光雷达不同,市场并无成熟可用的此类设备。

4.目前在云和气溶胶探测方面具有代表性的星载激光雷达为caliop(cloud-aerosol lidar with orthogonal polarization)和cats(cloud aerosol transport system)。cats是首次采用光子探测模式的星载激光雷达,相比calipso,而激光单脉冲能量由传统的百mj减小到几mj级,同时采用了khz的工作频率,大大提高了对地观测的水平分辨率。cats具有两个激光器,单脉冲能量分别为1mj/2mj,重复频率分别为5khz/4khz。它通过提高脉冲重复频率来提高激光器的平均发射功率,在这种探测模式下,雷达接收到的回波信号极弱,仅为光子量级,若使用模拟探测模式,由于信噪比极低,回波信号将无法从背景噪声中被提取出来,因此需采用光子计数技术,即对随机出现的光子脉冲数进行计数,最后通过统计得到不同距离的回波信号强度,这对光子计数采集卡提出了更高的要求。

5.目前商用的光子计数卡(multichannel scaler:mcs)不多,如mcs-pci和easy-mcs分别是采用pci和usb总线的板卡,它们基于可编程逻辑器件对外部脉冲计数,每次触发的计数值均传输到电脑进行软件累加,当激光器触发频率很高(如1mhz)时,由于传输速率的限制可能会导致数据丢失。licel瞬态记录仪在激光雷达领域应用较多,采用以太网接口传输数据,支持模拟和光子计数两种采集模式,但它采用模块化结构,虽然灵活但体积较大,且价格昂贵。以上采集设备,都只有数据采集功能,对于数据传输、数据存储及激光雷达各

单元的控制则需要工控机的参与,这增加了整个激光雷达的结构复杂度。

技术实现要素:

6.为了解决了上述技术问题,本发明提出了一种基于zynq的星载高重频激光雷达光子计数系统,具体技术方案如下:

7.一种基于zynq的星载高重频激光雷达光子计数系统,所述zynq芯片包括可编程逻辑单元pl和处理器系统ps;可编程逻辑单元pl用于采集光子计数探测器的信号,并完成计数和存储;所述可编程逻辑单元pl包括控制模块、与控制模块对应引脚连接的存储模块、输出模块、计数模块;

8.所述计数模块对光子计数探测器输出的脉冲信号进行分段计数,所述控制模块控制计数模块对bin通道相应位置进行计数值累加和累加次数,当达到设定的累加次数后,计数结果被传输至处理器单元ps中;bin宽度对应距离分辨率。

9.具体地说,所述可编程逻辑单元pl还包括axi协议转换模块。

10.具体地说,控制模块包括上升沿检测电路,所述上升沿检测电路包括依次设置的触发器dff1、触发器dff2、非门not1、与门and1、触发器dff3,所述与门的另一输入端与触发器dff1的输出端连接,触发器dff1的输入端输入trigger信号,控制模块中的比较器cmp1的两输入端分别输入bin宽度cnt_bin_width和bin宽度设置值set_bin_width,比较器cmp2的两输入端分别输入bins数cnt_bins_num和bins数设置值set_bins_num,两比较器的输出端与与门and2的两输入端对应连接,与门and2的输出端与触发器dff5的输入端连接,触发器dff5用于输出计数完成信号done和向多路选择器mux1选择端连接,多路选择器mux1的一输入端口与所述上升沿检测电路的输出端连接,另一端口输入0,输出端与触发器dff4的输入端连接,触发器dff4输出正在计数busy信号。

11.具体地说,所述计数模块包括计数器选择单元、初始信号处理单元、第一计数单元和第二计数单元;

12.所述计数器选择单元包括比较器cmp21、多路选择器mux21、非门not21和触发器dff21、减法器sub21及比较器cmp22,所述比较器cmp21的两输入端分别输入内部寄存器的cnt_bin_width与set_bin_width信号,输出端与多路选择器mux21的选择端,多路选择器mux21的输出端经过触发器dff21后,经过非门not21与其中一个输入端连接,另一输入端与触发器dff21输出端直接连接,且输出js_en信号;cnt_bin_width信号输入至比较器cmp22一输入端,set_bin_width信号经过减法器sub21后输入至比较器cmp22的另一输入端,减法器sub21的另一输入端输入信号1,比较器cmp22的输出端输出sig1信号;

13.所述初始信号处理单元包括非门not22、或非门nor22,或非门nor22的两输入端分别为计数开始run信号和正在计数busy信号,输出端为第一计数单元和第二计数单元提供sig2信号,js_en信号经过非门not22后输出~js_en信号;

14.第一计数单元包括与门and21、多路选择器mux22、触发器dff22、多路选择器mux23、加法器add21、触发器dff23;

15.与门and21的两输入端分别输入js_en信号和sig1信号,输出端与多路选择器mux22的一端连接,多路选择器mux22的另一端输入1,选择端输入sig2信号,输出端与触发器dff22的输入端连接,触发器dff22的输出端输出rst_1信号,多路选择器mux23的输入端

分别为0和1,选择端输入~js_en信号;输出端与加法器add21一端连接,加法器add21的输出端经过触发器dff23后输出cnt1信号,cnt1信号反馈到加法器add21的另一输入端,触发器dff23的复位端输入rst_1信号,时钟输入端输入pulse信号;

16.第二计数单元包括与门and22、多路选择器mux24、触发器dff24、多路选择器mux25、加法器add22、触发器dff25;

17.与门and22的两输入端分别输入~js_en信号和sig1信号,输出端与多路选择器mux24的一端连接,多路选择器mux24的另一端输入1,选择端输入sig2信号,输出端与触发器dff24的输入端连接,触发器dff24的输出端输出rst_2信号,多路选择器mux25的输入端分别为0和1,选择端输入js_en信号;输出端与加法器add22一端连接,加法器add22的输出端经过触发器dff25后输出cnt2信号,cnt2信号反馈到加法器add22的另一输入端,触发器dff25的复位端输入rst_2信号,时钟输入端输入pulse信号。

18.具体地说,所述输出模块中的比较器cmp31、比较器cmp32、比较器cmp33连接到与门and31的输入端,bin宽度cnt_bin_width和bin宽度设置值set_bin_width分别对应输入至比较器cmp31两输入端,bins数cnt_bins_num和bins数设置值set_bins_num分别对应输入至比较器cmp32两输入端,累加次数cnt_accum_num和累加次数设置值set_accum_num分别对应输入至比较器cmp33两输入端;

19.减法器sub31两端分别对应输入信号set_bins_num和1,输出端与比较器cmp34的一输入端连接,读ram地址rd_ram_addr作为触发器dff32的输入端,触发器dff32、触发器dff33、触发器dff34依次设置后,触发器dff34的输出端与比较器cmp34的另一输入端连接,比较器cmp34的输出端输出信号sig31,作为多路选择器mux31的选通信号,触发器dff33的输出端输出信号sig32;

20.比较器cmp35一端输入信号sig32,另一端输入1,输出端与加法器and32的一输入端连接,比较器cmp36一端输入信号sig32,另一端输入bins数设置值set_bins_num,输出端与加法器and32的另一输入端连接,加法器and32的第三个输入端输入累加完成标志flag_out信号,输出端输出信号sig33,多路选择器mux32一端输入读ram数据rd_ram_data信号,输出端经过触发器dff35后输出累加数据data_accum信号,累加数据data_accum信号反馈输入到多路选择器mux32的另一输入端,多路选择器mux32的选择端输入累加完成标志flag_out信号;

21.多路选择器mux33一输入端输入0,一输入端输入4,输出端经过加法器add31、触发器dff36后输出累加地址address_accum信号,累加地址address_accum信号反馈到加法器add31的另一输入端,多路选择器mux33的选择端输入信号sig33。

22.具体地说,所述zynq芯片的型号为zynq-7020。

23.具体地说,处理器系统ps包括两个arm cortex-a9。

24.具体地说,系统还包括

25.激光器,用于发射激光,并且输出与激光同步的触发信号;

26.比较器,用于对触发信号进行甄别获得作为采样的起始信号;

27.光子计数探测器,用于探测回波信号,并输出密度与光强成正比的脉冲信号。

28.本发明的优点在于:

29.(1)本技术采用高重频微脉冲激光器,探测方式为光子计数,该激光雷达适合区域

灰霾污染的遥感监测。

30.(2)由于存在散粒噪声和电子热噪声,使得在没有外部光照射条件下,pmt仍有少数随机脉冲输出,即“暗噪声”引起的“暗计数”。而且天空背景光也会导致探测器输出电子脉冲,对激光雷达的观测精度造成很大影响,本技术基于统计学原理,对同一高度区间(bins通道)的回波信号进行对应累加,从而改善信噪比,其中信噪比改善程度与累加次数的平方根成正比。

31.(3)首先在zynq片内的可编程逻辑单元pl上实现了分段计数,采用两个计数器交替计数,消除死时间的影响;在可编程逻辑单元pl内实现硬件累加(通过逻辑电路实现累加运算),运算速度快,且降低了pl与ps间传输的数据吞吐量,同时采用高速axi总线传输数据到ps,从而支持高重频激光器的触发;针对星载特殊环境的需要,在zynq片内的ps中实现了数据预处理和存储相关的控制程序,能在无工控机条件下独立工作。该系统采用软硬件协同设计方法,所有采集和控制功能在zynq内部完成,内部数据传输由内部高速axi总线互联,有效减少了外界的干扰,增加了稳定性和可靠性。

32.(4)当微脉冲激光雷达运用在大气探测领域时,激光器单脉冲能量很低(如1μj)时,回波信号极弱,仅为光子量级(10-14

w),此时只能采用光子计数的探测方式获取有效回波信号。但是,单次触发后的回波光子数极少,而大气背景噪声和电子学中的散粒噪声始终存在,从而导致单次触发后的回波信噪比很低(远小于1),因此不能直接用于大气参量的反演。而采用累加方式可大大提高信噪比,信噪比改善程度与累加次数的平方根成正比。在实际应用时,可通过软件和硬件两种方式累加。软件累加的工作原理是:每次触发时,pl计数的结果通过总线发送到dsp/arm/计算机中,然后在处理器内部以串行工作方式进行累加,速度较慢。而且这种方式对总线带宽要求较高,在高重复频率信号触发(如1mhz)时,此时触发间隔只有1μs,因此数据量大,当数据未被及时传输到接收端时就会丢包,此时即使采用fifo缓存,但连续采集时,fifo也会长期处于“满”的状态,同样导致通信拥堵;硬件累加的工作原理是:pl经多次触发后的计数值直接在内部逻辑电路中以并行工作方式执行累加,而仅仅将最终的累加结果输出到dsp/arm/计算机中,进一步完成数据处理。而当采用硬件累加时,pl的单次触发结果直接与上一次的计数值通过加法器累加,仅当全部累加过程结束后,结果才会通过总线传输,数据传输的频率降低,因此数据传输不会拥堵。综上所述,基于pl的硬件累加方式和高速axi总线共同保证了系统对高重频激光器的支持。

33.(5)axi总线具有高带宽,低延迟的优点,在高重复频率触发时,能将数据及时,高效地传输。本发明采用zynq异构芯片,axi总线在芯片内部连接pl和ps,数据传输的可靠性和有效性都很高。而传统的双芯片方案(如fpga+arm/dsp)缺少高效的通信总线,一般采用spi/fsmc/emif等总线连接,传输效率较低,且总线布置在pcb电路板上,更易受到外部电磁信号的干扰。综上,基于zynq异构芯片的数据采集与控制系统具有稳定性好,数据传输速率高,体积小等优点,而这些优点正是星载高重频激光雷达数据采集与控制系统所需的。

34.(6)zynq具有pl(aritx-7 fpga)和ps(arm cortex-a9双核及其他外设)。在本发明中,利用pl的高速并行处理优势对外部脉冲信号进行重复计数,计数结果经累加后传输到ps中进行预处理(去背景噪声等),同时本系统随时收到地面控制台的控制指令,为了防止在数据预处理过程中被干扰(arm单核工作时,无线模块收到指令后,优先进入中断服务程序,主程序将停止运行,待中断程序结束后再回返回到主程序继续运行),利用内部的两个

arm核分工协作,即arm 1核循环执行故障检测、数据预处理和数据存储,这三项是系统的常态化工作状态,因此稳定性很重要。arm 2核负责与地面控制台进行通信,其工作时间是随机的,如收到地面的控制指令(如读取一段时间的采集数据)后,从非易失性存储器(ide硬盘)中读取数据并无线发送,此时数据串行发送到无线模块,传输需要时间。arm 1核和arm 2核间采用内部消息传递机制,因此避免了两者同时读写ddr3 sdram或硬盘导致的数据冲突。综上,充分运用ps所具有的双核优势,能够大大降低数据丢失的概率,提高控制程序的稳健性。

附图说明

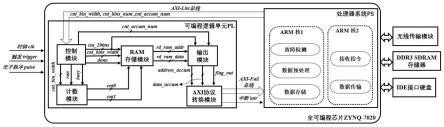

35.图1为系统的整体结构图。

36.图2为控制模块的电路图。

37.图3为计数模块的电路图。

38.图4为输出模块的电路图。

39.图5为整体的回波信号采集过程图。

40.图6为系统获得光子计数的时序图。

具体实施方式

41.一种基于zynq的星载高重频激光雷达光子计数系统,包括

42.激光器,用于发射激光,并且输出与激光同步的触发信号;

43.比较器,用于对触发信号进行甄别获得作为采样的起始信号;

44.光子计数探测器,为pmt(光电倍增管)或spad(单光子雪崩二极管),用于探测回波信号,并输出密度与光强成正比的脉冲信号;

45.采集与控制系统,获得光子计数探测器输出的脉冲信号。在该方案中,采集系统采用zynq芯片(异构多核芯片),具体型号为zynq-7020。

46.如图1所示,所述zynq芯片包括可编程逻辑单元pl和处理器系统ps。

47.可编程逻辑单元pl用于采集光子计数探测器的信号,并完成计数和存储;所述可编程逻辑单元pl包括控制模块、与控制模块对应引脚连接的存储模块、输出模块、计数模块。

48.所述计数模块对光子计数探测器输出的脉冲信号进行分段计数,所述控制模块控制计数模块对bin通道相应位置进行计数值累加,当达到设定的累加次数后,计数结果被传输至处理器单元ps中。bin宽度对应距离分辨率,比如bin宽度为50ns,对应的距离分辨率为7.5m。输出模块从存储模块中读取数据。

49.所述可编程逻辑单元pl还包括axi协议转换模块,为提供数据通信的有效性,防止高频率触发导致数据的拥塞提供条件。协议转换模块将数据封装在axi4协议中,通过高速axi-full总线将数据传输到与处理器系统ps相连的ddr3 sdram,数据传输完成后,可编程逻辑单元pl通过中断intr通知处理器系统ps,提醒处理器系统ps及时从ddr3 sdram中读取数据并处理。由于ddr3 sdram存储器挂载在处理器系统ps上,因此可以快速读出数据并进行预处理,增加了时效性。此外,处理器系统ps还可以通过axi_lite总线将采集所需的bin通道宽度(set_bin_width),bins通道数量(set_bins_num)以及累加次数(set_accum_num)

三个参数传递到可编程逻辑单元pl的控制模块中,实现对光子计数系统的动态配置。axi_lite总线为精简版axi总线,占用较少的逻辑资源,在vivado中通过自定义ip核实现。

50.处理器系统ps包括两个arm cortex-a9,为提升系统运行效率,arm内核1中执行故障检测、数据预处理和数据存储程序,最终将数据保存到硬盘中。arm内核2中实时检测无线传输模块是否收到指令,在收到指令时,执行相应的动作,或将数据通过无线传输模块传输到地面控制台。通过双核协同工作,arm内核2在与地面控制台无线通信时,不会影响arm核1中的程序运行,从而保持了数据的完整性。

51.以下分别对控制模块、计数模块、输出模块的电路做详细描述。

52.控制模块

53.如图2所示,控制模块包括上升沿检测电路,所述上升沿检测电路包括依次设置的触发器dff1、触发器dff2、非门not1、与门and1、触发器dff3,所述与门的另一输入端与触发器dff1的输出端连接,触发器dff1的输入端输入trigger信号,控制模块中的比较器cmp1的两输入端分别输入bin宽度cnt_bin_width和bin宽度设置值set_bin_width,比较器cmp2的两输入端分别输入bins数cnt_bins_num和bins数设置值set_bins_num,两比较器的输出端与与门and2的两输入端对应连接,与门and2的输出端与触发器dff5的输入端连接,触发器dff5用于输出计数完成信号done和向多路选择器mux1选择端连接,多路选择器mux1的一输入端口与所述上升沿检测电路的输出端连接,另一端口输入0,输出端与触发器dff4的输入端连接,触发器dff4输出正在计数busy信号。

54.工作原理为:该模块主要通过生成run,busy和done信号,来完成对计数模块、存储模块、以及输出模块的实时控制。由激光器输出的触发信号trigger的上升沿表示激光已发射,因此通过触发器dff1、触发器dff2、非门not1、与门and3和触发器dff3组成上升沿检测电路对trigger信号进行检测,并输出run信号。当trigger的上升沿到来时,run被拉高,表明采集系统单轮计数开始工作。通过多路选择器mux1和触发器dff4输出当前的计数状态,当run为高,计数未完成(done为低)时,busy被拉高,表示当前正在计数,表明采集系统单轮计数工作正在进行。比较器cmp1、比较器cmp2、与门and2和触发器dff5用于输出计数完成信号done,即当内部计数器的的值cnt_bin_width和cnt_bins_num,同时分别等于设定的参数(由ps输出)set_bin_width和set_bins_num时,done被拉高,此时采集系统单轮计数工作结束。

55.计数模块

56.如图3所示,包括计数器选择单元、初始信号处理单元、第一计数单元和第二计数单元;具体描述如下:

57.所述计数器选择单元包括比较器cmp21、多路选择器mux21、非门not21和触发器dff21、减法器sub21及比较器cmp22,所述比较器cmp21的两输入端分别输入内部寄存器的cnt_bin_width与set_bin_width信号,输出端与多路选择器mux21的选择端,多路选择器mux21的输出端经过触发器dff21后,经过非门not21与其中一个输入端连接,另一输入端与触发器dff21输出端直接连接,且输出js_en信号;cnt_bin_width信号输入至比较器cmp22一输入端,set_bin_width信号经过减法器sub21后输入至比较器cmp22的另一输入端,减法器sub21的另一输入端输入信号1,比较器cmp22的输出端输出sig1信号。

58.所述初始信号处理单元包括非门not22、或非门nor22,或非门nor22的两输入端分

别为计数开始run信号和正在计数busy信号,输出端为第一计数单元和第二计数单元提供sig2信号,js_en信号经过非门not22后输出~js_en信号。

59.第一计数单元包括与门and21、多路选择器mux22、触发器dff22、多路选择器mux23、加法器add21、触发器dff23;

60.与门and21的两输入端分别输入js_en信号和sig1信号,输出端与多路选择器mux22的一端连接,多路选择器mux22的另一端输入1,选择端输入sig2信号,输出端与触发器dff22的输入端连接,触发器dff22的输出端输出rst_1信号,多路选择器mux23的输入端分别为0和1,选择端输入~js_en信号;输出端与加法器add21一端连接,加法器add21的输出端经过触发器dff23后输出cnt1信号,cnt1信号反馈到加法器add21的另一输入端,触发器dff23的复位端输入rst_1信号,时钟输入端输入pulse信号。

61.第二计数单元包括与门and22、多路选择器mux24、触发器dff24、多路选择器mux25、加法器add22、触发器dff25;

62.与门and22的两输入端分别输入~js_en信号和sig1信号,输出端与多路选择器mux24的一端连接,多路选择器mux24的另一端输入1,选择端输入sig2信号,输出端与触发器dff24的输入端连接,触发器dff24的输出端输出rst_2信号,多路选择器mux25的输入端分别为0和1,选择端输入js_en信号;输出端与加法器add22一端连接,加法器add22的输出端经过触发器dff25后输出cnt2信号,cnt2信号反馈到加法器add22的另一输入端,触发器dff25的复位端输入rst_2信号,时钟输入端输入pulse信号。

63.计数开始run信号和正在计数busy信号接入或非门nor21,单轮触发结束时,run和busy均为低电平,此时nor21的输出信号sig2为高电平,第一计数单元的多路选择器mux22和第二计数单元的多路选择器mux24输出为高电平,因此可同时对计数器清零(触发器dff22和触发器dff25输出高电平,清零信号rst_1和rst_2均为1)。

64.计数过程中(计数开始信号run或正在计数信号busy至少一个为高电平)sig2为低电平,多路选择器mux22和多路选择器mux24的输入分别接入与门and21和与门and22。

65.比较器cmp21对bin宽度cnt_bin_width和bin宽度设置值set_bin_width进行比较。当它们相等时,js_en信号翻转(js_en变为~js_en,反之亦然),翻转功能由多路选择器mux21、非门not21和触发器dff21实现。js_en及其反相信号~js_en(由非门not22产生)分别接入与门and21和与门and22。

66.同时,减法器sub21和比较器cmp22对bin宽度值cnt_bin_width和bin宽度设置值set_bin_width-1值进行比较。当它们相等时,sig1为高电平,表示设定的通道时间已到,允许对计数器1和2清零,sig1信号接入与门and21和与门and22。js_en(或~js_en)与sig1信号对计数器交替清零,清零动作与bin宽度设置值set_bin_width同步(如set_bin_width对应50ns,则清零周期为50ns)。

67.当js_en信号为高电平时,计数器的多路选择器mux22输出1,此时当外部脉冲pulse上升沿到来时,第二计数单元的计数值加1(通过触发器dff25和加法器add22实现)。同理js_en信号为低电平时,计数器的多路选择器mux25输出1,此时当外部脉冲pulse上升沿到来时,第二计数单元的计数值加1(通过触发器dff25和加法器add22实现)。

68.输出模块

69.如图4所示,所述输出模块中的比较器cmp31、比较器cmp32、比较器cmp33连接到与

门and31的输入端,bin宽度cnt_bin_width和bin宽度设置值set_bin_width分别对应输入至比较器cmp31两输入端。bins数cnt_bins_num和bins数设置值set_bins_num分别对应输入至比较器cmp32两输入端。累加次数计数cnt_accum_num和累加次数设置值set_accum_num分别对应输入至比较器cmp33两输入端。即bin宽度值cnt_bin_width,bins数cnt_bins_num以及累加次数计数值cnt_accum_num分别与ps输出的参数(set_bin_width,set_bins_num和set_accum_num)相等时,and31的输出信号被拉高,表明一次累加过程结束。

70.与门and31的输出端与多路选择器mux31的已输入端连接,另一输入端输入0,输出端经过触发器dff31后输出累加完成标志flag_out信号。

71.减法器sub31两端分别对应输入信号set_bins_num和1,输出端与比较器cmp34的一输入端连接,读ram地址rd_ram_addr作为触发器dff32的输入端,触发器dff32、触发器dff33、触发器dff34依次设置后,触发器dff34的输出端与比较器cmp34的另一输入端连接,比较器cmp34的输出端输出信号sig31,作为多路选择器mux31的选通信号,触发器dff33的输出端输出信号sig32。sig31信号用于复位累加标志信号flag_out,即当读地址信号与set_bins_num-1的值相同时(表示读取完成),sig31为高电平。此时多路选择器mux31的输入为0,触发器dff31输出为0,即清零累加完成标志信号flag_out,方便下一次累加标志信号的产生。触发器dff32、触发器dff33、触发器dff34组成延迟单元,对ram读地址信号rd_ram_addr延迟三个时钟周期,以防止过早对flag_out复位。

72.比较器cmp35一端输入信号sig32,另一端输入1,输出端与加法器and32的一输入端连接,比较器cmp36一端输入信号sig32,另一端输入bins数设置值set_bins_num,输出端与加法器and32的另一输入端连接,加法器and32的第三个输入端输入累加完成标志flag_out信号,输出端输出信号sig33,多路选择器mux32一端输入读ram数据rd_ram_data信号,输出端经过触发器dff35后输出累加数据data_accum信号,累加数据data_accum信号反馈输入到多路选择器mux32的另一输入端,多路选择器mux32的选择端输入累加完成标志flag_out信号;多路选择器mux32和触发器dff35用于控制累加数据data_accum的值。当累加结束(flag_out为高)时,data的值等于存储模块ram中的数据rd_ram_data,其余情况下,累加数据继续保存原值。多路选择器mux33一输入端输入0,一输入端输入4,输出端经过加法器add31、触发器dff36后输出累加地址address_accum信号,累加地址address_accum信号反馈到加法器add31的另一输入端,多路选择器mux33的选择端输入信号sig33。比较器cmp35、比较器cmp36、与门and32、多路选择器mux33、加法器add31产生累加地址信号address_accum。当累加完成(flag_out为高电平),且rd_ram_addr延迟后的值sig2信号(dff3输出)满足1≤sig2≥set_bins_num(即数据尚未传输结束)时,累加地址信号address_accum自增1,此时ram中的数据依次被读出,其余情况下,累加地址为0。flag_out拉高时,ram存储模块中累加的数据data_accum依次传输到axi协议转换器(传输期间flag_out保持高电平,直到传输结束),最终输出到与ps相连的ddr3 sdram。

73.根据上述系统,整体的回波信号采集过程如图5所示,激光器在发射激光的同时,输出与激光同步的触发信号,该信号经过高速比较器甄别后,输出trigger,作为光子计数系统的起始信号。pmt光子探测器探测到回波信号pulse后,输入到光子计数系统。为了获取不同高度气溶胶浓度的分布特性,采用分段计数法对回波光子信号进行计数,即bin宽度(如50ns,可设置)的计数值代表一段高度区间(根据光的传播速度,50ns对应7.5m)内的回

波光子数,bins数对应总探测距离,如当bins通道时间为50ns,且bins通道数为5000时,总探测距离为37.5km(bin宽度*bins数)。研究表明,信噪比改善程度与累加次数的平方根成正比,因此对同一高度区间(如每次触发的第一个bins通道,图中深灰色填充区域)的回波光子数对应累加(如104次,可设置)。累加结束后,回波信号强度分布可由采集的数据恢复,表示不同高度的气溶胶浓度。

74.根据上述采集过程,获得光子计数的时序如图6所示,采集系统的主时钟信号clk由和晶振和锁相环(pll)产生。外部触发信号trigger输入到采集系统后,由上升沿检测电路输出run信号(trig_r和trig_rr分别是trigger延迟1和2个周期的信号,run=~trig_rr&trig_r),run为计数开始信号,当其有效后,busy信号拉高,表示计数器正在工作。

75.为减小计数死时间的影响(计数器存储数据需要时间,在此期间不能计数),采用“乒乓”方式工作,即当其中一个计数器计数时,另一个计数器存储,反之亦然。cnt1和cnt2是两个独立的计数器,单次计数周期即bin宽度(此处为50ns)可调节,cnt_en对这两个计数器进行交替选择,以防止数据存储过程导致的漏计数事件发生。pulse为单光子探测器的输出信号,该信号随机出现,且相邻脉冲可能离得很近,本文采用了异步逻辑设计方法,有效减少了漏计数的概率。

76.计数完成时,done输出一个周期的高电平信号,指示单次触发引起的采样结束(图中虚线矩形框为单次触发过程)。所有累加过程完成后,flag_out输出高电平信号,表示本次累加过程结束,ram存储模块中的数据将通过axi协议转换器被依次输出到ps。

77.以上仅为本发明创造的较佳实施例而已,并不用以限制本发明创造,凡在本发明创造的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明创造的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1