磁传感器装置的制作方法

1.本发明涉及一种构成为检测互不相同的多个方向的多个磁场的磁传感器装置。

背景技术:

2.近年来,在各种用途中利用使用了磁阻效应元件的磁传感器。在包含磁传感器的系统中,有时想要利用设置在基板上的磁阻效应元件检测包含与基板的面垂直的方向的分量的磁场。在该情况下,通过设置将与基板的面垂直的方向的磁场转换成与基板的面平行的方向的磁场的软磁性体,或在形成在基板上的倾斜面上配置磁阻效应元件,能够检测包含与基板的面垂直的方向的分量的磁场。

3.在日本专利申请公开2006-261401号公报中公开有一种x轴传感器、y轴传感器以及z轴传感器设置在基板上的磁传感器。构成z轴传感器的磁阻效应元件设置于形成于基板的基底膜的突起部的斜面。

4.在将磁阻效应元件配置在倾斜面上的磁传感器中,不需要转换磁场的软磁性体。然而,软磁性体有时也作为屏蔽件发挥作用。即,该软磁性体有时构成为具有几乎不使应检测方向的磁场衰减,但使与应检测方向不同的方向的磁场遮断或衰减的功能。因此,在这样的软磁性体、或屏蔽件未被设置的磁传感器中,磁阻效应元件的灵敏度会根据与应检测方向不同的方向的磁场而变化,其结果,有时磁传感器的检测精度降低。

技术实现要素:

5.本发明的目的在于提供能够在构成为检测互不相同的多个方向的多个磁场的磁传感器装置中减小检测对象的磁场以外的磁场所引起的误差的磁传感器装置。

6.本发明的磁传感器装置具备:第一检测电路,其构成为检测作为检测对象的磁场的对象磁场的一方向的分量,并生成第一检测信号;第二检测电路,其检测对象磁场的另一方向的分量,并生成第二检测信号;以及处理器。

7.处理器构成为执行如下处理:第一生成处理,使用第一检测信号生成第一初始检测值;第二生成处理,使用第二检测信号生成第二初始检测值;第一修正处理,使用根据最新的第二初始检测值生成的第二修正值来修正第一初始检测值,并更新第一初始检测值;第二修正处理,使用根据最新的第一初始检测值生成的第一修正值来修正第二初始检测值,并更新第二初始检测值;确定处理,将最新的第一初始检测值确定为与平行于第一基准方向的对象磁场的分量具有对应关系的第一检测值,并且将最新的第二初始检测值确定为与平行于第二基准方向的对象磁场的分量具有对应关系的第二检测值。处理器在交替执行第一修正处理和第二修正处理之后,执行确定处理。

8.在本发明的磁传感器装置中,处理器在交替执行第一修正处理和第二修正处理之后,执行确定处理。由此,根据本发明,能够减小检测对象的磁场以外的磁场所引起的误差。

9.本发明的其它目的、特征及优点通过以下的说明而变得充分清楚。

附图说明

10.图1是表示本发明的第一实施方式的磁传感器装置的立体图。

11.图2是表示本发明的第一实施方式的磁传感器装置的俯视图。

12.图3是表示本发明的第一实施方式的磁传感器装置的结构的功能框图。

13.图4是表示本发明的第一实施方式的第一检测电路的电路结构的电路图。

14.图5是表示本发明的第一实施方式的第二检测电路的电路结构的电路图。

15.图6是表示本发明的第一实施方式的第三检测电路的电路结构的电路图。

16.图7是表示本发明的第一实施方式的第一芯片的一部分的俯视图。

17.图8是表示本发明的第一实施方式的第一芯片的一部分的截面图。

18.图9是表示本发明的第一实施方式的第二芯片的一部分的俯视图。

19.图10是表示本发明的第一实施方式的第二芯片的一部分的截面图。

20.图11是表示本发明的第一实施方式的磁阻效应元件的侧视图。

21.图12是表示本发明的第一实施方式的处理器的结构的功能框图。

22.图13是表示本发明的第二实施方式的第一检测电路的电路结构的电路图。

23.图14是表示本发明的第二实施方式的第二检测电路的电路结构的电路图。

24.图15是表示本发明的第二实施方式的第三检测电路的电路结构的电路图。

25.图16是表示本发明的第三实施方式的磁传感器装置的结构的功能框图。

26.图17是表示本发明的第三实施方式的第一检测电路的电路结构的电路图。

27.图18是表示本发明的第三实施方式的第二检测电路的电路结构的电路图。

28.图19是表示本发明的第三实施方式的第三检测电路的电路结构的电路图。

29.图20是表示本发明的第三实施方式的多个磁阻效应元件和多个磁轭的立体图。

30.图21是表示本发明的第三实施方式的多个磁阻效应元件和多个磁轭的侧视图。

31.图22是表示本发明的第三实施方式的处理器的结构的功能框图。

具体实施方式

32.[第一实施方式]

[0033]

以下,参照附图,对本发明的实施方式进行详细的说明。首先,参照图1~图3,对本发明的第一实施方式的磁传感器装置的结构进行说明。图1是表示磁传感器装置100的立体图。图2是表示磁传感器装置100的俯视图。图3是表示磁传感器装置100的结构的功能框图。磁传感器装置100具备磁传感器1。

[0034]

磁传感器装置100具备第一芯片2、第二芯片3以及支撑第一及第二芯片2、3的支撑体4。磁传感器1由第一芯片2和第二芯片3构成。第一芯片2、第二芯片3及支撑体4均具有长方体形状。支撑体4具有作为上表面的基准平面4a、位于与基准平面4a相反侧的下表面、以及将基准平面4a和下表面连接的四个侧面。

[0035]

在此,参照图1及图2,对本实施方式的基准坐标系进行说明。基准坐标系是以磁传感器装置100为基准的坐标系,是由三个轴定义的正交坐标系。在基准坐标系中,定义x方向、y方向、z方向。x方向、y方向、z方向相互正交。在本实施方式中,特别是将与支撑体4的基准平面4a垂直的方向、即从支撑体4的下表面朝向基准平面4a的方向设为z方向。另外,将与x方向相反的方向设为-x方向,将与y方向相反的方向设为-y方向,将与z方向相反的方向

设为-z方向。定义基准坐标系的三个轴是与x方向平行的轴、与y方向平行的轴、与z方向平行的轴。

[0036]

以下,将相对于基准的位置处于z方向的前方的位置称为“上方”,将相对于基准的位置处于与“上方”相反侧的位置称为“下方”。另外,对于磁传感器装置100的构成要素,将位于z方向的一端的面称为“上表面”,将位于-z方向的一端的面称为“下表面”。另外,“从z方向观察时”这样的表达是指从沿z方向分开的位置观察对象物。

[0037]

第一芯片2具有位于彼此相反侧的上表面2a及下表面和将上表面2a及下表面连接的四个侧面。第二芯片3具有位于彼此相反侧的上表面3a及下表面和将上表面3a及下表面连接的四个侧面。

[0038]

第一芯片2以第一芯片2的下表面与支撑体4的基准平面4a相对的姿势安装在基准平面4a上。第二芯片3以第二芯片3的下表面与支撑体4的基准平面4a相对的姿势安装在基准平面4a上。第一芯片2和第二芯片3分别通过例如粘接剂6、7与支撑体4接合。

[0039]

第一芯片2具有设置在上表面2a上的多个第一电极焊盘21。第二芯片3具有设置在上表面3a上的多个第二电极焊盘31。支撑体4具有设置在基准平面4a上的多个第三电极焊盘。虽未图示,在磁传感器装置100中,多个第一电极焊盘21、多个第二电极焊盘31以及多个第三电极焊盘中对应的两个电极焊盘通过接合线相互连接。

[0040]

在此,将与基准平面4a垂直的方向的尺寸称为厚度。如图1所示,第一芯片2的厚度和第二芯片3的厚度也可以相同。另外,支撑体4的厚度也可以大于第一芯片2的厚度及第二芯片3的厚度。

[0041]

磁传感器1具备第一检测电路10、第二检测电路20以及第三检测电路30。第一芯片2包含第一检测电路10。第二芯片3包含第二检测电路20和第三检测电路30。因为磁传感器1是磁传感器装置100的构成要素,所以也可以说磁传感器装置100具备第一~第三检测电路10、20、30。

[0042]

磁传感器装置100还具备处理器40。支撑体4包含处理器40。第一~第三检测电路10、20、30和处理器40经由多个第一电极焊盘21、多个第二电极焊盘31、多个第三电极焊盘及多个接合线而连接。

[0043]

第一~第三检测电路10、20、30各自包含多个磁気检测元件,构成为检测对象磁场而生成至少一个检测信号。在本实施方式中,特别是多个磁気检测元件为多个磁阻效应元件。以下,将磁阻效应元件记为mr元件。

[0044]

处理器40构成为通过对第一~第三检测电路10、20、30生成的多个检测信号进行处理,生成与规定的基准位置处的磁场的互不相同的三个方向的分量具有对应关系的第一检测值、第二检测值及第三检测值。在本实施方式中,特别是上述的互不相同的三个方向为与xy平面平行的两个方向和与z方向平行的方向。处理器40例如由面向特定用途的集成电路(asic)构成。

[0045]

接下来,参照图3~图10,对第一~第三检测电路10、20、30进行说明。图4是表示第一检测电路10的电路结构的电路图。图5是表示第二检测电路20的电路结构的电路图。图6是表示第三检测电路30的电路结构的电路图。图7是表示第一芯片2的一部分的俯视图。图8是表示第一芯片2的一部分的截面图。图9是表示第二芯片3的一部分的俯视图。图10是表示第二芯片3的一部分的截面图。

[0046]

在此,如图7及图9所示,如下定义u方向和v方向。u方向是从x方向朝向-y方向旋转的方向。v方向是从y方向朝向x方向旋转的方向。在本实施方式中,特别是将u方向设为从x方向朝向-y方向旋转α的方向,将v方向设为从y方向朝向x方向旋转α的方向。此外,α是大于0

°

且小于90

°

的角度。在一个例子中,α是45

°

。另外,将与u方向相反的方向设为-u方向,将与v方向相反的方向设为-v方向。

[0047]

在本实施方式中,u方向与本发明的“第一基准方向”对应。另外,在本实施方式中,v方向与本发明的“第二基准方向”对应。第一基准方向(u方向)和第二基准方向(v方向)均与基准平面4a平行且相互正交。

[0048]

另外,如图10所示,如下定义w1方向和w2方向。w1方向是从v方向朝向-z方向旋转的方向。w2方向是从v方向朝向z方向旋转的方向。在本实施方式中,特别是将w1方向设为从v方向朝向-z方向旋转β的方向,将w2方向设为从v方向朝向z方向旋转β的方向。此外,β是大于0

°

且小于90

°

的角度。另外,将与w1方向相反的方向设为-w1方向,将与w2方向相反的方向设为-w2方向。w1方向及w2方向分别与u方向正交。

[0049]

第一检测电路10构成为,检测对象磁场的与u方向平行的方向的分量,生成与该分量具有对应关系的至少一个第一检测信号。第二检测电路20构成为,检测对象磁场的与w1方向平行的方向的分量,生成与该分量具有对应关系的至少一个第二检测信号。第三检测电路30构成为,检测对象磁场的与w2方向平行的方向的分量,生成与该分量具有对应关系的至少一个第三检测信号。

[0050]

如图4所示,第一检测电路10包含电源端v1、接地端g1、信号输出端e11、e12、第一电阻部r11、第二电阻部r12、第三电阻部r13、以及第四电阻部r14。第一检测电路10的多个mr元件构成第一~第四电阻部r11、r12、r13、r14。

[0051]

第一及第二电阻部r11、r12在将第一节点p11和第二节点p12电连接的路径即第一路径(图4中的左侧的路径)上串联连接。第三及第四电阻部r13、r14在将第一节点p11和第二节点p12电连接的其它路径即第二路径(图4中的右侧的路径)上串联连接。

[0052]

第一及第四电阻部r11、r14与第一节点p11连接。第二及第三电阻部r12、r13与第二节点p12连接。第一节点p11与电源端v1连接。第二节点p12与接地端g1连接。第一电阻部r11和第二电阻部r12的连接点与信号输出端e11连接。第三电阻部r13和第四电阻部r14的连接点与信号输出端e12连接。

[0053]

如图5所示,第二检测电路20包含电源端v2、接地端g2、信号输出端e21、e22、第一电阻部r21、第二电阻部r22、第三电阻部r23、以及第四电阻部r24。第二检测电路20的多个mr元件构成第一~第四电阻部r21、r22、r23、r24。

[0054]

第二检测电路20的电路结构基本上与第一检测电路10的电路结构相同。如果将第一检测电路10的电路结构的说明中的电源端v1、接地端g1、信号输出端e11、e12、电阻部r11、r12、r13、r14及节点p11、p12分别替换为电源端v2、接地端g2、信号输出端e21、e22、电阻部r21、r22、r23、r24及节点p21、p22,则成为第二检测电路20的电路结构的说明。

[0055]

如图6所示,第三检测电路30包含电源端v3、接地端g3、信号输出端e31、e32、第一电阻部r31、第二电阻部r32、第三电阻部r33、以及第四电阻部r34。第三检测电路30的多个mr元件构成第一~第四电阻部r31、r32、r33、r34。

[0056]

第三检测电路30的电路结构基本上与第一检测电路10的电路结构相同。如果将第

一检测电路10的电路结构的说明中的电源端v1、接地端g1、信号输出端e11、e12、电阻部r11、r12、r13、r14及节点p11、p12分别替换为电源端v3、接地端g3、信号输出端e31、e32、电阻部r31、r32、r33、r34及节点p31、p32,则成为第三检测电路30的电路结构的说明。

[0057]

对电源端v1~v3各自施加规定大小的电压或电流。接地端g1~g3各自接地。

[0058]

以下,将第一检测电路10的多个mr元件称为多个第一mr元件50a,将第二检测电路20的多个mr元件称为多个第二mr元件50b,将第三检测电路30的多个mr元件称为多个第三mr元件50c。因为第一~第三检测电路10、20、30是磁传感器1的构成要素,所以也可以说磁传感器1包含多个第一mr元件50a、多个第二mr元件50b及多个第三mr元件50c。另外,对任意的mr元件标注符号50表示。

[0059]

图11是表示mr元件50的侧视图。mr元件50是自旋阀型的mr元件。mr元件50具有:具有方向被固定的磁化的磁化固定层52、具有方向可根据对象磁场的方向而变化的磁化的自由层54、以及配置于磁化固定层52和自由层54之间的间隙层53。mr元件50可以是tmr(隧道磁阻效应)元件,也可以是gmr(巨磁阻效应)元件。在tmr元件中,间隙层53是隧道势垒层。在gmr元件中,间隙层53是非磁性导电层。在mr元件50中,电阻值根据自由层54的磁化的方向相对于磁化固定层52的磁化的方向所成的角度而变化,在该角度为0

°

时,电阻值成为最小值,在角度为180

°

时,电阻值成为最大值。在各mr元件50中,自由层54具有易磁化轴方向成为与磁化固定层52的磁化的方向正交的方向的形状各向异性。此外,作为在自由层54设定规定的方向的易磁化轴的方法,也能够使用对自由层54施加偏置磁场的磁体。

[0060]

mr元件50还具有反铁磁性层51。反铁磁性层51、磁化固定层52、间隙层53及自由层54被依次层叠。反铁磁性层51由反铁磁性材料构成,在与磁化固定层52之间产生交换耦合,固定磁化固定层52的磁化的方向。此外,磁化固定层52也可以是所谓的自钉扎型的固定层(synthetic ferri pinned(合成铁钉扎)层,sfp层)。自钉扎型的固定层具有层叠了铁磁性层、非磁性中间层及铁磁性层的层叠铁结构,使两个铁磁性层反铁磁性地耦合而成。在磁化固定层52为自钉扎型的固定层的情况下,也可以省略反铁磁性层51。

[0061]

此外,mr元件50中的层51~54的配置也可以与图11所示的配置上下相反。

[0062]

在图4~图6中,实心箭头表示mr元件50的磁化固定层52的磁化的方向。另外,空心箭头表示不对mr元件50施加对象磁场时的、mr元件50的自由层54的磁化的方向。

[0063]

在此,如下定义第一磁化方向、第二磁化方向、第三磁化方向及第四磁化方向。第一磁化方向是与平行于z方向的轴(以下,称为z轴。)交叉的一方向。第二磁化方向是与z轴交叉的一方向、即与第一磁化方向相反的一方向。第三磁化方向是与z轴交叉的一方向、即与第一磁化方向正交的一方向。第四磁化方向是与z轴交叉的一方向、即与第三磁化方向相反的一方向。

[0064]

在第一检测电路10中,第一磁化方向是u方向,第二磁化方向是-u方向,第三磁化方向是v方向,第四磁化方向是-v方向。在图4所示的例子中,第一及第三电阻部r11、r13各自中的磁化固定层52的磁化包含第一磁化方向(u方向)的分量。第二及第四电阻部r12、r14各自中的磁化固定层52的磁化包含第二磁化方向(-u方向)的分量。

[0065]

另外,在图4所示的例子中,在未对第一mr元件50a施加对象磁场的情况下,第一及第二电阻部r11、r12各自中的自由层54的磁化包含第三磁化方向(v方向)的分量。在未对第一mr元件50a施加对象磁场的情况下,第三及第四电阻部r13、r14各自中的磁化固定层52的

磁化包含第四磁化方向(-v方向)的分量。

[0066]

此外,在磁化固定层52的磁化包含特定的磁化方向的分量的情况下,特定的磁化方向的分量也可以是磁化固定层52的磁化的主分量。或者,磁化固定层52的磁化也可以不含与特定的磁化方向正交的方向的分量。在本实施方式中,在磁化固定层52的磁化包含特定的磁化方向的分量的情况下,磁化固定层52的磁化的方向成为特定的磁化方向或大致特定的磁化方向。

[0067]

同样,在未对自由层54施加对象磁场的情况下的自由层54的磁化包含特定的磁化方向的分量的情况下,特定的磁化方向的分量也可以是自由层54的磁化的主分量。或者,上述的情况下的自由层54的磁化也可以不含与特定的磁化方向正交的方向的分量。在本实施方式中,在上述的情况下的自由层54的磁化包含特定的磁化方向的分量的情况下,上述的情况下的自由层54的磁化的方向成为特定的磁化方向或大致特定的磁化方向。

[0068]

第一检测电路10构成为,在未对第一检测电路10施加对象磁场的情况下,自由层54的磁化成为上述的方向。具体而言,第一检测电路10的多个第一mr元件50a各自的自由层54具有易磁化轴方向成为与第三磁化方向(v方向)平行的方向的形状各向异性。此外,与第三磁化方向(v方向)平行的方向也是与第四磁化方向(-v方向)平行的方向。

[0069]

在第二检测电路20中,第一磁化方向是w1方向,第二磁化方向是-w1方向,第三磁化方向是u方向,第四磁化方向是-u方向。如果将第一检测电路10中的磁化固定层52的磁化的方向及自由层54的磁化的方向的说明中的、第一检测电路10、电阻部r11、r12、r13、r14、第一mr元件50a、u方向、-u方向、v方向及-v方向分别替换为第二检测电路20、电阻部r21、r22、r23、r24、第二mr元件50b、w1方向、-w1方向、u方向及-u方向,则成为第二检测电路20中的磁化固定层52的磁化的方向及自由层54的磁化的方向的说明。

[0070]

在第三检测电路30中,第一磁化方向是w2方向,第二磁化方向是-w2方向,第三磁化方向是u方向,第四磁化方向是-u方向。如果将第一检测电路10中的磁化固定层52的磁化的方向及自由层54的磁化的方向的说明中的、第一检测电路10、电阻部r11、r12、r13、r14、第一mr元件50a、u方向、-u方向、v方向及-v方向分别替换为第三检测电路30、电阻部r31、r32、r33、r34、第三mr元件50c、w2方向、-w2方向、u方向及-u方向,则成为第三检测电路30中的磁化固定层52的磁化的方向及自由层54的磁化的方向的说明。

[0071]

磁传感器1包含磁场产生器,该磁场产生器构成为对多个第一mr元件50a、多个第二mr元件50b、以及多个第三mr元件50c各自的自由层54施加规定的方向的磁场。在本实施方式中,磁场产生器包含:对第一mr元件50a各自的自由层54施加规定方向的磁场的第一线圈70、对多个第二mr元件50b和多个第三mr元件50c各自的自由层54施加规定方向的磁场的第二线圈80。第一芯片2包含第一线圈70。第二芯片3包含第二线圈80。

[0072]

以下,详细地说明第一芯片2和第二芯片3的具体结构。首先,参照图7及图8对第一芯片2的结构进行说明。图8表示在图7中由8-8线表示的位置的截面的一部分。

[0073]

第一芯片2包含:具有上表面201a的基板201、绝缘层202、203、204、207、208、209、210、多个下部电极61a、多个上部电极62a、多个下部线圈要素71、以及多个上部线圈要素72。基板201的上表面201a设为与xy平面平行。z方向也是与基板201的上表面201a垂直的一方向。此外,线圈要素是线圈的绕阻的一部分。

[0074]

绝缘层202配置在基板201之上。多个下部线圈要素71配置在绝缘层202之上。绝缘

层203在绝缘层202之上配置于多个下部线圈要素71的周围。绝缘层204配置在多个下部线圈要素71及绝缘层203之上。

[0075]

多个下部电极61a配置在绝缘层204之上。绝缘层207在绝缘层204之上配置于多个下部电极61a的周围。多个第一mr元件50a配置在多个下部电极61a之上。绝缘层208在多个下部电极61a及绝缘层207之上配置于多个第一mr元件50a的周围。多个上部电极62a配置在多个第一mr元件50a及绝缘层208之上。绝缘层209在绝缘层208之上配置于多个上部电极62a的周围。

[0076]

绝缘层210配置在多个上部电极62a及绝缘层209之上。多个上部线圈要素72配置在绝缘层210之上。第一芯片2也可以还包含覆盖多个上部线圈要素72及绝缘层210的未图示的绝缘层。此外,在图7中,示出第一芯片2的构成要素中的绝缘层204、多个第一mr元件50a及多个上部线圈要素72。

[0077]

基板201的上表面201a与xy平面平行,多个下部电极61a各自的上表面也与xy平面平行。因此,在上述的状态下,可以说多个第一mr元件50a配置在与xy平面平行的平面之上。

[0078]

如图7所示,多个第一mr元件50a以沿u方向和v方向分别各多个地排列的方式排列。多个第一mr元件50a通过多个下部电极61a和多个上部电极62a串联连接。此外,在从z方向观察时,相邻的两个第一mr元件50a可以沿与v方向平行的方向错开,也可以不错开。

[0079]

在此,参照图11,详细地说明多个第一mr元件50a的连接方法。在图11中,符号61表示与任意的mr元件50对应的下部电极,符号62表示与任意的mr元件50对应的上部电极。如图11所示,各个下部电极61具有细长的形状。在下部电极61的长边方向上相邻的两个下部电极61之间形成有间隙。在下部电极61的上表面上,在长边方向的两端的附近分别配置有mr元件50。另外,各个上部电极62具有细长的形状,将配置于在下部电极61的长边方向上相邻的两个下部电极61上而相邻的两个mr元件50彼此电连接。

[0080]

虽然未图示,但位于排列成一列的多个mr元件50的列的一端的一个mr元件50与位于在与下部电极61的长边方向交叉的方向上相邻的其它的多个mr元件50的列的一端的另一个mr元件50连接。这两个mr元件50通过未图示的电极相互连接。未图示的电极也可以是将两个mr元件50的下表面彼此或上表面彼此连接的电极。

[0081]

在图11所示的mr元件50为第一mr元件50a的情况下,图11所示的下部电极61与下部电极61a对应,图11所示的上部电极62与上部电极62a对应。另外,在该情况下,下部电极61的长边方向成为与v方向平行的方向。

[0082]

此外,在本实施方式中,将包含反铁磁性层51、磁化固定层52、间隙层53及自由层54的层叠膜作为mr元件50进行说明。但是,也可以将具备该层叠膜、下部电极61以及上部电极62的部件作为本实施方式中的mr元件。层叠膜包含多个磁性膜。

[0083]

多个上部线圈要素72各自向与y方向平行的方向延伸。另外,多个上部线圈要素72以沿x方向排列的方式排列。在本实施方式中,特别是在从z方向观察时,两个上部线圈要素72与多个第一mr元件50a的各个重叠。

[0084]

多个下部线圈要素71各自向与y方向平行的方向延伸。另外,多个下部线圈要素71以沿x方向排列的方式排列。多个下部线圈要素71的形状及排列可以与多个上部线圈要素72的形状及排列相同,也可以不同。

[0085]

在图7及图8所示的例子中,多个下部线圈要素71和多个上部线圈要素72以构成对

多个第一mr元件50a各自的自由层54施加与x方向平行的方向的磁场的第一线圈70的方式电连接。另外,第一线圈70也可以构成为,例如能够对第一及第二电阻部r11、r12中的自由层54施加x方向的磁场,且对第三及第四电阻部r13、r14中的自由层54施加-x方向的磁场。另外,第一线圈70也可以被处理器40控制。

[0086]

接下来,参照图9及图10,对第二芯片3的结构进行说明。图10表示在图9中以10-10线表示的位置的截面的一部分。

[0087]

第二芯片3包含具有上表面301a的基板301、绝缘层302、303、304、305、307、308、309、310、多个下部电极61b、多个下部电极61c、多个上部电极62b、多个上部电极62c、多个下部线圈要素81、以及多个上部线圈要素82。基板301的上表面301a设为与xy平面平行。z方向也是与基板301的上表面301a垂直的一方向。

[0088]

绝缘层302配置在基板301之上。多个下部线圈要素81配置在绝缘层302之上。绝缘层303在绝缘层302之上配置于多个下部线圈要素81的周围。绝缘层304,305依次层叠在多个下部线圈要素81及绝缘层303之上。

[0089]

多个下部电极61b和多个下部电极61c配置在绝缘层305之上。绝缘层307在绝缘层305之上配置于多个下部电极61b的周围和多个下部电极61c的周围。多个第二mr元件50b配置在多个下部电极61b之上。多个第三mr元件50c配置在多个下部电极61c之上。绝缘层308在多个下部电极61b、多个下部电极61c及绝缘层307之上配置于多个第二mr元件50b的周围和多个第三mr元件50c的周围。多个上部电极62b配置在多个第二mr元件50b及绝缘层308之上。多个上部电极62c配置在多个第三mr元件50c及绝缘层308之上。绝缘层309在绝缘层308之上配置于多个上部电极62b的周围和多个上部电极62c的周围。

[0090]

绝缘层310配置在多个上部电极62b、多个上部电极62c及绝缘层309之上。多个上部线圈要素82配置在绝缘层310之上。第二芯片3也可以还包含覆盖多个上部线圈要素82及绝缘层310的未图示的绝缘层。

[0091]

第二芯片3包含支撑多个第二mr元件50b和多个第三mr元件50c的支撑部件。支撑部件具有相对于基板301的上表面301a倾斜的至少一个倾斜面。在本实施方式中,特别是支撑部件由绝缘层305构成。此外,在图9中,示出第二芯片3的构成要素中的、绝缘层305、多个第二mr元件50b、多个第三mr元件50c及多个上部线圈要素82。

[0092]

绝缘层305具有分别向远离基板301的上表面301a的方向(z方向)伸出的多个凸面305c。多个凸面305c各自向与u方向平行的方向延伸。凸面305c的整体形状是使图10所示的凸面305c的三角形形状沿着与u方向平行的方向移动而成的三角屋顶形状。另外,多个凸面305c沿与v方向平行的方向排列。

[0093]

多个凸面305c各自具有离基板301的上表面301a最远的上端部。在本实施方式中,多个凸面305c各自的上端部向与u方向平行的方向延伸。在此,着眼于多个凸面305c中的任意一个凸面305c。凸面305c包含第一倾斜面305a和第二倾斜面305b。第一倾斜面305a是凸面305c中比凸面305c的上端部靠v方向侧的面。第二倾斜面305b是凸面305c中比凸面305c的上端部靠-v方向侧的面。凸面305c的上端部也可以是第一倾斜面305a和第二倾斜面305b的边界。

[0094]

基板301的上表面301a与xy平面平行。第一倾斜面305a和第二倾斜面305b各自相对于基板301的上表面301a即xy平面倾斜。在与基板301的上表面301a垂直的截面上,第一

倾斜面305a和第二倾斜面305b的间隔随着远离基板301的上表面301a而减小。

[0095]

在本实施方式中,因为存在多个凸面305c,所以第一倾斜面305a和第二倾斜面305b也分别存在多个。绝缘层305具有多个第一倾斜面305a和多个第二倾斜面305b。

[0096]

绝缘层305包含分别向z方向突出的多个突出部。多个突出部各自向与u方向平行的方向延伸。凸面305c由绝缘层305的上表面构成。另外,多个突出部沿与v方向平行的方向排列。

[0097]

多个下部电极61b配置在多个第一倾斜面305a之上。多个下部电极61c配置在多个第二倾斜面305b之上。如上所述,因为第一倾斜面305a和第二倾斜面305b各自相对于基板301的上表面301a即xy平面倾斜,所以多个下部电极61b各自的上表面和多个下部电极61c各自的上表面也相对于xy平面倾斜。因此,可以说多个第二mr元件50b和多个第三mr元件50c配置在相对于xy平面倾斜的倾斜面上。绝缘层305是用于将多个第二mr元件50b和多个第三mr元件50c的各个以相对于xy平面倾斜的方式支撑的部件。

[0098]

在本实施方式中,多个第一倾斜面305a各自是与u方向和w1方向平行的平面。多个第二倾斜面305b各自是与u方向和w2方向平行的平面。

[0099]

虽然未图示,但绝缘层305还具有存在于多个凸面305c的周围的平坦面。多个凸面305c也可以从平坦面向z方向突出。另外,多个凸面305c也可以以在相邻的两个凸面305c之间形成有平坦面的方式隔开规定的间隔而配置。或者,绝缘层305也可以具有从平坦面朝向-z方向凹陷的槽部。在该情况下,多个凸面305c也可以存在于槽部内。

[0100]

另外,凸面305c也可以是使曲线形状(拱形状)沿着与u方向平行的方向移动而成的半圆筒状的曲面。在该情况下,第一倾斜面305a成为曲面。第二mr元件50b沿着曲面(第一倾斜面305a)弯曲。即使在该情况下,方便起见,第二mr元件50b的磁化固定层52的磁化的方向也如上所述定义为直线性的方向。同样,第二倾斜面305b成为曲面。第三mr元件50c沿着曲面(第二倾斜面305b)弯曲。即使在该情况下,方便起见,第三mr元件50c的磁化固定层52的磁化的方向也如上所述定义为直线性的方向。

[0101]

如图9所示,多个第二mr元件50b以沿u方向和v方向分别各多个地排列的方式排列。在一个第一倾斜面305a之上,多个第二mr元件50b排列成一列。同样,多个第三mr元件50c以沿u方向和v方向分别各多个地排列的方式排列。在一个第二倾斜面305b之上,多个的第三mr元件50c排列成一列。在本实施方式中,多个第二mr元件50b的列和多个第三mr元件50c的列在与v方向平行的方向上交替排列。

[0102]

此外,在从z方向观察时,相邻的一个第二mr元件50b和一个第三mr元件50c可以沿与u方向平行的方向错开,也可以不错开。另外,在从z方向观察时,隔着一个第三mr元件50c而相邻的两个第二mr元件50b也可以沿与u方向平行的方向错开,也可以不错开。另外,在从z方向观察时,隔着一个第二mr元件50b而相邻的两个第三mr元件50c可以沿与u方向平行的方向错开,也可以不错开。

[0103]

多个第二mr元件50b通过多个下部电极61b和多个上部电极62b串联连接。上述的关于多个第一mr元件50a的连接方法的说明也适用于多个第二mr元件50b的连接方法。在图11所示的mr元件50为第二mr元件50b的情况下,图11所示的下部电极61与下部电极61b对应,图11所示的上部电极62与上部电极62b对应。另外,在该情况下,下部电极61的长边方向成为与u方向平行的方向。

[0104]

同样,多个第三mr元件50c通过多个下部电极61c和多个上部电极62c串联连接。上述的关于多个第一mr元件50a的连接方法的说明也适用于多个第三mr元件50c的连接方法。在图11所示的mr元件50为第三mr元件50c的情况下,图11所示的下部电极61与下部电极61c对应,图11所示的上部电极62与上部电极62c对应。另外,在该情况下,下部电极61的长边方向成为与u方向平行的方向。

[0105]

多个上部线圈要素82各自向与y方向平行的方向延伸。另外,多个上部线圈要素82以沿x方向排列的方式排列。在本实施方式中。特别是在从z方向观察时,两个上部线圈要素82与多个第二mr元件50b和多个第三mr元件50c的各个重叠。

[0106]

多个下部线圈要素81各自向与y方向平行的方向延伸。另外,多个下部线圈要素81以沿x方向排列的方式排列。多个下部线圈要素81的形状及排列可以与多个上部线圈要素82的形状及排列相同,也可以不同。

[0107]

在图9及图10所示的例子中,多个下部线圈要素81和多个上部线圈要素82以构成对多个第二mr元件50b和多个第三mr元件50c各自的自由层54施加与x方向平行的方向的磁场的第二线圈80的方式电连接。另外,第二线圈80也可以构成为,例如能够对第二检测电路20的第一及第二电阻部r21、r22和第三检测电路30的第一及第二电阻部r31、r32中的自由层54施加x方向的磁场,且对第二检测电路20的第三及第四电阻部r23、r24和第三检测电路30的第三及第四电阻部r33、r34中的自由层54施加-x方向的磁场。另外,第二线圈80也可以被处理器40控制。

[0108]

接下来,对第一~第三检测信号进行说明。首先,参照图4,对第一检测信号进行说明。当对象磁场的与u方向平行的方向的分量的强度变化时,第一检测电路10的电阻部r11~r14各自的电阻值以如下方式变化:随着电阻部r11、r13的电阻值增加而电阻部r12、r14的电阻值减少,或随着电阻部r11、r13的电阻值减少而电阻部r12、r14的电阻值增加。由此,信号输出端e11、e12各自的电位变化。第一检测电路10构成为将与信号输出端e11的电位对应的信号作为第一检测信号s11生成,将与信号输出端e12的电位对应的信号作为第一检测信号s12生成。

[0109]

接下来,参照图5,对第二检测信号进行说明。当对象磁场的与w1方向平行的方向的分量的强度变化时,第二检测电路20的电阻部r21~r24各自的电阻值以如下方式变化:随着电阻部r21、r23的电阻值增加而电阻部r22、r24的电阻值减少,或随着电阻部r21、r23的电阻值减少而电阻部r22、r24的电阻值。由此,信号输出端e21、e22各自的电位变化。第二检测电路20构成为将与信号输出端e21的电位对应的信号作为第二检测信号s21生成,将与信号输出端e22的电位对应的信号作为第二检测信号s22生成。

[0110]

接下来,参照图6,对第三检测信号进行说明。当对象磁场的与w2方向平行的方向的分量的强度变化时,第三检测电路30的电阻部r31~r34各自的电阻值以如下方式变化:随着电阻部r31、r33的电阻值增加而电阻部r32、r34的电阻值减少,或随着电阻部r31、r33的电阻值减少而电阻部r32、r34的电阻值增加。由此,信号输出端e31、e32各自的电位变化。第三检测电路30构成为将与信号输出端e31的电位对应的信号作为第三检测信号s31生成,将与信号输出端e32的电位对应的信号作为第三检测信号s32生成。

[0111]

接下来,对处理器40的结构及动作进行说明。处理器40构成为,基于第一检测信号s11、s12生成第一检测值,且基于第二检测信号s21、s22及第三检测信号s31、s32生成第二

检测值和第三检测值。第一检测值是与对象磁场的与u方向平行的方向的分量对应的检测值。第二检测值是与对象磁场的与v方向平行的方向的分量对应的检测值。第三检测值是与对象磁场的与z方向平行的方向的分量对应的检测值。以下,由记号su表示第一检测值,由记号sv表示第二检测值,由记号sz表示第三检测值。

[0112]

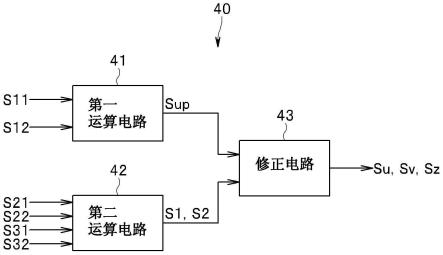

图12是表示处理器40的结构的功能框图。处理器40包含第一运算电路41、第二运算电路42以及修正电路43。第一运算电路41构成为执行第一生成处理。第一生成处理是使用第一检测信号s11、s12生成与第一检测值su对应的第一初始检测值sup的处理。

[0113]

在本实施方式中,第一运算电路41通过包括求出第一检测信号s11和第一检测信号s12之差s11-s12的运算,生成第一初始检测值sup。第一初始检测值sup可以是差s11-s12其本身,也可以是对差s11-s12施加了增益调整及偏移调整等规定的修正的值。

[0114]

第二运算电路42构成为执行第二生成处理中的至少一部分的处理。第二生成处理包括生成与第二检测值sv对应的第二初始检测值svp的处理和生成与第三检测值sz对应的第三初始检测值szp的处理。在生成第二初始检测值svp的处理中,至少使用第二检测信号s21、s22。在本实施方式中,在生成第二初始检测值svp的处理和生成第三初始检测值szp的处理的任一处理中均使用第二检测信号s21、s22和第三检测信号s31、s32。

[0115]

在本实施方式中,第二生成处理包括第一处理、第二处理以及第三处理。第一处理是使用第二检测信号s21、s22生成第一值s1的处理。第二处理是使用第三检测信号s31、s32生成第二值s2的处理。第三处理是使用第一值s1和第二值s2生成第二初始检测值svp和第三初始检测值szp的处理。

[0116]

在本实施方式中,特别是第二运算电路42构成为执行第一处理和第二处理。第一处理是通过包括求出第二检测信号s21和第二检测信号s22之差s21-s22的运算而生成第一值s1的处理。第二处理是通过包括求出第三检测信号s31和第三检测信号s32之差s31-s32的运算而生成第二值s2的处理。

[0117]

第三处理包括使用下述的式(1)、(2)计算值s3、s4的处理。

[0118]

s3=(s2+s1)/(2cosα)

……

(1)

[0119]

s4=(s2-s1)/(2sinα)

……

(2)

[0120]

第三处理还包括使用值s3、s4生成第二及第三初始检测值svp、szp的处理。通过第三处理生成的第二初始检测值svp可以是值s3其本身,也可以是对值s3施加了增益调整及偏移调整等规定的修正的值。同样,通过第三处理生成的第三初始检测值szp可以是值s4其本身,也可以是对值s4施加了增益调整及偏移调整等规定的修正的值。

[0121]

修正电路43使用第一~第三初始检测值sup、svp、szp生成第一~第三检测值su、sv、sz。在本实施方式中,特别是修正电路43构成为为了生成第一~第三检测值su、sv、sz而执行第二生成处理的第三处理、第一修正处理、第二修正处理以及确定处理。

[0122]

在第一修正处理中,第一初始检测值sup更新一次以上。以下,将最后更新的第一初始检测值sup称为最新的第一初始检测值sup。此外,方便起见,也将执行第一生成处理之后且执行第一次的第一修正处理之前的第一初始检测值sup称为最新的第一初始检测值sup。

[0123]

在第二修正处理中,第二初始检测值svp和第三初始检测值szp各自更新一次以上。以下,将最后更新的第二初始检测值svp称为最新的第二初始检测值svp,将最后更新的

第三初始检测值szp称为最新的第三初始检测值szp。

[0124]

第一修正处理是使用根据最新的第二初始检测值svp生成的第二修正值svc来修正第一初始检测值sup(最新的第一初始检测值sup)并更新第一初始检测值sup的处理。

[0125]

第二修正值svc也可以是通过包括最新的第二初始检测值svp乘以第二修正系数的运算而算出的值。以下,将最后算出的第二修正值svc称为最新的第二修正值svc。第一修正处理也可以是通过在使用第一初始检测值sup和第二修正值svc表示的式子中代入最新的第一初始检测值sup和最新的第二修正值svc来计算(更新)第一初始检测值sup的处理。上述的式子也可以是包括第一运算和第二运算的式子,上述第一运算包括最新的第一初始检测值sup乘以第二修正值svc,上述第二运算将通过第一运算获得的值加到最新的第一初始检测值sup或将其从最新的第一初始检测值sup减去。

[0126]

第二修正处理是使用根据最新的第一初始检测值sup生成的第一修正值suc来修正第二初始检测值svp(最新的第二初始检测值svp)和第三初始检测值szp(最新的第三初始检测值szp)并更新第二及第三初始检测值svp、szp的处理。在本实施方式中,特别是第二修正处理包括第四处理、第五处理以及第六处理。第四处理是使用第一修正值suc来修正第一及第二值s1、s2并更新第一及第二值s1、s2的处理。第五处理是使用最新的第一及第二值s1、s2生成第二及第三初始检测值svp、szp的处理。第六处理是使用通过第五处理生成的第二及第三初始检测值svp、szp更新第二及第三初始检测值svp、szp的处理。此外,最新的第一值s1是指最后更新的第一值s1。另外,最新的第二值s2是指最后更新的第二值s2。方便起见,执行第一及第二处理之后且执行第一次的第三处理之前的第一值s1及第二值s2也分别被称为最新的第一值s1及最新的第二值s2。

[0127]

第五处理的内容实质上与第二生成处理的第三处理相同。即,第二修正处理实质上包括第二生成处理的第三处理。第五处理包括使用最新的第一及第二值s1、s2和式(1)、(2)计算值s3、s4的处理和使用值s3、s4生成第二及第三初始检测值svp、szp的处理。

[0128]

第一修正值suc也可以是通过包括最新的第一初始检测值sup乘以第一修正系数的运算而算出的值。以下,将最后算出的第一修正值suc称为最新的第一修正值suc。第二修正处理的第四处理也可以是如下处理:通过在使用第一值s1和第一修正值suc表示的第一式中代入最新的第一值s1和最新的第一修正值suc来计算(更新)第一值s1,通过在使用第二值s2和第一修正值suc表示的第二式中代入最新的第二值s2和最新的第一修正值suc来计算(更新)第二值s2。第一式也可以是包括第三运算和第四运算的式子,上述第三运算包括最新的第一值s1乘以第一修正值suc,上述第四运算将通过第三运算获得的值加到最新的第一值s1或将其从最新的第一值s1减去。第二式也可以是包括第五运算和第六运算的式子,上述第五运算包括最新的第二值s2乘以第一修正值suc,上述第六运算将通过第五运算获得的值加到最新的第二值s2或将其从最新的第二值s2减去。

[0129]

确定处理是如下处理:将最新的第一初始检测值sup确定为第一检测值su,将最新的第二初始检测值svp确定为第二检测值sv,将最新的第三初始检测值szp确定为第三检测值sz。修正电路43在将第一修正处理和第二修正处理交替执行一次以上之后,执行确定处理。修正电路43可以将第一修正处理及第二修正处理分别各一次地执行,也可以分别各两次地执行,也可以分别各三次以上地执行。

[0130]

修正电路43也可以自第二及第三初始检测值svp、szp的更新起先执行。即,修正电

路43也可以在执行第一次的第一修正处理之前执行第一次的第二修正处理。

[0131]

第一次的第二修正处理在执行第二生成处理的第一及第二处理之后执行。另外,如上所述,第二修正处理实质上包括第二生成处理的第三处理。因此,通过执行第一次的第二修正处理,实质上执行第二生成处理。

[0132]

此外,处理器40的结构不限于图12所示的例子。例如,第一运算电路41、第二运算电路42及修正电路43实质上也可以是一个电路。在该情况下,一个电路也可以构成为能够执行由第一运算电路41、第二运算电路42及修正电路43执行的所有处理。或者也可以构成为,取代设置修正电路43,而是第一运算电路41执行修正电路43执行的一部分的处理(与第一初始检测值sup及第一检测值su相关的处理),第二运算电路42执行修正电路43执行的其它的一部分的处理(与第二及第三初始检测值svp、szp以及第二及第三检测值sv、sz相关的处理)。在该情况下,也可以构成为能够在第一运算电路41和第二运算电路42之间收发第一及第二初始检测值sup、svp。

[0133]

接下来,对由修正电路43执行的一系列的处理的效果进行说明。首先,对比较例的第一~第三检测电路进行说明。比较例的第一检测电路的结构除了未对多个第一mr元件50a施加对象磁场的情况下的、多个第一mr元件50a各自的自由层54的磁化的方向之外,与图4所示的第一检测电路10的结构相同。在比较例的第一检测电路中,在上述的情况下,自由层54的磁化的方向在多个第一mr元件50a的全部中为v方向。

[0134]

比较例的第二检测电路的结构除了未对多个第二mr元件50b施加对象磁场的情况下的、多个第二mr元件50b各自的自由层54的磁化的方向之外,与图5所示的第二检测电路20的结构相同。在比较例的第二检测电路中,在上述的情况下,自由层54的磁化的方向在多个第二mr元件50b的全部中为u方向。

[0135]

比较例的第三检测电路的结构除了未对多个第三mr元件50c施加对象磁场的情况下的、多个第三mr元件50c各自的自由层54的磁化的方向之外,与图6所示的第三检测电路30的结构相同。在比较例的第三检测电路中,在上述的情况下,自由层54的磁化的方向在多个第三mr元件50c的全部中为u方向。

[0136]

在比较例的第一检测电路中,与v方向平行的方向的磁场(对象磁场的与v方向平行的方向的分量)实质上具有使基于易磁化轴方向成为与v方向平行的方向的形状各向异性的各向异性磁场变化的作用。该各向异性磁场作用于自由层54的磁化。因此,在比较例的第一检测电路中,检测对象磁场的与u方向平行的方向的分量时的自由层54的磁化的方向根据与v方向平行的方向的磁场的有无或其强度的变化而变化。由此,第一检测信号s11、s12在不存在与v方向平行的方向的磁场的状态下从检测到对象磁场的与u方向平行的方向的分量时的第一检测信号s11、s12偏离,其结果,实质上相当于第一检测值su的差s11-s12也会偏离。

[0137]

与此相对,在本实施方式中,使自由层54的磁化的方向针对每个电阻部而不同。在本实施方式中,特别是设定自由层54的磁化的方向,以使得能够在计算差s11-s12时抵消与v方向平行的方向的磁场所引起的第一检测信号s11、s12的偏离。由此,根据本实施方式,能够抑制与v方向平行的方向的磁场所引起的差s11-s12的偏离。其结果,根据本实施方式,能够减小与v方向平行的方向的磁场所引起的第一检测值su的误差。

[0138]

对于上述的比较例的第一检测电路的说明也适用于比较例的第二及第三检测电

路。在比较例的第二检测电路中,第二检测信号s21、s22在不存在与u方向平行的方向的磁场的状态下从检测到对象磁场的与w1方向平行的方向的分量时的第二检测信号s21、s22偏离,其结果,第一值s1也会偏离。另外,在比较例的第三检测电路中,第三检测信号s31、s32在不存在与u方向平行的方向的磁场的状态下从检测到对象磁场的与w2方向平行的方向的分量时的第三检测信号s31、s32偏离,其结果,第二值s2也会偏离。因此,实质上相当于第二检测值sv的值s3和实质上相当于第三检测值sz的值s4也会偏离。与此相对,根据本实施方式,能够抑制与u方向平行的方向的磁场所引起的值s3、s4的偏离。其结果,根据本实施方式,能够减小与u方向平行的方向的磁场所引起的第二及第三检测值sv、sz的误差。

[0139]

由修正电路43执行的一系列处理是用于进一步抑制如上所述被抑制的差s11-s12的偏离即第一初始检测值sup的偏离、值s3的偏离即第二初始检测值svp的偏离、以及值s4的偏离即第三初始检测值szp的偏离的处理。在第一修正处理中,使用与对象磁场的与v方向平行的方向的分量的强度具有对应关系的第二初始检测值svp来修正第一初始检测值sup。能够通过使用第二初始检测值svp而根据与v方向平行的方向的磁场的有无或其强度的变化,修正第一初始检测值sup。具体而言,因为第二修正值svc根据与v方向平行的方向的磁场的有无或其强度的变化而变化,所以能够高精度地修正第一初始检测值sup。

[0140]

第二修正系数或使用上述的第一初始检测值sup和第二修正值svc表示的式子也可以被规定为,随着第一初始检测值sup的偏离变大而第一初始检测值sup的修正量变大,并且第一初始检测值sup的修正量的正负根据第一初始检测值sup以减少的方式偏离的情况和以增加的方式偏离的情况而改变。例如,在第一初始检测值sup以减少的方式偏离的情况下,也可以将相当于第一初始检测值sup的减少量的第一初始检测值sup的修正量与第一初始检测值sup相加。另外,在第一初始检测值sup以增加的方式偏离的情况下,也可以将相当于第一初始检测值sup的增加量的第一初始检测值sup的修正量从第一初始检测值sup减去。

[0141]

对于第一修正处理的上述的说明也适用于第二修正处理。即,在第二修正处理中,使用与对象磁场的与u方向平行的方向的分量的强度具有对应关系的第一初始检测值sup来修正第一及第二值s1、s2。由此,实质上,使用与对象磁场的与u方向平行的方向的分量的强度具有对应关系的第一初始检测值sup来修正第二及第三初始检测值svp、szp。能够通过使用第一初始检测值sup而根据与u方向平行的方向的磁场的有无或其强度的变化,修正第一及第二值s1、s2(第二及第三初始检测值svp、szp)。具体而言,因为第一修正值suc根据与u方向平行的方向的磁场的有无或其强度的变化而变化,所以能够高精度地修正第一及第二值s1、s2(第二及第三初始检测值svp、szp)。

[0142]

第一修正系数或上述的第一及第二式也可以被规定为,随着第二初始检测值svp的偏离变大而第二初始检测值svp的修正量变大,并且第二初始检测值svp的修正量的正负根据第二初始检测值svp以减少的方式偏离的情况和以增加的方式偏离的情况而改变。

[0143]

也可以预先选择第一修正系数和第二修正系数,以抑制第一初始检测值sup的偏离、第二初始检测值svp的偏离以及第三初始检测值szp的偏离。第一修正系数和第二修正系数也可以基于多个测定结果,使用数值分析等而确定。

[0144]

此外,如果想要对由比较例的第一~第三检测电路生成的第一~第三初始检测值sup、svp、szp应用第一及第二修正处理,则需要根据施加的磁场的方向进行第一及第二修

正系数的正负的变更等、第一及第二修正处理的内容的变更。与此相对,在本实施方式中,能够不论施加的磁场的方向如何而应用相同的第一及第二修正处理,能够简化修正电路43的结构及第一及第二修正处理的内容。

[0145]

然而,作为抑制第一~第三初始检测值sup、svp、szp各自的偏离的方法,考虑设置由磁性材料构成的屏蔽件,以使得不对第一~第三检测电路10、20、30的各个施加检测对象以外的磁场。例如,考虑在第一检测电路10设置屏蔽件,该屏蔽件构成为使与u方向平行的方向的磁场几乎不衰减,但使与v方向平行的方向的磁场遮断或衰减。同样,考虑在第二及第三检测电路20、30设置屏蔽件,该屏蔽件构成为使与w1方向平行的方向的磁场及与w2方向平行的方向的磁场几乎不衰减,但使与u方向平行的方向的磁场遮断或衰减。但是,在本实施方式中,不在第一~第三检测电路10、20、30的各个设置屏蔽件而抑制第一~第三初始检测值sup、svp、szp各自的偏离。由此,根据本实施方式,能够简化磁传感器1的结构。

[0146]

另外,在本实施方式中,第一初始检测值sup使用第一检测信号s11、s12生成,上述第一检测信号s11、s12通过检测对象磁场的与基准平面4a即xy平面平行的方向的分量(对象磁场的与u方向平行的方向的分量)而生成。第二及第三初始检测值svp、szp使用第二检测信号s21、s22及第三检测信号s31、s32生成,上述第二检测信号s21、s22及第三检测信号s31、s32通过检测对象磁场的相对于基准平面4a即xy平面倾斜的一方向的分量(对象磁场的与w1方向平行的方向的分量)和对象磁场的相对于基准平面4a即xy平面倾斜的另一方向的分量(对象磁场的与w2方向平行的方向的分量)而生成。这样,在本实施方式中,其特征在于,抑制通过检测对象磁场的与xy平面平行的方向的分量和相对于xy平面倾斜的方向的分量而生成的第一~第三初始检测值sup、svp、szp各自的偏离。

[0147]

此外,如上所述,在本实施方式中,与对象磁场的与u方向平行的方向的分量对应的检测值(第一初始检测值sup)通过检测对象磁场的与u方向平行的方向的分量而生成,但与对象磁场的与v方向平行的方向的分量对应的检测值(第二初始检测值svp)不通过检测对象磁场的与v方向平行的方向的分量而生成,与对象磁场的与z方向平行的方向的分量对应的检测值(第三初始检测值szp)也不通过检测对象磁场的与z方向平行的方向的分量而生成。因此,在本实施方式中,有时与第二及第三初始检测值svp、szp相比,能够高精度地生成第一初始检测值sup。在该情况下,在执行第一修正处理之前,通过执行使用第一初始检测值sup的第二修正处理,能够高精度地更新第一~第三初始检测值sup、svp、szp。

[0148]

另外,在本实施方式中,生成第一检测信号s11、s12的第一检测电路10包含于第一芯片2,生成第二检测信号s21、s22的第二检测电路20和生成第三检测信号s31、s32的第三检测电路30包含于第二芯片3。这样,在本实施方式中,其特征在于,抑制使用物理上相互分离的两个芯片各自所含的检测电路而生成的第一~第三初始检测值sup、svp、szp各自的偏离。

[0149]

接下来,对于调查第二检测值sv的误差的模拟结果进行说明。在模拟中,对磁传感器装置100施加至少包含u方向的分量和v方向的分量的对象磁场,生成第一~第三检测值su、sv、sz。此外,在模拟中,以第一~第三检测值su、sv、sz分别表示对象磁场的与u方向平行的方向的分量的强度、对象磁场的与v方向平行的方向的分量的强度及对象磁场的与z方向平行的方向的分量的强度的方式修正差s11-s12及值s3、s4,生成第一~第三初始检测值sup、svp、szp。另外,在模拟中,在执行第一次的第一修正处理之前,执行第一次的第二修

正处理。

[0150]

在模拟中,每当将第二修正处理和第一修正处理交替执行一次,执行确定处理,生成第一~第三检测值su、sv、sz。另外,将对象磁场的v方向的分量的强度和第二检测值sv之差除以对象磁场的v方向的分量的强度所得的值作为第二检测值sv的误差求出。

[0151]

另外,在模拟中,在执行第一及第二修正处理之前执行第二生成处理的第三处理,求出第二初始检测值svp,并根据该第二初始检测值svp求出第一及第二修正处理各自的执行次数为零次时的第二检测值sv的误差。即,将对象磁场的v方向的分量的强度和上述的第二初始检测值svp之差除以对象磁场的v方向的分量的强度所得的值作为第一及第二修正处理各自的执行次数为零次时的第二检测值sv的误差求出。第一及第二修正处理各自的执行次数为零次时的第二检测值sv的误差为3.54%。

[0152]

另外,第一及第二修正处理各自的执行次数为一次时的第二检测值sv的误差为0.13%。另外,第一及第二修正处理各自的执行次数为两次时和为三次时的第二检测值sv的误差均为0%。

[0153]

根据模拟的结果可理解,通过将第一及第二修正处理分别执行一次,能够减小第二检测值sv的误差。另外,通过将第一及第二修正处理分别执行两次,能够将第二检测值sv的误差设为大致0。此外,即使将第一及第二修正处理分别执行三次,第二检测值sv的误差也为大致0。从处理器40的负荷的观点来看,第一及第二修正处理各自的执行次数优选为两次。

[0154]

上述的关于第二检测值sv的说明也适用于第一检测值su及第三检测值sz。

[0155]

[第二实施方式]

[0156]

接下来,对本发明的第二实施方式的磁传感器装置进行说明。在本实施方式中,mr元件50的自由层54的磁化的方向与第一实施方式不同。

[0157]

以下,使用在第一实施方式中定义的第一~第四磁化方向,对mr元件50的自由层54的磁化的方向进行说明。图13是表示第一检测电路10的电路结构的电路图。图14是表示第二检测电路20的电路结构的电路图。图15是表示第三检测电路30的电路结构的电路图。

[0158]

与第一实施方式同样地,在第一检测电路10中,第一磁化方向为u方向,第二磁化方向为-u方向,第三磁化方向为v方向,第四磁化方向为-v方向。在本实施方式中,在未对第一mr元件50a施加对象磁场的情况下,第一及第四电阻部r11、r14各自中的自由层54的磁化包含第三磁化方向(v方向)的分量。在未对第一mr元件50a施加对象磁场的情况下,第二及第三电阻部r12、r13各自中的自由层54的磁化包含第四磁化方向(-v方向)的分量。

[0159]

另外,在本实施方式中,第一线圈70(参照图3)也可以构成为,例如能够对第一及第四电阻部r11、r14中的自由层54施加x方向的磁场,并对第二及第三电阻部r12、r13中的自由层54施加-x方向的磁场。

[0160]

另外,与第一实施方式同样地,在第二检测电路20中,第一磁化方向为w1方向,第二磁化方向为-w1方向,第三磁化方向为u方向,第四磁化方向为-u方向。在本实施方式中,在未对第二mr元件50b施加对象磁场的情况下,第一及第四电阻部r21、r24各自中的自由层54的磁化包含第三磁化方向(u方向)的分量。在未对第二mr元件50b施加对象磁场的情况下,第二及第三电阻部r22、r23各自中的自由层54的磁化包含第四磁化方向(-u方向)的分量。

[0161]

另外,与第一实施方式同样地,在第三检测电路30中,第一磁化方向为w2方向,第二磁化方向为-w2方向,第三磁化方向为u方向,第四磁化方向为-u方向。在本实施方式中,在未对第三mr元件50c施加对象磁场的情况下,第一及第四电阻部r31、r34各自中的自由层54的磁化包含第三磁化方向(u方向)的分量。在未对第三mr元件50c施加对象磁场的情况下,第二及第三电阻部r32、r33各自中的自由层54的磁化包含第四磁化方向(-u方向)的分量。

[0162]

另外,在本实施方式中,第二线圈80(参照图3)也可以构成为,例如能够对第二检测电路20的第一及第四电阻部r21、r24和第三检测电路30的第一及第四电阻部r31、r34中的自由层54施加x方向的磁场,且对第二检测电路20的第二及第三电阻部r22、r23和第三检测电路30的第二及第三电阻部r32、r33中的自由层54施加-x方向的磁场。

[0163]

本实施方式的其它结构、作用及效果与第一实施方式相同。

[0164]

[第三实施方式]

[0165]

接下来,对本发明的第三实施方式进行说明。本实施方式的磁传感器装置100由本实施方式的磁传感器101和在第一实施方式中说明的处理器40构成。磁传感器101也可以具有与第一实施方式的第一芯片2或第二芯片3同样的外观形状。

[0166]

以下,参照图16~图19,对本实施方式的磁传感器101的结构进行说明。图16是表示本实施方式的磁传感器装置100的结构的功能框图。图17是表示本实施方式的第一检测电路的电路结构的电路图。图18是表示本实施方式的第二检测电路的电路结构的电路图。图19是表示本实施方式的第三检测电路的电路结构的电路图。

[0167]

磁传感器101具备第一检测电路110、第二检测电路120以及第三检测电路130。第一~第三检测电路110、120、130各自包含多个mr元件。

[0168]

第一检测电路110构成为检测对象磁场的与u方向平行的方向的分量,生成与该分量具有对应关系的第一检测信号s111、s112。第二检测电路120构成为检测对象磁场的与v方向平行的方向的分量,生成与该分量具有对应关系的第二检测信号s121、s122。第三检测电路130构成为检测对象磁场的与z方向平行的方向的分量,生成与该分量具有对应关系的第三检测信号s131、s132。

[0169]

第一检测电路110的电路结构基本上与第一实施方式的第一检测电路10的电路结构相同。在图17中,分别由符号r111、r112、r113、r114表示与第一检测电路10的第一~第四电阻部r11、r12、r13、r14对应的第一检测电路110的第一~第四电阻部。

[0170]

第二检测电路120的电路结构基本上与第一实施方式的第二检测电路20的电路结构相同。在图18中,分别由符号r121、r122、r123、r124表示与第二检测电路20的第一~第四电阻部r21、r22、r23、r24对应的第二检测电路120的第一~第四电阻部。

[0171]

第三检测电路130的电路结构基本上与第一实施方式的第三检测电路30的电路结构相同。在图19中,分别由符号r131、r132、r133、r134表示与第三检测电路30的第一~第四电阻部r31、r32、r33、r34对应的第三检测电路130的第一~第四电阻部。

[0172]

电阻部r111~r114、r121~r124、r131~r134由多个mr元件构成。以下,将磁传感器101的多个mr元件以符号150表示。mr元件150的结构也可以与在第一实施方式中说明的mr元件50的结构相同。即,mr元件150至少具有磁化固定层52、自由层54及间隙层53(参照图11)。

[0173]

在图17~图19中,实心箭头表示mr元件150的磁化固定层52的磁化的方向。在图17所示的例子中,第一及第三电阻部r111、r113各自中的磁化固定层52的磁化的方向为u方向。第二及第四电阻部r112、r114各自中的磁化固定层52的磁化的方向为-u方向。另外,第一检测电路110的多个mr元件150各自的自由层54具有易磁化轴方向成为与v方向平行的方向的形状各向异性。

[0174]

在图18所示的例子中,第一及第三电阻部r121、r123各自中的磁化固定层52的磁化的方向为v方向。第二及第四电阻部r122、r124各自中的磁化固定层52的磁化的方向为-v方向。另外,第二检测电路120的多个mr元件150各自的自由层54具有易磁化轴方向成为与u方向平行的方向的形状各向异性。

[0175]

第三检测电路130的多个mr元件150各自的自由层54具有易磁化轴方向成为与v方向平行的方向的形状各向异性。后面说明第三检测电路130中的磁化固定层52的磁化的方向。

[0176]

接下来,对磁传感器101的具体结构进行说明。磁传感器101包含具有上表面的基板、包含第一检测电路110的第一部分、包含第二检测电路120的第二部分、以及包含第三检测电路130的第三部分。基板的上表面设为与xy平面平行。第一~第三部分形成在基板之上。第一部分的结构和第二部分的结构与在第一实施方式中说明的第一芯片2(除基板201之外)的结构相同。第一部分中所含的多个mr元件150分别具有在v方向上长的形状。第二部分中所含的多个mr元件150分别具有在u方向上长的形状。此外,第一及第二部分可以包含在第一实施方式中说明的第一线圈70,也可以不包含。

[0177]

接下来,参照图20及图21,对磁传感器101的第三部分的结构进行说明。图20是表示多个mr元件150和多个磁轭的立体图。图21是表示多个mr元件150和多个磁轭的侧视图。

[0178]

第三部分的结构基本上与第一部分的结构相同。第三部分还包含分别由软磁性体构成的多个磁轭151。多个磁轭151各自也可以具有在v方向上长的长方体形状。多个磁轭151各自构成为接收包含与z方向平行的方向的输入磁场分量的输入磁场并产生输出磁场。输出磁场包含与u方向平行的方向的输出磁场分量、即根据输入磁场分量而变化的输出磁场分量。

[0179]

多个磁轭151各自具有位于与u方向平行的方向的两端的第一端面151a及第二端面151b。在多个磁轭151各自中,第一端面151a位于磁轭151的-u方向的一端,第二端面151b位于磁轭151的u方向的一端。另外,多个磁轭151沿与u方向平行的方向排列。

[0180]

如图20及图21所示,在第三部分中,多个mr元件150沿着第一端面150a排列成一列,并且多个mr元件150沿着第二端面150b排列成一列。以下,由符号150a表示沿着第一端面150a排列的多个mr元件150,由符号150b表示沿着第二端面150b排列的多个mr元件150。在第三部分中,多个mr元件150a及多个mr元件150b以排列成一列的mr元件150a的列和排列成一列的mr元件150b的列沿与u方向平行的方向交替排列的方式排列。在从上方观察时,多个mr元件150a和多个mr元件150b也可以不与多个磁轭151重叠。

[0181]

虽然未图示,但第三部分还包含多个第一下部电极、多个第二下部电极、多个第一上部电极以及多个第二上部电极。多个mr元件150a通过多个第一下部电极及多个第一上部电极串联连接。多个mr元件150b通过多个第二下部电极及多个第二上部电极串联连接。

[0182]

接下来,详细地说明多个磁轭151。在输入磁场分量的方向为z方向的情况下,多个

mr元件150a各自接收的输出磁场分量的方向成为u方向,多个mr元件150b各自接收的输出磁场分量的方向成为-u方向。在输入磁场分量的方向为-z方向的情况下,多个mr元件150a各自接收的输出磁场分量的方向成为-u方向,多个mr元件150b各自接收的输出磁场分量的方向成为u方向。

[0183]

接下来,对本实施方式的第一~第三检测信号进行说明。首选,对第一检测信号进行简单说明。第一检测电路110的电阻部r111~r114各自的电阻值的变化的方式与在第一实施方式中说明的第一检测电路10的电阻部r11~r14各自的电阻值的变化的方式相同。第一检测电路110构成为将与信号输出端e11的电位对应的信号作为第一检测信号s111生成,将与信号输出端e12的电位对应的信号作为第一检测信号s112生成。

[0184]

接下来,参照图18,对第二检测信号进行说明。当对象磁场的与v方向平行的方向的分量的强度变化时,第二检测电路120的电阻部r121~r124各自的电阻值以如下方式变化:随着电阻部r121、r123的电阻值增加而电阻部r122、r124的电阻值减少,或随着电阻部r121、r123的电阻值减少而电阻部r122、r124的电阻值增加。由此,信号输出端e21、e22各自的电位变化。第二检测电路120构成为将与信号输出端e21的电位对应的信号作为第二检测信号s121生成,将与信号输出端e22的电位对应的信号作为第二检测信号s122生成。

[0185]

接下来,参照图19~图21,对第三检测信号进行说明。第一电阻部r131和第二电阻部r132由多个mr元件150a构成。第三电阻部r133和第四电阻部r134由多个mr元件150b构成。

[0186]

在此,将配置有构成第三检测电路130的多个mr元件150的一个区域分割成第一区域和第二区域。构成第一电阻部r131的多个mr元件150a和构成第四电阻部r134的多个mr元件150b也可以配置于第一区域。构成第二电阻部r132的多个mr元件150a和构成第三电阻部r133的多个mr元件150b也可以配置于第二区域。

[0187]

第一及第四电阻部r131、r134各自中的磁化固定层52的磁化的方向为u方向。第二及第三电阻部r132、r133各自中的磁化固定层52的磁化的方向为-u方向。

[0188]

在输入磁场分量的方向为z方向的情况下,第一及第二电阻部r131、r132内的多个mr元件150a接收的输出磁场分量的方向成为u方向,第三及第四电阻部r133、r134内的多个mr元件150b接收的输出磁场分量的方向成为-u方向。在该情况下,与不存在输出磁场分量的状态相比,第一电阻部r131内的多个mr元件150a和第三电阻部r133内的多个mr元件150b各自的电阻值减少,第一及第三电阻部r131、r133各自的电阻值也减少。另外,与不存在输出磁场分量的状态相比,第二电阻部r132内各自的mr元件150a和第四电阻部r134内的多个mr元件150b各自的电阻值增加,第二及第四电阻部r132、r134的电阻值也增加。

[0189]

在输入磁场分量的方向为-z方向的情况下,输出磁场分量的方向和第一~第四电阻部r131~r134的电阻值的变化与上述的输入磁场分量的方向为z方向的情况相反。

[0190]

这样,当输入磁场分量的方向和强度变化时,第三检测电路130的电阻部r131~r134各自的电阻值以如下方式变化:随着电阻部r131、r133的电阻值增加而电阻部r132、r134的电阻值减少,或随着电阻部r131、r133的电阻值减少而电阻部r132、r134的电阻值增加。由此,信号输出端e31、e32各自的电位变化。第三检测电路130构成为将与信号输出端e31的电位对应的信号作为第三检测信号s131生成,将与信号输出端e32的电位对应的信号作为第三检测信号s132生成。

[0191]

接下来,对本实施方式的处理器40的结构及动作进行说明。图22是表示本实施方式的处理器40的结构的功能框图。在本实施方式中,处理器40构成为,基于第一检测信号s111、s112生成与对象磁场的与u方向平行的方向的分量对应的第一检测值su,基于第二检测信号s121、s122生成与对象磁场的与v方向平行的方向的分量对应的第二检测值sv,基于第三检测信号s131、s132生成与对象磁场的与z方向平行的方向的分量对应的第三检测值sz。

[0192]

本实施方式的处理器40取代第一实施方式的第一及第二运算电路而包含第一运算电路141、第二运算电路142以及第三运算电路143。第一运算电路141构成为执行第一生成处理。本实施方式的第一生成处理的内容与第一实施方式相同。即,本实施方式的第一生成处理是使用第一检测信号s111、s112生成与第一检测值su对应的第一初始检测值sup的处理。第一运算电路141通过包括求出第一检测信号s111和第一检测信号s112之差s111-s112的运算而生成第一初始检测值sup。第一初始检测值sup可以是差s111-s112其本身,也可以是对差s111-s112施加了增益调整及偏移调整等规定的修正的值。

[0193]

第二运算电路142构成为执行第二生成处理。本实施方式的第二生成处理的内容与第一实施方式不同。本实施方式的第二生成处理是使用第二检测信号s121、s122生成与第二检测值sv对应的第二初始检测值svp的处理。第二运算电路142通过包括求出第二检测信号s121和第二检测信号s122之差s121-s122的运算而生成第二初始检测值svp。第二初始检测值svp可以是差s121-s122其本身,也可以是对差s121-s122施加了增益调整及偏移调整等规定的修正的值。

[0194]

第三运算电路143构成为执行第三生成处理。第三生成处理是使用第三检测信号s131、s132生成第三检测值sz的处理。第三运算电路143通过包括求出第三检测信号s131和第三检测信号s132之差s131-s132的运算而生成第三检测值sz。第三检测值sz可以是差s131-s132其本身,也可以是对差s131-s132施加了增益调整及偏移调整等规定的修正的值。

[0195]

另外,在本实施方式中,修正电路43构成为不生成第三检测值sz。另外,在本实施方式中,确定处理的内容与第一实施方式不同。本实施方式的确定处理包括确定第一检测值su和第二检测值sv的处理,但不包括确定第三检测值sz的处理。

[0196]

另外,在本实施方式中,修正电路43在交替执行第一修正处理和第二修正处理之后,执行确定处理。修正电路43可以将第一修正处理和第二修正处理分别各一次地执行,也可以分别各两次地执行,也可以分别各三次以上地执行。另外,修正电路43也可以自第二初始检测值svp的更新起先执行。即,修正电路43也可以在执行第一次的第一修正处理之前执行第一次的第二修正处理。

[0197]

本实施方式的其它结构、作用及效果与第一实施方式相同。

[0198]

此外,本发明不限于上述各实施方式,能够进行各种变更。例如,本发明的磁传感器也可以使第一芯片2和第二芯片3一体化。

[0199]

另外,第二芯片3也可以取代第二及第三检测电路20、30而仅包含构成为检测对象磁场的与v方向平行的方向的分量的第二检测电路。或者,第二芯片3也可以取代第二及第三检测电路20、30而包含构成为检测对象磁场的与v方向平行的方向的分量的第二检测电路和构成为检测对象磁场的与z方向平行的方向的分量的第三检测电路。

[0200]

另外,第一实施方式的第二运算电路42也可以构成为除了第二生成处理的第一及第二处理之外还能够执行第二生成处理的第三处理。在该情况下,修正电路43也可以取代第一及第二值s1、s2而使用由第二运算电路42生成的第二及第三初始检测值svp、szp来执行第二修正处理。第二修正处理也可以是如下处理:通过在使用第二初始检测值svp和第一修正值suc表示的第一式中代入最新的第二初始检测值svp和最新的第一修正值suc来计算(更新)第二初始检测值svp,通过在使用第三初始检测值szp和第一修正值suc表示的第二式中代入最新的第三初始检测值szp和最新的第一修正值suc来计算(更新)第三初始检测值szp。第一式也可以是包含包括最新的第二初始检测值svp乘以第一修正值suc的运算和将通过该运算获得的值加到最新的第二初始检测值svp或将其从最新的第二初始检测值svp减去的运算的式子。第二式也可以是包含包括最新的第三初始检测值szp乘以第一修正值suc的运算和将通过该运算获得的值加到最新的第三初始检测值szp或将其从最新的第三初始检测值szp减去的运算的式子。

[0201]

如上所述,本发明的磁传感器装置具备:第一检测电路,其构成为检测作为检测对象的磁场的对象磁场的一方向的分量,并生成第一检测信号;第二检测电路,其构成为检测对象磁场的另一方向的分量,并生成第二检测信号;处理器。

[0202]

处理器构成为执行如下处理:第一生成处理,使用第一检测信号生成第一初始检测值;第二生成处理,使用第二检测信号生成第二初始检测值;第一修正处理,使用根据最新的第二初始检测值生成的第二修正值来修正第一初始检测值,并更新第一初始检测值;第二修正处理,使用根据最新的第一初始检测值生成的第一修正值来修正第二初始检测值,并更新第二初始检测值;确定处理,将最新的第一初始检测值确定为与平行于第一基准方向的对象磁场的分量具有对应关系的第一检测值,并且将最新的第二初始检测值确定为与平行于第二基准方向的对象磁场的分量具有对应关系的第二检测值。处理器在交替执行第一修正处理和第二修正处理之后执行确定处理。

[0203]

在本发明的磁传感器装置中,处理器也可以将第一修正处理和第二修正处理分别各两次地执行。

[0204]

另外,在本发明的磁传感器装置中,处理器也可以在执行第一次的第一修正处理之前,执行第一次的第二修正处理。

[0205]

另外,在本发明的磁传感器装置中,第一修正值也可以是通过包括最新的第一初始检测值乘以第一修正系数的运算而算出的值。第二修正值也可以是通过包括最新的第二初始检测值乘以第二修正系数的运算而算出的值。

[0206]

另外,在本发明的磁传感器装置中,第一检测电路和第二检测电路各自也可以包含:第一磁阻效应元件及第二磁阻效应元件,其在将第一节点和第二节点电连接的路径即第一路径上串联连接;第三磁阻效应元件及第四磁阻效应元件,其在将第一节点和第二节点电连接的其它路径即第二路径上串联连接。第一磁阻效应元件和第四磁阻效应元件也可以与第一节点连接。第二磁阻效应元件和第三磁阻效应元件也可以与第二节点连接。第一~第四磁阻效应元件各自也可以包含具有方向被固定的第一磁化的磁化固定层、具有方向可根据对象磁场而变化的第二磁化的自由层、以及配置于磁化固定层和自由层之间的间隙层。第一磁阻效应元件中的第一磁化的主分量的方向和第三磁阻效应元件中的第一磁化的主分量的方向也可以是相同方向。第二磁阻效应元件中的第一磁化的主分量的方向和第四

磁阻效应元件中的第一磁化的主分量的方向也可以是相同方向。第二磁阻效应元件中的第一磁化的主分量的方向也可以是与第一磁阻效应元件中的第一磁化的主分量的方向相反的方向。第四磁阻效应元件中的第一磁化的主分量的方向也可以是与第三磁阻效应元件中的第一磁化的主分量的方向相反的方向。在未对第一及第二检测电路施加对象磁场的情况下,第一~第四磁阻效应元件中的两个磁阻效应元件各自中的第二磁化的主分量的方向也可以是与第一~第四磁阻效应元件中的其它两个磁阻效应元件各自中的第二磁化的主分量的方向相反的方向。间隙层也可以是隧道势垒层。

[0207]

另外,在本发明的磁传感器装置中,也可以在第一检测电路和第二检测电路的各个不设置屏蔽件。

[0208]

另外,在本发明的磁传感器装置中,第一基准方向和第二基准方向也可以均与基准平面平行且相互正交。

[0209]

另外,在本发明的磁传感器装置中,第一检测电路检测的对象磁场的分量的方向也可以是与基准平面平行的方向。第二检测电路检测的对象磁场的分量的方向也可以是相对于基准平面倾斜的方向。

[0210]

另外,也可以是本发明的磁传感器装置还具备第三检测电路,并且第三检测电路构成为检测相对于基准平面倾斜并且与第二检测电路检测的对象磁场的分量的方向不同的方向的对象磁场的分量,并生成第三检测信号。第二生成处理也可以是使用第二检测信号和第三检测信号来生成第二初始检测值和第三初始检测值的处理。第二修正处理也可以是使用第一修正值来修正第二初始检测值和第三初始检测值并更新第二初始检测值和第三初始检测值的处理。确定处理也可以还将最新的第三初始检测值确定为与垂直于基准平面的对象磁场的分量具有对应关系的第三检测值。

[0211]

在本发明的磁传感器装置具备第三检测电路的情况下,第二生成处理也可以包括使用第二检测信号生成第一值的第一处理、使用第三检测信号生成第二值的第二处理、以及使用第一值和第二值生成第二初始检测值和第三初始检测值的第三处理。第二修正处理也可以实质上包括第三处理。在该情况下,处理器也可以在执行第一处理和第二处理之后依次执行第一次的第二修正处理和第一次的第一修正处理。另外,第二修正处理也可以包括使用第一修正值修正第一值和第二值的第四处理、使用通过第四处理修正的第一值和第二值生成第二初始检测值和第三初始检测值的第五处理、以及使用通过第五处理生成的第二初始检测值和第三初始检测值更新第二初始检测值和第三初始检测值的第六处理。

[0212]

在本发明的磁传感器装置具备第三检测电路的情况下,第一~第三检测电路各自也可以包含:第一磁阻效应元件及第二磁阻效应元件,其在将第一节点和第二节点电连接的路径即第一路径上串联连接;第三磁阻效应元件及第四磁阻效应元件,其在将第一节点和第二节点电连接的其它路径即第二路径上串联连接。第一磁阻效应元件和第四磁阻效应元件也可以与第一节点连接。第二磁阻效应元件和第三磁阻效应元件也可以与第二节点连接。第一~第四磁阻效应元件各自也可以包含具有方向被固定的第一磁化的磁化固定层、具有方向可根据对象磁场而变化的第二磁化的自由层、以及配置于磁化固定层和自由层之间的间隙层。第一磁阻效应元件中的第一磁化的主分量的方向和第三磁阻效应元件中的第一磁化的主分量的方向也可以是相同方向。第二磁阻效应元件中的第一磁化的主分量的方向和第四磁阻效应元件中的第一磁化的主分量的方向也可以是相同方向。第二磁阻效应元

件中的第一磁化的主分量的方向也可以是与第一磁阻效应元件中的第一磁化的主分量的方向相反的方向。第四磁阻效应元件中的第一磁化的主分量的方向也可以是与第三磁阻效应元件中的第一磁化的主分量的方向相反的方向。在未对第一~第三检测电路施加对象磁场的情况下,第一~第四磁阻效应元件中的两个磁阻效应元件各自中的第二磁化的主分量的方向也可以是与第一~第四磁阻效应元件中的其它的两个磁阻效应元件各自中的第二磁化的主分量的方向相反的方向。间隙层也可以是隧道势垒层。

[0213]

另外,在本发明的磁传感器装置具备第三检测电路的情况下,也可以在第一~第三检测电路的各个不设置屏蔽件。

[0214]

另外,在本发明的磁传感器装置具备第三检测电路的情况下,本发明的磁传感器装置也可以还具备包含第一检测电路的第一芯片和包含第二检测电路及第三检测电路的第二芯片。

[0215]

另外,也可以是本发明的磁传感器装置还具备第三检测电路,并且第三检测电路构成为检测与基准平面垂直的对象磁场的分量并生成第三检测信号。第一检测电路检测的对象磁场的分量的方向也可以是与基准平面平行的第一方向。第二检测电路检测的对象磁场的分量的方向也可以是与基准平面平行的第二方向。第二生成处理也可以是使用第二检测信号和第三检测信号生成第二初始检测值和第三检测值的处理。第三检测值也可以与垂直于基准平面的对象磁场的分量具有对应关系。

[0216]

基于以上的说明可知,能够实施本发明的各种方式或变形例。因此,在权利要求书的等同的范围内,即使是上述的最佳方式以外的方式,也能够实施本发明。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1