一种串扰测试组件和串扰测试方法与流程

1.本技术属于量子芯片制备领域,具体涉及一种串扰测试组件和串扰测试方法。

背景技术:

2.随着量子比特数目的增加,在量子芯片制备过程中,量子比特的各种相应控制线路和测量线路也会不断增加。考虑到量子芯片的有限空间,这些线路之间很可能会产生不同程度的彼此影响,例如串扰,特别是在高频情况下其将表现的尤为突出。

3.因此,为了抑制这样的串扰,常常需要对比特结构或其读取、控制线路进行优化设计。

4.另外,一些实践中还会选择配置用于抑制串扰的结构。那么就需要考察这些结构所能够产生的抑制效果。为了获得可以产生更理想效果的结构,需要对以不同形式构造的串扰抑制结构进行试验。例如,针对不同形式的抑制结构方案,选择不同的试验方案。

5.那么就可能会导致需要验证和考察的方案较多,而对应各个结构单独地配置相应的测试方案又是繁杂和高成本(如耗费更多的测试资源)的。并且在诸如超导量子芯片的领域中,需要配置低温环境以及在线路中配置各种射频元件;同时由于量子芯片中的串扰信号相对较弱,而量子比特的信号也较弱,从而使得极低的串扰也需要被慎重地对待。

6.因此,如何高效、便利地对串扰抑制结构进行方案验证就是一个亟待解决的问题。

技术实现要素:

7.有鉴于此,本技术公开了一种串扰测试组件和串扰测试方法。其能够简化串扰抑制元件的性能测试过程、提高测试效率以及测试资源的利用率。

8.本技术示例的方案,通过如下内容实施。

9.在第一方面,本技术的示例提出了一种串扰测试组件,其包括:第一线路;与第一线路耦合的至少三条第二线路,沿着第一线路的延伸轨迹间隔地分布,至少三条第二线路包括基准线路和至少两条对照线路;以及与至少两条对照线路一一对应的至少两个串扰抑制单元,每个串扰抑制单元包括至少一个抑制元件;抑制元件设置于第一线路和至少两条对照线路的耦合区域,并且被配置为弱化第一线路和对照线路之间的串扰。

10.在该串扰测试组件中,相互耦合的第一线路和第二线路提供信号的传输、产生串扰以及与抑制元件相互影响的环境。并且,其中部分第二线路(对照线路)配置串扰抑制单元,同时部分的第二线路(基准线路)未予以配置。因此在第一线路和第二线路传输信号的同时进行信号的测量,比对不同的第二线路的测量值将可以获得是否配置串扰抑制单元以及配置不同形式的串扰抑制单元所产生的对串扰的作用和影响的结果,进而能够据此评估抑制元件的配置方式的优劣,并且也有助于验证和开发串扰抑制方案。

11.另外,根据需要,第二线路中可以配置多条对照线路,并且因此可以进行多种方案的测试,而不需要针对每个设计方案为其配置独立的测试资源,从而提高资源利用率。

12.根据本技术的一些示例,抑制元件与第一线路和第二线路均未接触,且包括空气桥、超导元件。其中的抑制元件包括应用于倒装芯片中的倒装互连结构。示例性地,互连结构为铟柱。进一步地,铟柱被设置于第一线路和对照线路之间。

13.根据本技术的一些示例,串扰抑制单元具有关联于弱化程度的特征参数,特征参数包括抑制元件的数量、形状、尺寸和位置中的任意一个或多个的组合。

14.根据本技术的一些示例,抑制元件包括空气桥,且空气桥跨接第一线路的两侧;或者,抑制元件包括空气桥,且空气桥跨接对照线路的两侧。

15.根据本技术的一些示例,抑制元件包括空气桥;串扰抑制单元的数量为至少三个,且其中至少一个串扰抑制单元的全部空气桥跨接第一线路的两侧,至少一个串扰抑制单元的全部空气桥跨接对照线路的两侧,至少一个串扰抑制单元的全部空气桥中的部分跨接第一线路的两侧且剩余部分跨接对照线路的两侧。

16.根据本技术的一些示例,同一个串扰抑制单元中的各个空气桥具有相同的形状和尺寸;和/或,不同的串扰抑制元件中的空气桥具有相同的形状和不同的尺寸。

17.根据本技术的一些示例,第一线路是应用于超导量子芯片的读取总线,基准线路和对照线路是与读取总线耦合的读取谐振腔。

18.根据本技术的一些示例,第一线路是应用于超导量子芯片的微波控制线,基准线路和对照线路是应用于超导量子芯片的通量控制线。

19.在第二方面,本技术的示例提出了一种串扰测试方法,其包括:提供前述的串扰测试组件;测定第一线路和基准线路之间的第一耦合强度,以及测定第一线路和对照线路之间的第二耦合强度;比较第一耦合强度和第二耦合强度,以确定抑制元件弱化串扰的程度。

20.在第三方面,本技术的示例提出了一种串扰测试方法,其包括:提供前述之串扰测试组件,且第一线路为读取总线,基准线路和对照线路为读取谐振腔时;测定并比较各个读取谐振腔的品质因数,以确定抑制元件弱化串扰的性能。

21.有益效果:与现有技术相比,本技术的串扰测试组件能够在相对更简便的配置情况下实现多项目的测试,从而能够助于提高抑制元件的测试效率和测试资源的利用率。

附图说明

22.为了更清楚地说明本技术实施例或现有技术中的技术方案,以下将对实施例或现有技术描述中所需要使用的附图作简单地介绍。

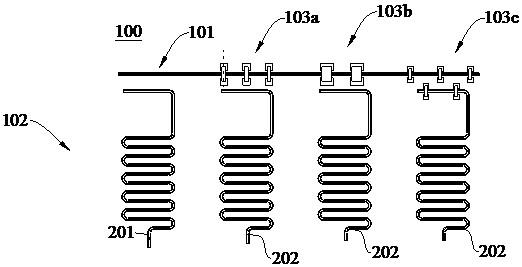

23.图1为本技术实施例提供的第一种串扰测试组件的结构示意图;图2公开了图1的串扰测试组件中的一个串扰抑制单元中的抑制元件的一种剖视结构示意图;

图3公开了本技术示例中的具有按照铟柱的形式构建的抑制元件的串扰测试组件的结构示意图;图4为本技术实施例提供的串扰测试方法的流程示意图。

24.图标:100-串扰测试组件;300-串扰测试组件;101-第一线路;102-第二线路;103a-第一抑制单元;103b-第二抑制单元;103c-第三抑制单元;201-基准线路;202-对照线路;301a-第一抑制单元;301b-第二抑制单元;301c-第三抑制单元;311-桥墩;312-桥体。

具体实施方式

25.在倒装芯片的制作过程中,芯片使用焊接凸块而非焊线固定在基材或称载体上,以提供密集的互连。因此,倒装芯片具有很优异的电气性能和热性能。

26.在常规的芯片封装技术中,晶片与载体之间采用细线进行互连。具体地,晶片的背面(正面朝上)贴装到载体上;其中的细线则会先连接晶片,然后再焊接到载体。相对地,倒装封装的晶片和载体采用凸块进行互连。其中,在晶片的表面配置导电的凸块。然后,再将带有凸块的晶片“翻转过来”,正面朝下放置,凸块连接到载体。在硅基芯片中,例如,凸块被选择为铜。此外,为了防止凸块对晶片的不利影响,在凸块和晶片之间还通常会配置中间层,例如被称之为凸点下金属层(under-bump metal,简称ubm)ubm的结构。

27.因倒装互连技术的优势,其同样被应用于量子芯片中。其不仅可以提高量子芯片的集成度,还避免了量子芯片中的量子比特数目增加时其平面尺寸增加太快。因此,有鉴于单个芯片中配置越来越多的量子比特,在超导量子芯片的制作过程中,倒装互连技术被选择使用并被寄予厚望。

28.当前,在基于倒装互连技术的超导量子芯片中,习惯上,其中的晶片被描述为上层芯片,而载体可以被描述为下层芯片。同时,上下层芯片各自还根据设计需要选择性地配置量子比特、读取线路、控制线路或各种元件等。目前,上下层芯片之间的互连件一般选择为铟柱。

29.在本技术发明人的研究中,除了作为信号的传输通道之外,互连件还被用于改善线路之间的信号串扰。例如,设置到超导量子比特的控制线之间的铟柱,其能够抑制超导量子比特的控制线之间的串扰。并且由于相邻控制线之间加入了铟柱,那么在一定串扰程度下,控制线之间的距离可以被压缩,从而可以为芯片中的其他元件留出更多的空间。

30.因此,在上述情况中,如何准确地评估串扰以确定串扰抑制结构的性能就成为了一个需要被慎重地考虑的问题。

31.基于上述的现实需求,于本技术的示例中,发明人提出了一种串扰测试组件。大体上,该串扰测试组件通过构建彼此耦合的两种元件,并且通过考察串扰抑制结构对二者的串扰的削弱作用来评估串扰抑制结构的性能。

32.例如,在彼此耦合的第一元件和第二元件之间传输信号时,可能存在被测量到的串扰。当为第二元件配置串扰抑制结构之后,再进行串扰测量,如果此时根据测量值获得的串扰相比于未配置串扰抑制结构时根据测量值获得的串扰变得更小了,则可以认为该串扰抑制结构起到了抑制串扰的作用。并且,在实际的操作中,串扰的测试可以通过衡量两元件之间的耦合作用,即耦合强弱,来判断串扰程度。

33.进一步地,当在超导量子芯片中,例如,第一元件配置为读取总线,而第二元件配

置为读取谐振腔时,还可以通过确定读取谐振腔的品质因子来衡量串扰。例如,读取谐振腔的品质因子越高,则表明能量泄露越小;换言之,读取谐振腔与读取总线的耦合作用越小,则串扰也越小,且反之亦然。

34.示例中,如图1所示,串扰测试组件100包括第一线路101和第二线路102,且第二线路102包括多条,例如至少三条。其中,至少一条第二线路102被作为基准线路201,而至少两条第二线路102则被作为对照线路202。其中“基准”和“对照”作为区别两线路的使用目的而被命名,而并非意在限定二者必须存在任何有意为之的结构或性能区别。并且,相反,对照线路和基准线路之间不存在结构和性能等方面的差距,将更有助于通过测试结果进行比对并判断串扰抑制元件的抑制性能。

35.实践中,基准线路201和对照线路202可以按照相同的结构、材质以及工艺被制作而成,使得二者各自与第一线路101之间具有相同的耦合作用表现或根据设计需求可以接受的差距范围之内的耦合作用表现。示例性地,当第一线路101为读取总线,第二线路102为多个读取谐振腔的集合时,各个读取谐振腔的腔频率可以相同或者虽然存在差距,但是差距很小(例如差距小于50mhz)。例如,四个读取谐振腔的腔频率可以分别为6.50ghz、6.55ghz、6.60ghz和6.65ghz。

36.除此之外,串扰测试组件中还包括串扰抑制单元。其用于弱化第一线路101和第二线路102之间的串扰,即弱化两条线路之间的耦合作用。并且,串扰抑制单元的数量与对照线路202的数量是一致的;二者一一对应。即一个串扰抑制单元与一条对照线路202对应。

37.每条对照线路202,在其与第一线路的耦合区域范围内,对应地配置一个串扰抑制单元。也即,其中串扰抑制单元的配置位置是在第一线路101和对照线路202的耦合区域的。顾名思义,串扰抑制单元是用来弱化第一线路101和对照线路202之间的串扰的。

38.进一步地,串扰抑制单元具有各种选择数量的抑制元件,例如一个、两个、三个、四个等等。通常地,抑制元件是多个的,其遍及到第一线路与第二线路耦合范围内的整个耦合长度区域。

39.作为示例,抑制元件可以是空气桥或超导元件。其中的超导元件例如是倒装芯片中的互连结构,示例性地包括铟柱。

40.当抑制元件是空气桥时,空气桥可以跨接第一线路101、或者空气桥跨接对照线路202。部分实例中,全部空气桥跨接第一线路101;另一些示例中全部空气桥跨接对照线路202;又一些示例中全部的空气桥中的部分跨接第一线路101,并且剩余部分跨接对照线路202。

41.其中的跨接是指,空气桥的隆起部分位于相应的线路之上。或者说,从空气桥的一端至第二端的第一方向,前述之隆起部分与第一线路101的延伸轨迹的第二方向是彼此纵横交错的。

42.作为示例,空气桥可以具有桥墩、引桥和桥面(或称为桥顶);并且,桥面的两端分别与一个引桥连接,每个引桥还连接一个桥墩。则空气桥的两端(桥墩)结合到芯片的接地平面。

43.引桥隆起,且逐渐远离芯片的表面;引桥终止于一定的相对于芯片的表面的高度。桥面连接到引桥,且大致平行于芯片的表面延伸。桥面延伸一定长度后,再与引桥连接。引桥延伸逐渐接近芯片的表面,然后与结合到芯片的表面的接地平面的桥墩连接。或者,如图

2所示,空气桥包括桥墩311和桥体312;即前述的引桥和桥面结合为桥体312,且大致呈拱形。

44.上文主要阐述了空气桥形式的抑制元件。另一些示例中,当抑制元件为应用于倒装芯片中的倒装互连结构—即铟柱—时,抑制元件可以配置到第一线路101和对照线路202之间。铟柱通常被构造为大致的圆柱形结构,且具有适当的高度(一般大于上下层芯片之间的间距)。

45.在实践中,发明人发现,抑制元件的数量、位置、材质、形状、尺寸等均可能独立或两个以上的组合对弱化串扰的性能产生影响。

46.以第一线路101为超导量子芯片中的读取总线,第二线路102中的基准线路201和对照线路202为超导量子芯片中的读取谐振腔为例。在图1中,读取总线为一条,且可以采用共面波导传输线;一条基准线路201和三条对照线路202为以相同材料和结构按照相同工艺制作而成的共面波导谐振腔(可以是1/4波长谐振腔,或者1/2波长谐振腔)。

47.请参阅图1,读取总线沿水平方向延伸布置,并因此具有在该方向的延伸轨迹。一条基准线路201和三条对照线路202共四条线路沿着水平方向依次间隔地分布。其中任意两条第二线路之间具有大致相同的距离。

48.对应于三条对照线路202,图1所示的串扰测试组件100包括三个串扰抑制单元。其中第一抑制单元103a具有三个空气桥;每个空气桥跨接读取总线的两侧。第二抑制单元103b具有两个空气桥;每个空气桥跨接读取总线的两侧。第三抑制单元103c具有五个空气桥;其中三个空气桥跨接读取总线的两侧,其中两个空气桥跨接读取谐振腔。

49.在图1所示的串扰测试组件中,三个抑制单元具有不同的抑制元件数量、相同的抑制元件形状和相同的材质,但是尺寸不同。因此,测定四个读取谐振腔的品质因子,然后再进行比对可以获得感兴趣的结果,例如哪种尺寸和数量的空气桥可以更好地弱化串扰。

50.示例性地,将基准线路201的品质因子,与各个对照线路202的品质因子进行比对,或者将任意两个对照线路202的品质因子进行比对,即可对空气桥对串扰的弱化效果进行评价,进而确定哪种空气桥配置方案—即哪种串扰抑制单元—性能更优。其中品质因子的测量方式例如是采用探针台、网络分析仪进行s参数/散射参数(如测s21)测试,然后通过变换关系计算获得品质因子即q值。

51.类似地,图3公开了具有按照铟柱的形式构建的抑制元件的串扰测试组件300。该串扰测试组件300与图1中的串扰测试组件100的主要区别在于:图1和图3中的串扰抑制单元不同,且构成串扰抑制单元的抑制元件不同。

52.其中,第一抑制单元301a具有五个铟柱,并且依次呈线性等间距排布。第二抑制单元301b具有四个铟柱,并且依次呈线性等间距排布。第三抑制单元301c具有十个铟柱,并且以五个为一组依次呈线性等间距排布,两组成行地排列,且在垂直方向交错开。其中第一抑制单元301a中的铟柱的直径大于第二抑制单元301b中的铟柱的直径。第三抑制单元301c中的铟柱的直径小于第一抑制单元301a中的铟柱的直径。

53.上述示例中,第一线路101为读取总线,第二线路102为读取谐振腔。在另一些示例中,第一线路101可以选择为应用于超导量子芯片的微波控制线;对应地,第二线路102中的基准线路201和对照线路202分别为应用于超导量子芯片的通量控制线。或者,第一线路和第二线路也可以是量子芯片中的各种其他形式的元件。

54.其次,如前述抑制元件的各种性质特性(数量、形状、尺寸和位置中的一者或多个组合)均可能对串扰抑制效果起到不同程度的影响,而图1和图3所示的示例中主要对抑制元件的形状、尺寸以及位置进行了示例性的说明。应当理解在其他示例中,抑制元件还可以是其他形状、尺寸和位置;或者,在串扰测试组件中,各个抑制单元中抑制元件也可以包括空气桥和铟柱。

55.对应于上述的串扰抑制组件,示例中可以提供串扰测试方法。

56.示例性地,参阅图4,串扰测试方法包括以下步骤:步骤s101、提供串扰测试组件。

57.步骤s102、测定第一线路101和基准线路201之间的第一耦合强度,以及测定第一线路101和对照线路202之间的第二耦合强度。

58.步骤s103、比较第一耦合强度和第二耦合强度,以确定抑制元件弱化串扰的程度。

59.当第一线路101按照读取总线的结构形式进行构造,而基准线路201和对照线路202按照读取谐振腔构造时,串扰测试方法可以包括:测定并比较各个读取谐振腔的品质因子,以确定抑制元件弱化串扰的性能。其中的测试方法如前述利用网络分析仪对s参数进行测试。

60.例如,当由读取谐振腔构造的基准线路201被测量到的q值十二万,而当读取谐振腔构造的对照线路202被测量到的q值十四万时,则可以认为增设的抑制元件减弱了读取总线与读取谐振腔之间的耦合作用,也就起到了降低串扰的作为。换言之,传输信号的两条线路或两元件之间的串扰可以由二者之间的耦合作用的形式被呈现。因此,耦合强,则表明串扰增加。因此通过确定q值就可以评价串扰—q值大,则串扰小。

61.前文通过参考附图描述的实施例是示例性的,仅用于解释本技术,而不能解释为对本技术的限制。为使本技术实施例的目的、技术方案和优点更加清楚,前述内容结合附图对本技术的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本技术各实施例中,为了使读者更好地理解本技术而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本技术所要求保护的技术方案。其中的各个实例的划分是为了描述方便,不应对本技术的具体实现方式构成任何限定,各个实施例在不矛盾的前提下可以相互结合相互引用。

62.需要说明的是,本技术的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本技术的实施例能够以除了在这里图示或描述的那些以外的顺序实施。

63.此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

64.以上依据图式所示的实施例详细说明了本技术的构造、特征及作用效果,以上仅为本技术的较佳实施例,但本技术不以图面所示限定实施范围,凡是依照本技术的构想所作的改变,或修改为等同变化的等效实施例,仍未超出说明书与图示所涵盖的精神时,均应在本技术的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1