跨电路板边界扫描链生成方法与流程

1.本发明涉及集成电路领域,特别是涉及一种跨电路板边界扫描链生成方法。

背景技术:

2.边界扫描(boundary scan)测试发展于上个世纪90年代,随着大规模集成电路的出现,印制电路板制造工艺向小,微,薄发展,传统的ict测试已经没有办法满足这类产品的测试要求。由于芯片的引脚多,元器件体积小,板的密度特别大,根本没有办法进行下探针测试。一种新的测试技术产生了,联合测试行为组织(joint test action group)简称jtag定义这种新的测试方法即边界扫描测试。

3.边界扫描是应用于集成电路级的设计规则的集合,允许软件减轻设计、生产和测试数字系统的不断增长的成本。以前只能通过特殊测试方法来解决的极其困难的印刷电路板测试问题现在能够被边界扫描轻松快速地处理。

4.边界扫描测试主要针对数字逻辑结构,并且主要集中在集成电路芯片之外。边界扫描既可以在支持边界扫描的芯片之间进行互连测试及诊断,也可以在支持边界扫描的芯片内进行不同程度的内部测试。

5.当前集成电路技术日新月异,集成电路规模越来越庞大,密度也越来越高,所以待测主板上的接口也越来越多,这些接口都需要设计配套的转板来配合测试。由于每个测试转板上面都有至少一颗可支持边界扫描的芯片,所以它们都会被识别为一条或多条单独的扫描链。但是硬件资源上可配置的tap端口是有限的,所以需要一种跨电路板的扫描链生成方法将部分测试转板串联起来以复用一些tap端口来减轻硬件资源负担。

技术实现要素:

6.在发明内容部分中引入了一系列简化形式的概念,该简化形式的概念均为本领域现有技术简化,这将在具体实施方式部分中进一步详细说明。本发明的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

7.本发明要解决的技术问题是提供一种能在有限硬件资源下且不降低测试覆盖率的情况下,能减少端口资源占用的跨电路板边界扫描链生成方法。

8.为解决上述技术问题,本发明提供的跨电路板边界扫描链生成方法,包括以下步骤:

9.s1,获取已经创建管脚库的待测芯片,添加到可测芯片列表;

10.s2,所述可测芯片列表,在遍历过程中沿着当前可测芯片的tdi查找上游的其他可测芯片,以及沿着当前可测芯片的tdo查找下游的其他可测芯片,按照从上游到下游的顺序给查找到的可测芯片编序;

11.s3,根据测试需求,将可测芯片列表中待测试同类型接口按所述可测芯片编序串联形成执行扫描链;

12.可执行扫描链的tdi取被串联前第1条扫描链的tdi,可执行扫描链的tdo取被串联前第n条扫描链的tdo,n>1。

13.可选择的,在两个可测芯片的同类型接口之间通过虚拟连接器连接。

14.可选择的,在两个可测芯片之间还设有虚拟跳线。

15.可选择的,进一步改进所述的跨电路板边界扫描链生成方法,还包括

16.s4,根据测试需求确定要合并测试的扫描链及其顺序,得到要合并的扫描链数目,设为m;

17.然后按照可测芯片顺序给扫描链编序,第1条扫描链的序号为1,第2条扫描链的序号为2,最后一条扫描链的序号为m;

18.s5,新建m-1个虚拟节点,更改第n条扫描链的tdo配置和第n+1条扫描链的tdi配置,m-1≥n≥1;

19.将第n条扫描链的tdo节点上的tdo管脚放置到第n个虚拟节点上,将第n+1条扫描链的tdi节点上的tdi管脚放置到第n个虚拟节点上;

20.s6,随机选择一个被合并前的扫描链上的待测芯片作为中心器件,沿着该中心器件的tdi节点和tdo节点向两侧开始搜索,最后形成一条完整的包含所有被合并前的待测芯片的扫描链。

21.本发明通过虚拟连接器将部分待测电路板上的待测芯片的tdo/tdi和需要被合并的电路板上的待测芯片的tdi/tdo串联在一起,这种串联使边界扫描软件可以在识别扫描链的时候沿着该链任意待测芯片的tdi/tdo往两侧扩展从而找到包含该链所有待测芯片的完整扫描链,进而实现在有限硬件资源下且不降低测试覆盖率的情况下,能减少端口资源占用,能提高测试的效率。

附图说明

22.本发明附图旨在示出根据本发明的特定示例性实施例中所使用的方法、结构和/或材料的一般特性,对说明书中的描述进行补充。然而,本发明附图是未按比例绘制的示意图,因而可能未能够准确反映任何所给出的实施例的精确结构或性能特点,本发明附图不应当被解释为限定或限制由根据本发明的示例性实施例所涵盖的数值或属性的范围。下面结合附图与具体实施方式对本发明作进一步详细的说明:

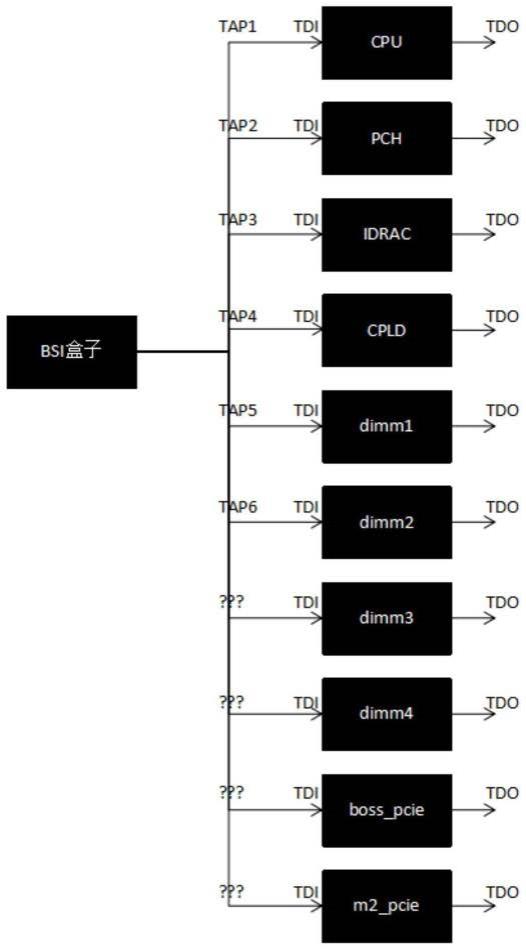

23.图1是现有技术扫描链结构示意图。

24.图2是本发明扫描链结构示意图一。

25.图3是本发明扫描链结构示意图二。

具体实施方式

26.以下通过特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所公开的内容充分地了解本发明的其他优点与技术效果。本发明还可以通过不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点加以应用,在没有背离发明总的设计思路下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。本发明下述示例性实施例可以多种不同的形式来实施,并且不应当被解释为只限于这里所阐述的具体实施例。应当理解的是,提供这些实施例

是为了使得本发明的公开彻底且完整,并且将这些示例性具体实施例的技术方案充分传达给本领域技术人员。应当理解的是,当元件被称作“连接”或“结合”到另一元件时,该元件可以直接连接或结合到另一元件,或者可以存在中间元件。不同的是,当元件被称作“直接连接”或“直接结合”到另一元件时,不存在中间元件。在全部附图中,相同的附图标记始终表示相同的元件。

27.第一实施例;

28.本发明提供的跨电路板边界扫描链生成方法,包括以下步骤:

29.s1,获取已经创建管脚库的待测芯片,添加到可测芯片列表;

30.s2,所述可测芯片列表,在遍历过程中沿着当前可测芯片的tdi查找上游的其他可测芯片,以及沿着当前可测芯片的tdo查找下游的其他可测芯片,按照从上游到下游的顺序给查找到的可测芯片编序;

31.s3,根据测试需求,将可测芯片列表中待测试同类型接口按所述可测芯片编序串联形成执行扫描链;

32.可执行扫描链的tdi取被串联前第1条扫描链的tdi,可执行扫描链的tdo取被串联前第n条扫描链的tdo,n>1;

33.其中,在两个可测芯片的同类型接口之间通过虚拟连接器连接,在两个可测芯片之间还设有虚拟跳线。

34.兹举例以下芯片测试结合上述实施例进一步说明本发明原理;

35.假设bsi测试装置有6个tap端口可供同时测试。

36.假设待测主板上已有cpu链、pch链、cpld链和idrac链,现在有额外的4个内存条接口(分别对应dimm1、dimm2、dimm3、dimm4)和两个pcie接口(boss_pcie和m2_pcie)需要测试,那么按照附图1所示的实现dimm3、dimm4、boss_pcie和m2_pcie接口将无法分配到测试端口,从而降低了测试覆盖率。

37.采用本发明提供的方案:

38.在dimm1待测芯片的tdo上插入虚拟连接器dimm1.cn1

39.在dimm2待测芯片的tdi上插入虚拟连接器dimm2.cn1,在tdo上插入虚拟连接器dimm2.cn2

40.在dimm3待测芯片的tdi上插入虚拟连接器dimm3.cn1,在tdo上插入虚拟连接器dimm3.cn2

41.在dimm4待测芯片的tdi上插入虚拟连接器dimm4.cn1

42.将dimm1.cn1和dimm2.cn1进行merge,生成虚拟跳线virtualjumper1

43.将dimm2.cn2和dimm3.cn1进行merge,生成虚拟跳线virtualjumper2

44.将dimm3.cn2和dimm4.cn1进行merge,生成虚拟跳线virtualjumper3

45.这样边界扫描软件在识别扫描链的时候就可以沿着该链任意待测芯片的tdi节点和tdo节点向两侧扩展,从而生成一条包含dimm1、dimm2、dimm3和dimm4的扫描链,在有限硬件资源下且不降低测试覆盖率的情况下,能减少端口资源占用。

46.第二实施例;

47.本发明提供的跨电路板边界扫描链生成方法,包括以下步骤:

48.s1,获取已经创建管脚库的待测芯片,添加到可测芯片列表;

49.s2,所述可测芯片列表,在遍历过程中沿着当前可测芯片的tdi查找上游的其他可测芯片,以及沿着当前可测芯片的tdo查找下游的其他可测芯片,按照从上游到下游的顺序给查找到的可测芯片编序;

50.s3,根据测试需求,将可测芯片列表中待测试同类型接口按所述可测芯片编序串联形成执行扫描链;

51.可执行扫描链的tdi取被串联前第1条扫描链的tdi,可执行扫描链的tdo取被串联前第n条扫描链的tdo,n>1;

52.s4,根据测试需求确定要合并测试的扫描链及其顺序,得到要合并的扫描链数目,设为m;

53.然后按照可测芯片顺序给扫描链编序,第1条扫描链的序号为1,第2条扫描链的序号为2,最后一条扫描链的序号为m;

54.s5,新建m-1个虚拟节点,更改第n条扫描链的tdo配置和第n+1条扫描链的tdi配置,m-1≥n≥1;

55.将第n条扫描链的tdo节点上的tdo管脚放置到第n个虚拟节点上,将第n+1条扫描链的tdi节点上的tdi管脚放置到第n个虚拟节点上;

56.s6,随机选择一个被合并前的扫描链上的待测芯片作为中心器件,沿着该中心器件的tdi节点和tdo节点向两侧开始搜索,最后形成一条完整的包含所有被合并前的待测芯片的扫描链。

57.第二实施例相较上述第一实施例有点在于不需要增加额外的电路板元件,而是通过直接修改电路板网络拓扑的方式将同类型接口对应的待测芯片串联到了一起,第二实施例操作更为简单,但是修改了原有电路板的网络拓扑,不具有可逆性。

58.除非另有定义,否则这里所使用的全部术语(包括技术术语和科学术语)都具有与本发明所属领域的普通技术人员通常理解的意思相同的意思。还将理解的是,除非这里明确定义,否则诸如在通用字典中定义的术语这类术语应当被解释为具有与它们在相关领域语境中的意思相一致的意思,而不以理想的或过于正式的含义加以解释。

59.以上通过具体实施方式和实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1