一种基于ZYNQ_FPGA的车载毫米波雷达处理系统的制作方法

本技术涉及毫米波雷达,具体而言,涉及一种基于zynq_fpga的车载毫米波雷达处理系统。

背景技术:

1、目前,毫米波雷达多采用单个射频芯片解决方案,虽说采用单射频芯片可以基本满足现有绝大多数主机厂的需求,但是由于有限的通道数造成雷达信号精度较低,无法满足不断发展市场需求,因而多片射频芯片级联方案得到国内外各大雷达厂商的重视。然而,多片级联带来的不仅仅是雷达信号精度的提高,同时也提高了雷达系统数据处理复杂程度。

2、当前行业中主要有两种解决方案:(1)在多片级联的方案中采用多片低性能fpga+一片dsp架构进行设计。该方案的缺点在于:对数据同步设计要求较高,设计较难,而且综合成本不低于直接选择一款高性能的fpga。(2)选择一片高性能的fpga替换dsp以提高性能,如zynq。该方案的缺点在于:直接选用一款带arm核的高性能fpga(zynq),由于技术还未成熟,其数据主要还是在arm核内进行处理,并未根据fpga内部资源对不同算法进行实际的优化,使得整体处理时延不低于使用dsp的方案,浪费了高性能fpga高速处理数据能力。

技术实现思路

1、本实用新型的目的在于提供一种基于zynq_fpga的车载毫米波雷达处理系统,极大的降低了数据处理的延时,适应车载雷达发展的未来需求。

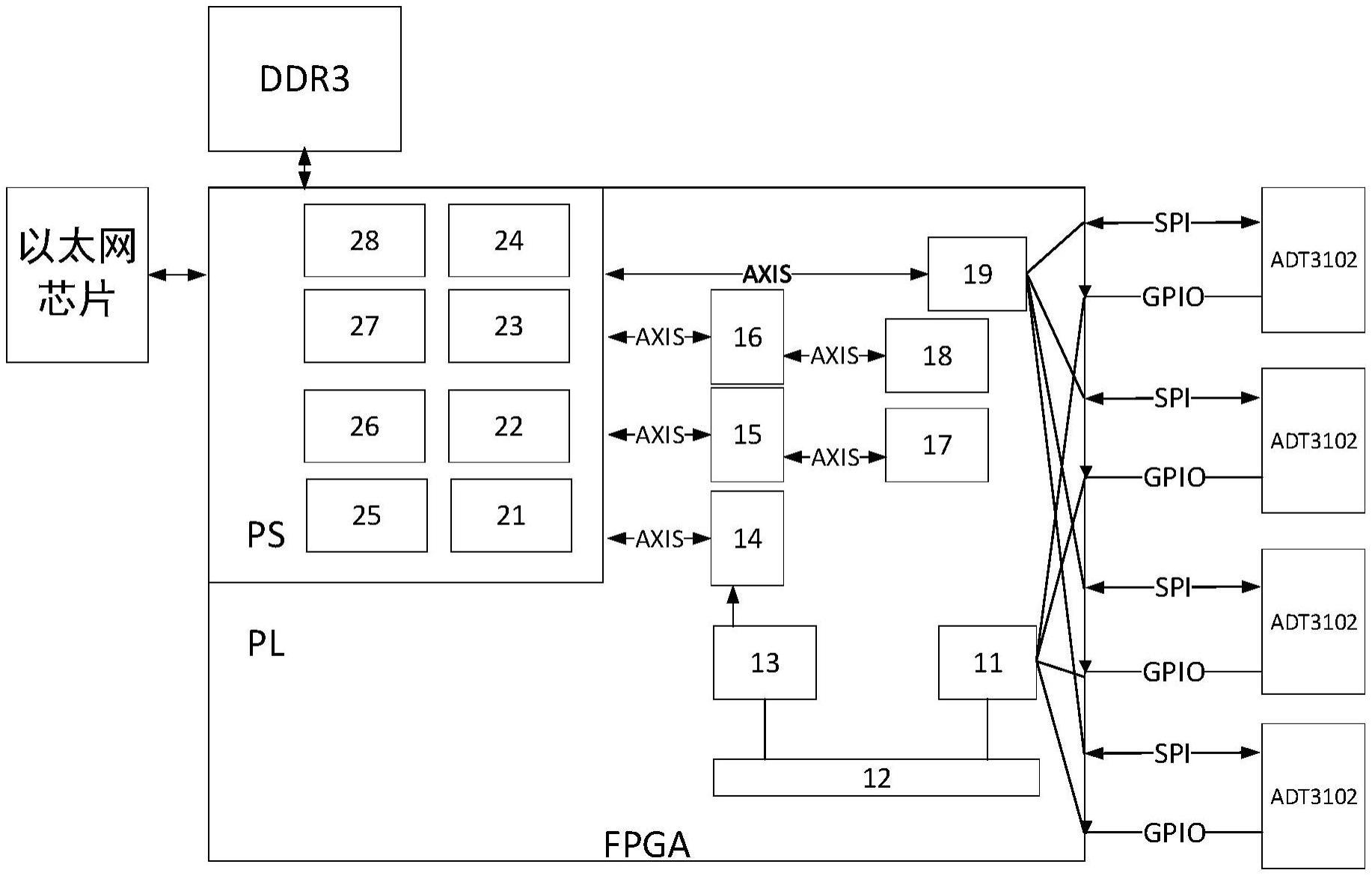

2、为解决上述技术问题,本实用新型采用的技术方案是:一种基于zynq_fpga的车载毫米波雷达处理系统,包括fpga系统、以太网芯片、存储芯片和多个射频芯片,所述fpga系统包括相互连接的ps器件和pl器件,所述ps器件用于向pl器件中各模块下发指令,以及对采集数据进行计算处理,所述pl器件用于配置射频芯片的波形数据,以及采集射频芯片数据,进行解码、转换后发送至ps器件,所述ps器件与以太网芯片和存储芯片相连,所述以太网芯片用于与上位机进行数据传输,所述存储芯片用于存储软件程序、采集数据和计算后的数据,所述pl器件与多个射频芯片相连,所述射频芯片用于接收和发射波形数据。

3、作为优选方案,所述ps器件包括测距模块、测速模块、测角模块、cfar模块、以太网传输模块、指令控制模块和ddr存储模块;所述测距模块用于根据采集数据进行距离计算;所述测速模块用于根据采集数据进行速度计算;所述测角模块用于根据采集数据进行角度计算;所述cfar模块用于对经pl器件处理后的数据进行筛选,保留有效数据作为数据源;所述以太网传输模块与以太网芯片相连,用于将数据传输至以太网芯片进行通信;所述指令控制模块用于向pl器件中各模块下发指令;所述ddr存储模块与存储芯片相连,用于将软件程序、采集数据和计算后的数据存储至所述存储芯片。

4、作为优选方案,所述pl器件包括数据采集模块、数据解码模块、fifo缓存模块、第一dma传输模块、第二dma传输模块、第三dma传输模块、1d_fft处理模块、2d_fft处理模块和雷达配置spi模块;所述数据采集模块与多个射频芯片相连,用于采集多个射频芯片的数据,并将串行数据转换为并行数据;所述数据解码模块用于对采集后的并行数据进行解析,获得对应通道的实部虚部;所述fifo缓存模块用于接收对应通道的实部虚部,进行缓存;所述第一dma传输模块用于进行fifo缓存模块和ps器件之间的数据传输;所述第二dma传输模块用于进行1d_fft处理模块和ps器件之间的数据传输;所述第三dma传输模块用于进行2d_fft处理模块和ps器件之间的数据传输;所述1d_fft处理模块用于对数据进行fft计算;所述2d_fft处理模块用于对数据进行2维fft处理;所述雷达配置spi模块用于对射频芯片进行波形数据配置。

5、作为优选方案,所述雷达配置spi模块通过spi接口与多个射频芯片相连,所述数据采集模块通过gpio接口与多个射频芯片相连。

6、作为优选方案,所述ps器件和pl器件通过axis协议进行内部通信。

7、作为优选方案,所述射频芯片的型号为adt3102,所述以太网芯片的型号为ksz9031rnx,所述存储芯片的型号为mt41k256m16tw-107。

8、与现有技术相比,本实用新型的有益效果包括:本申请通过对fpga系统架构进行重新编排组合,采用多个dma传输模块,达到数据边采集边计算的目的,能够实时计算fft数据,而且采用pl器件的fft_ip核,降低了fft算法延时。本发明在同等规模的数据量前提下,极大的降低了数据处理的延时,适应车载雷达发展的未来需求。

技术特征:

1.一种基于zynq_fpga的车载毫米波雷达处理系统,其特征在于,包括fpga系统、以太网芯片、存储芯片和多个射频芯片,所述fpga系统包括相互连接的ps器件和pl器件,所述ps器件用于向pl器件中各模块下发指令,以及对采集数据进行计算处理,所述pl器件用于配置射频芯片的波形数据,以及采集射频芯片数据,进行解码、转换后发送至ps器件,所述ps器件与以太网芯片和存储芯片相连,所述以太网芯片用于与上位机进行数据传输,所述存储芯片用于存储软件程序、采集数据和计算后的数据,所述pl器件与多个射频芯片相连,所述射频芯片用于接收和发射波形数据。

2.根据权利要求1所述的基于zynq_fpga的车载毫米波雷达处理系统,其特征在于,所述ps器件包括测距模块、测速模块、测角模块、cfar模块、以太网传输模块、指令控制模块和ddr存储模块;

3.根据权利要求1所述的基于zynq_fpga的车载毫米波雷达处理系统,其特征在于,所述pl器件包括数据采集模块、数据解码模块、fifo缓存模块、第一dma传输模块、第二dma传输模块、第三dma传输模块、1d_fft处理模块、2d_fft处理模块和雷达配置spi模块;

4.根据权利要求3所述的基于zynq_fpga的车载毫米波雷达处理系统,其特征在于,所述雷达配置spi模块通过spi接口与多个射频芯片相连,所述数据采集模块通过gpio接口与多个射频芯片相连。

5.根据权利要求1所述的基于zynq_fpga的车载毫米波雷达处理系统,其特征在于,所述ps器件和pl器件通过axis协议进行内部通信。

6.根据权利要求1所述的基于zynq_fpga的车载毫米波雷达处理系统,其特征在于,所述射频芯片的型号为adt3102,所述以太网芯片的型号为ksz9031rnx,所述存储芯片的型号为mt41k256m16tw-107。

技术总结

本技术提出了一种基于ZYNQ_FPGA的车载毫米波雷达处理系统,包括FPGA系统、以太网芯片、存储芯片和多个射频芯片,FPGA系统包括相互连接的PS器件和PL器件,PS器件用于向PL器件中各模块下发指令,以及对采集数据进行计算处理,PL器件用于配置射频芯片的波形数据,以及采集射频芯片数据,进行解码、转换后发送至PS器件,PS器件与以太网芯片和存储芯片相连,所述以太网芯片用于与上位机进行数据传输,存储芯片用于存储软件程序、采集数据和计算后的数据,PL器件与多个射频芯片相连,射频芯片用于接收和发射波形数据。本技术极大的降低了数据处理的延时,适应车载雷达发展的未来需求。

技术研发人员:张立飞,顾超,王开宇,杨克建

受保护的技术使用者:南京楚航科技有限公司

技术研发日:20221222

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!