电源检测电路的制作方法

本技术涉及电源上电检测,例如涉及一种电源检测电路。

背景技术:

1、电源检测电路,是用于检测电源电压的情况,实现电源变换、电压门限检测的电路。如公开号为cn108649939a的中国专利文件,其说明书[0005]段公开了一种主流por电路2,由带隙基准电路21及电压比较器22组成,所述带隙基准电路21连接于电源vdd和地gnd之间,输出带隙基准电压vref;所述电压比较器22的正相输入端接收所述带隙基准电压vref,反相输入端接收电阻r1’和r2’的分压vdiv,进行比较后输出比较结果。公开号为cn105891734a的中国专利文件,其说明书[0004]段公开了一种电源检测电路,由电容、分压电阻、基准电压产生电路、比较器组成,分压电阻对电源电压vdd进行分压,然后通过比较器com与基准电压vref比较,如果vdd减小到一定阈值,比较器输出vout为低电平;如果vdd在正常范围,比较器输出vout为高电平。再如图1所示,图1为现有技术中的一种电源检测电路,包括电源域vcc、第四电阻r4、第五电阻r5、第三nmos管nm3、第四nmos管nm4、第四pmos管pm4和缓冲器电路buf。第四电阻的一端与电源域vcc电连接,第四电阻的另一端分别与第五电阻的一端、第四nmos管的栅极以及第四pmos管的栅极电连接。第五电阻的另一端与第三nmos管的栅极以及漏极电连接;第三nmos管的栅极以及漏极电连接;所述第三nmos管的源极接地。第五电阻的一端分别与第四nmos管的栅极以及第四pmos管的栅极电连接。第四nmos管的栅极与第四pmos管的栅极电连接,第四nmos管的源极接地,第四nmos管的漏极分别与第四pmos管的漏极以及缓冲器电路的输入端电连接,第四pmos管的漏极与缓冲器电路的输入端电连接,第四pmos管的源极与电源域vcc电连接,所述缓冲器电路用于输出电源状态指示信号。在电源域的电源电压低于设定阈值的情况下,缓冲器电路输出的电源状态指示信号为0,随着电源域的上电,电源域的电源电压持续升高,在源电压大于或等于设定阈值的情况下,第四nmos管和第四pmos形成的反相器发生反转,从而使得缓冲器电路输出的电源状态指示信号为1。从而完成对电源域的上电检测。

2、在实现本公开实施例的过程中,发现相关技术中至少存在如下问题:

3、现有的电源检测电路在电源域上电完成之后,各元器件仍然处于功耗状态,导致功耗较大。

4、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本技术的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、为了对披露的实施例的一些方面有基本的理解,下面给出了简单的概括。所述概括不是泛泛评述,也不是要确定关键/重要组成元素或描绘这些实施例的保护范围,而是作为后面的详细说明的序言。

2、本公开实施例提供了一种电源检测电路,以能够在电源域上电完成时候,减小电源检测电路的功耗。

3、在一些实施例中,所述电源检测电路,包括:电源域,分别与采样电路和比较器电路电连接;所述采样电路,与所述比较器电路电连接,所述采样电路用于对电源域进行采样,获得并输出电源电压给所述比较器电路;所述比较器电路,分别与整形电路的输入端和反相器的输出端电连接;所述比较器电路用于根据所述电源电压生成并发送第一电平信号给所述整形电路;其中,在所述电源电压大于或等于设定阈值的情况下,所述比较器电路生成的第一电平信号为0;所述整形电路,与所述反相器的输入端电连接;所述整形电路用于对所述第一电平信号进行滤波和整形处理,生成电源状态指示信号;所述反相器,在所述第一电平信号为0的情况下,根据所述电源状态指示信号生成并发送第二电平信号给所述比较器电路,以断开所述比较器电路和所述整形电路之间的连接。

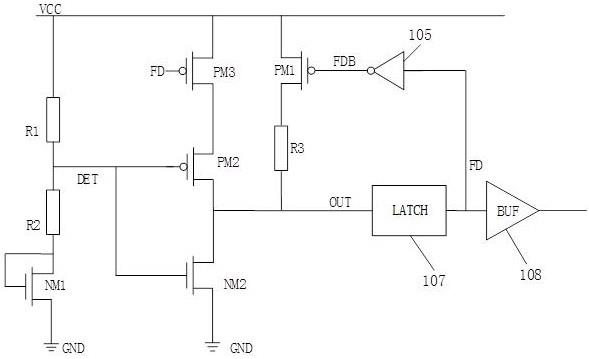

4、在一些实施例中,所述采样电路包括第一电阻、第二电阻和第一nmos管;所述第一电阻的一端与所述电源域电连接;所述第一电阻的另一端分别与所述第二电阻的一端和所述比较器电路电连接,所述第二电阻的一端与所述比较器电路电连接;所述第二电阻的另一端与所述第一nmos管的漏极电连接,所述第一nmos管的栅极与所述第一nmos管的漏极电连接,所述第一nmos管的源极接地。

5、在一些实施例中,所述比较器电路包括第二nmos管、第三电阻和第一pmos管,所述第二nmos管的漏极分别与所述第二nmos管的栅极、第三电阻的一端以及所述整形电路的输入端电连接;所述第三电阻的另一端与所述第一pmos管的漏极电连接;所述第二nmos管的源极接地;所述第一pmos管的栅极与所述反相器的输出端电连接;所述第一pmos管的源极与所述电源域电连接。

6、在一些实施例中,所述电源检测电路,还包括:反相电路,分别与所述采样电路、所述整形电路和所述电源域电连接;在所述第一电平信号为0的情况下,所述反相电路根据所述电源状态指示信号与所述整形电路导通。

7、在一些实施例中,所述反相电路包括第二pmos管和第三pmos管;所述第二pmos管的栅极分别与所述采样电路和所述第二nmos管的栅极电连接;所述第二pmos管的源极与所述第三pmos管的漏极电连接,所述第二pmos管的漏极分别与所述第二nmos管的漏极、所述第三电阻的一端以及所述整形电路电连接;所述第三pmos管的栅极用于接收所述电源状态指示信号;所述第三pmos管的源极与所述电源域电连接。

8、在一些实施例中,所述整形电路包括锁存器电路和缓冲器电路;所述锁存器电路的输入端与所述比较器电路电连接,所述锁存器电路的输出端分别与所述反相器的输入端和所述缓冲器电路的输入端电连接;所述锁存器电路用于锁定所述电源状态指示信号为第一电平信号。

9、在一些实施例中,在所述第一电平信号为0的情况下,所述整形电路生成的电源状态指示信号为0,用于表征电源域上电完成。

10、在一些实施例中,在所述电源状态指示信号为0的情况下,所述反相器生成的第二电平信号为1。

11、在一些实施例中,在所述电源电压小于设定阈值的情况下,所述比较器电路生成的第一电平信号为1。

12、在一些实施例中,在所述第一电平信号为1的情况下,所述整形电路生成的电源状态指示信号为1,用于表征电源域未完成上电。

13、本公开实施例提供的电源检测电路,可以实现以下技术效果:通过采样电路对电源域的电源电压进行上电检测,并通过比较器电路根据电源电压生成并发送第一电平信号给整形电路。然后经由整形电路对第一电平信号进行滤波和整形处理,生成电源状态指示信号,使得反相器能够根据电源状态指示信号生成第二电平信号。由于在电源电压大于或等于设定阈值的情况下,比较器电路生成的第一电平信号为0。同时在第一电平信号为0的情况下,反相器根据电源状态指示信号生成的第二电平信号,能够断开比较器电路和整形电路之间的连接。且在电源电压大于或等于设定阈值的情况下,即表征电源域上电完成。故本公开实施例提供的电源检测电路,能够在电源域上电完成的情况下,断开比较器电路和整形电路之间的连接。使得比较器电路在电源域上电完成之后被关闭,从而能够在电源域上电完成时候,减小电源检测电路的功耗。

14、以上的总体描述和下文中的描述仅是示例性和解释性的,不用于限制本技术。

15、附图说明

16、一个或多个实施例通过与之对应的附图进行示例性说明,这些示例性说明和附图并不构成对实施例的限定,附图中具有相同参考数字标号的元件示为类似的元件,附图不构成比例限制,并且其中:

17、图1是现有技术中的电源检测电路;

18、图2是本公开实施例提供的第一个电源检测电路的示意图;

19、图3是本公开实施例提供的一个采样电路的示意图;

20、图4是本公开实施例的一个比较器电路和反相电路的示意图;

21、图5是本公开实施例的第二个电源检测电路的示意图;

22、图6是本公开实施例的第三个电源检测电路的示意图。

- 还没有人留言评论。精彩留言会获得点赞!