一种基于FPGA的自适应频率测量装置及测试方法与流程

本发明应用于数字频率测量的,特别涉及一种基于fpga的自适应频率测量装置及测试方法。

背景技术:

1、数字频率测量方法有三种:直接测量法、间接测量法以及等精度测量法。

2、直接测量法是通过基准时钟计数产生闸门信号,在闸门信号时间内对被测信号周期进行计数,按照基准时钟频率、基准时钟数和被测信号周期数的比例关系,求出被测信号频率。然而直接测量法在通过基准时钟定时,计数被测信号直接测量被测信号频率,所带来的测量误差来源于±1个被测信号周期。被测信号周期越大,频率越低,误差越大,因此仅适用于高频测量场景。

3、间接测量法是在被测信号一个周期内,对基准时钟进行计数,计算出被测信号周期,求出被测信号频率。间接测量法在通过计数被测信号一个周期内的基准时钟个数,确定被测信号周期,从而换算被测信号频率,所带来的测量误差来源于±1个基准时钟周期。但为了保证此方法的测量精度,要求被测信号周期相对于基准时钟足够大,因此仅适用于低频测量场景。

4、等精度测量法是通过被测信号周期计数产生闸门信号,在闸门信号时间内对基准时钟进行计数,按照基准时钟频率、基准时钟数和被测信号周期数的比例关系,求出被测信号频率。然而等精度测量法在通过被测信号定时,计数基准时钟,按照比例关系计算出被测信号频率,各频段的测量误差均来源于±1个基准时钟周期,保证全频段测量等精度。但需要对被测信号周期数设置合理的计数值,否则依然会导致测量结果不准确或是测量时间过长等问题。

5、在数字频率测量技术中,影响数字频率测量的因素主要有三个,分别是测量范围、测量精度以及测量时间。上述三种方法存在测量范围的限制或测量精度不高的缺陷,因此有必要提供一种适应性更强、能够兼容多种测量范围、能够提高测量精度、能够控制测量时间的基于fpga的自适应频率测量装置及测试方法。

技术实现思路

1、本发明所要解决的技术问题是克服现有技术的不足,提供了一种适应性更强、能够兼容多种测量范围、能够提高测量精度、能够控制测量时间的基于fpga的自适应频率测量装置及测试方法。

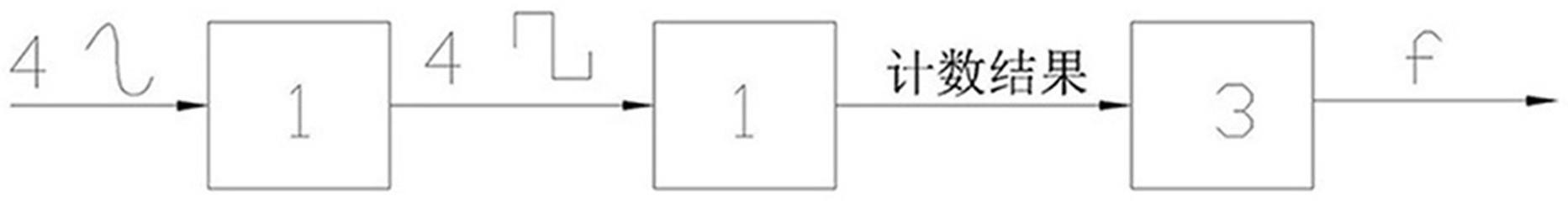

2、本发明所采用的技术方案是:本发明包括依次电连接的高速电压比较器、fpga测频模块以及运算单元,所述高速电压比较器接入被测信号,所述高速电压比较器将所述被测信号转换为数字脉冲,所述fpga测频模块进行测量计数,获得所述被测信号的计数结果和基准时钟计数结果,所述运算单元计算出所述被测信号的频率。

3、由上述方案可见,所述基于fpga的自适应频率测量装置应用于对宽频段信号的频率测量,兼顾测量范围、测量精度与测量时间。利用fpga实现精准计数,通过分析被测信号频率大致范围,设置合适的测量方法和测量时间,从而解决传统测频技术中的问题,适应性更强,兼容低频测量场景和高频测量场景,提高了测量精度,能够有效控制测量时间,同时自适应选择测量方法和自适应设置测量时间。

4、一个优选方案是,所述fpga测频模块包括依次电连接的频率预测模块、频率计数模块以及频率输出模块,所述频率预测模块包括依次电连接的边沿检测器、预测计数器、计数比较器、低频标志寄存器、时间设置寄存器,所述频率计数模块包括依次电连接的定时计数器、第一闸门生成器、第二闸门生成器、第三闸门生成器,所述第二闸门生成器连接有被测信号计数器,所述第三闸门生成器连接有基准时钟计数器,所述频率输出模块包括被测信号计数结果寄存器、数据选择器、基准时钟计数结果寄存器,所述被测信号计数器与所述被测信号计数结果寄存器连接,所述基准时钟计数器经所述数据选择器与所述基准时钟计数结果寄存器连接,所述边沿检测器和所述被测信号计数器均接入所述被测信号。

5、一种用于基于fpga的自适应频率测量装置的测试方法,所述测试方法包括如下步骤:

6、步骤a、所述高速电压比较器将所述被测信号转换为相同频率的数字脉冲,传输给所述边沿检测器;

7、步骤b、所述边沿检测器检测到一个完整的所述被测信号的周期,在这个信号周期内,所述预测计数器会被使能开始计数基准时钟,当一个完整的信号周期结束后,所述预测计数器的计数值将被送入所述计数比较器,所述计数比较器通过比较计数值的大小范围输出一个比较结果,用于粗略判断所述被测信号周期大小,即频率范围;

8、步骤c、所述低频标志寄存器根据频率范围的大小是否产生低频标志,进而控制所述时间设置寄存器、所述被测信号计数器以及所述基准时钟计数器是否失能;

9、步骤d、所述基准时钟计数结果寄存器输出被测信号计数结果s1,所述基准时钟计数结果寄存器输出基准时钟计数结果s2,基准时钟频率s3为已知数值;所述运算单元根据被测信号计数结果s1、基准时钟计数结果s2以及基准时钟频率s3计算出所述被测信号的频率f,所述被测信号的频率f = 基准时钟频率s3 * 被测信号计数结果s1 / 基准时钟计数结果s2。

10、所述步骤c包括以下细分步骤:

11、步骤c1、当f<s3时,即意味着信号频率足够低时,所述低频标志寄存器会产生低频标志,所述时间设置寄存器、所述被测信号计数器的计数值和所述基准时钟计数器的计数值都将被失能,并将所述被测信号计数结果寄存器置1、所述预测计数器的计数值传输至所述基准时钟计数结果寄存器;

12、步骤c2、当f>s3时,即意味着信号频率足够高时,所述被测信号计数结果寄存器的数值为所述被测信号计数器的计数值,所述基准时钟计数结果寄存器的数值为所述数据选择器的输出值,所述数据选择器的输出值由所述计数比较器的比较结果决定;

13、步骤c2.1、当比较结果显示所述被测信号频率低于基准时钟时,所述数据选择器的输出值为所述基准时钟计数器的计数值,所述被测信号计数结果寄存器的数值为所述第二闸门生成器的计数结果,所述基准时钟计数结果寄存器的数值为所述第三闸门生成器的计数结果;

14、步骤c2.2、当所述被测信号频率高于基准时钟时,所述数据选择器的输出为所述定时计数器的测量时间计数值,所述被测信号计数结果寄存器的数值为所述第二闸门生成器的计数结果,所述基准时钟计数结果寄存器的数值为所述第一闸门生成器的计数结果。

技术特征:

1.一种基于fpga的自适应频率测量装置,其特征在于:它包括依次电连接的高速电压比较器(1)、fpga测频模块(2)以及运算单元(3),所述高速电压比较器(1)接入被测信号(4),所述高速电压比较器(1)将所述被测信号(4)转换为数字脉冲,所述fpga测频模块(2)进行测量计数,获得所述被测信号(4)的计数结果和基准时钟计数结果,所述运算单元(3)计算出所述被测信号(4)的频率。

2.根据权利要求1所述的基于fpga的自适应频率测量装置,其特征在于:所述fpga测频模块(2)包括依次电连接的频率预测模块(21)、频率计数模块(22)以及频率输出模块(23),所述频率预测模块(21)包括依次电连接的边沿检测器(211)、预测计数器(212)、计数比较器(213)、低频标志寄存器(214)、时间设置寄存器(215),所述频率计数模块(22)包括依次电连接的定时计数器(221)、第一闸门生成器(222)、第二闸门生成器(223)、第三闸门生成器(224),所述第二闸门生成器(223)连接有被测信号计数器(225),所述第三闸门生成器(224)连接有基准时钟计数器(226),所述频率输出模块(23)包括被测信号计数结果寄存器(231)、数据选择器(232)、基准时钟计数结果寄存器(233),所述被测信号计数器(225)与所述被测信号计数结果寄存器(231)连接,所述基准时钟计数器(226)经所述数据选择器(232)与所述基准时钟计数结果寄存器(233)连接,所述边沿检测器(211)和所述被测信号计数器(225)均接入所述被测信号(4)。

3.一种用于如权利要求2所述的基于fpga的自适应频率测量装置的测试方法,其特征在于,所述测试方法包括如下步骤:

4.根据权利要求3所述的基于fpga的自适应频率测量装置的测试方法,其特征在于,所述步骤c包括以下细分步骤:

技术总结

本发明旨在提供一种适应性更强、能够兼容多种测量范围、能够提高测量精度、能够控制测量时间的基于FPGA的自适应频率测量装置及测试方法。本发明包括依次电连接的高速电压比较器、FPGA测频模块以及运算单元,所述高速电压比较器接入被测信号,所述高速电压比较器将所述被测信号转换为数字脉冲,所述FPGA测频模块进行测量计数,获得所述被测信号的计数结果和基准时钟计数结果,所述运算单元计算出所述被测信号的频率。本发明应用于数字频率测量的技术领域。

技术研发人员:陈运佳,张国富,宋小福

受保护的技术使用者:成都市运泰利自动化设备有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!