用于芯片上电自动校准的装置和方法与流程

本发明涉及芯片测试,更具体地,涉及一种用于芯片上电自动校准的装置和方法。

背景技术:

1、efuse技术广泛应用于对芯片在量产时候的内部参数微调,对于大规模量产芯片时,稳定而又快速、简洁的烧录方式能够大大提高新盘量产的良率。

2、现有的adc芯片在出厂时需要进行校准操作,对电压以及内部时钟进行校准操作;测试成本已经成为芯片成本的重要组成部分,减少测试时间具有经济效益;现有的上电trim电路存在上电trim以及烧录时间长,测试成本增加,可控性不足等问题。可靠的上电校准方案,对于芯片的稳定工作具有重要作用。

3、现有技术在模块层面提出了用于控制fuse的各种方式,但是在系统层面缺乏可靠的,有效的架构设计。

技术实现思路

1、本发明的目的是提出一种用于芯片上电自动校准的装置和方法,能够减少烧录时间和校准时间。

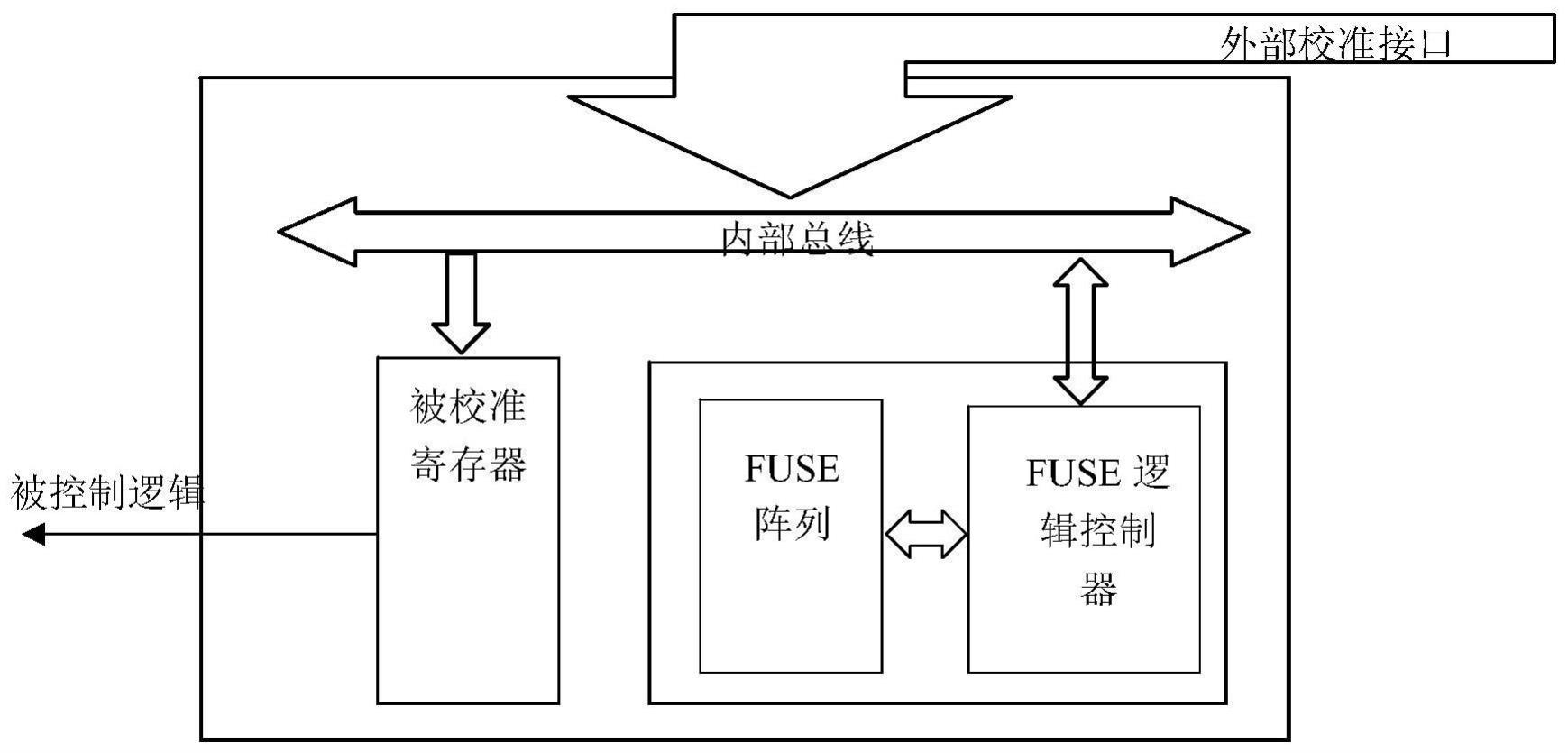

2、基于上述目的,本发明提供了一种用于芯片上电自动校准的装置,所述装置与所述芯片封装在一起,所述装置包括:

3、fuse逻辑控制器、fuse阵列、被校准寄存器和外部校准接口;

4、所述fuse逻辑控制器和所述fuse阵列电连接;

5、所述fuse逻辑控制器与所述外部校准接口均连接于所述芯片的内部总线;

6、所述外部校准接口用于将所述fuse阵列的所有存储单元的烧录值通过所述内部总线传输至所述fuse逻辑控制器中;

7、执行烧录时,所述fuse逻辑控制器基于所述烧录值对所述fuse阵列执行烧录操作;

8、上电trim时,所述fuse阵列中的值基于所述fuse逻辑控制器通过所述内部总线trim至所述被校准寄存器中。

9、可选方案中,所述fuse阵列的第0byte的8bit作为空片检测以及锁定标志位,当所述第0byte的高4bit位写入设定值时,标志所述fuse阵列被锁定,不能被烧录。

10、可选方案中,所述fuse阵列的第0byte的低4bit为全0时,标志所述fuse阵列为空片,上电不进行tirm操作;当第0byte的低4bit写入任意非0值,标志所述fuse阵列为非空片,上电时将所述fuse阵列中的值trim至所述被校准寄存器中。

11、可选方案中,所述fuse逻辑控制器具有第一寄存器,所述烧录值存储在所述第一寄存器中。

12、可选方案中,所述fuse逻辑控制器具有第二寄存器;根据所述被校准寄存器的数量和空间,确定fuse阵列的地址区间,并将所述地址的值存储在所述第二寄存器中,从而控制所述fuse逻辑控制器上电trim的区间范围。

13、可选方案中,所述芯片包括adc芯片。

14、本发明还提供了一种用于芯片上电自动校准的方法,包括:

15、fuse阵列的所有存储单元的初始状态为未烧断状态,初始值为0;

16、预先将fuse阵列的各存储单元的待烧录值通过所述芯片的内部总线存储在fuse逻辑控制器中,其中需要执行烧录的存储单元的所述烧录值为1,不需要执行烧录的存储单元的所述烧录值为0;

17、执行烧录时,基于所述烧录值对所述fuse阵列执行烧录操作,使相应存储单元的fuse值变为1,对于未执行烧录的存储单元,执行地址跳过操作;

18、上电trim时,将烧录后的所述fuse阵列的值基于所述fuse逻辑控制器通过所述内部总线trim至被校准寄存器中。

19、可选方案中,所述fuse阵列的第0byte的8bit作为空片检测以及锁定标志位,当所述第0byte的高4bit位写入设定值时,标志所述fuse阵列被锁定,不能被烧录。

20、可选方案中,当所述fuse阵列的第0byte的低4bit为全0时,标志所述fuse阵列为空片,上电不进行tirm操作;当第0byte的低4bit写入任意非0值,标志所述fuse阵列为非空片,上电时将所述fuse阵列中的值trim至所述被校准寄存器中。

21、可选方案中,所述fuse逻辑控制器具有第二寄存器;根据所述被校准寄存器的数量和空间,确定fuse阵列的地址区间,并将所述地址的值存储在所述第二寄存器中,从而控制所述fuse逻辑控制器上电trim的区间范围。

22、本发明的有益效果在于:

23、a)对于非trim的地址在烧录fuse时执行跳过操作,大幅减少烧录时间,降低测试成本。

24、b)增加空片检测特性,空片fuse阵列上电时不进行校准操作,保持电路的稳定性。

25、c)上电校准区间可控,有效利用fuse阵列空间,减少上电校准时间。

26、d)安全性设计,用户不能通过任何手段更改fuse阵列中的值。

27、e)精简设计,通过单个byte烧录以及读取的方式,尽可能减少fuse逻辑控制器内部寄存器的使用。

28、本发明具有其它的特性和优点,这些特性和优点从并入本文中的附图和随后的具体实施方式中将是显而易见的,或者将在并入本文中的附图和随后的具体实施方式中进行详细陈述,这些附图和具体实施方式共同用于解释本发明的特定原理。

技术特征:

1.一种用于芯片上电自动校准的装置,其特征在于,所述装置与所述芯片封装在一起,所述装置包括:

2.根据权利要求1所述的用于芯片上电自动校准的装置,其特征在于,所述fuse阵列的第0byte的8bit作为空片检测以及锁定标志位,当所述第0byte的高4bit位写入设定值时,标志所述fuse阵列被锁定,不能被烧录。

3.根据权利要求2所述的用于芯片上电自动校准的装置,其特征在于,所述fuse阵列的第0byte的低4bit为全0时,标志所述fuse阵列为空片,上电不进行tirm操作;当第0byte的低4bit写入任意非0值,标志所述fuse阵列为非空片,上电时将所述fuse阵列中的值trim至所述被校准寄存器中。

4.根据权利要求1所述的用于芯片上电自动校准的装置,其特征在于,所述fuse逻辑控制器具有第一寄存器,所述烧录值存储在所述第一寄存器中。

5.根据权利要求1所述的用于芯片上电自动校准的装置,其特征在于,所述fuse逻辑控制器具有第二寄存器;根据所述被校准寄存器的数量和空间,确定fuse阵列的地址区间,并将所述地址的值存储在所述第二寄存器中,从而控制所述fuse逻辑控制器上电trim的区间范围。

6.根据权利要求1所述的用于芯片上电自动校准的装置,其特征在于,所述芯片包括adc芯片。

7.一种用于芯片上电自动校准的方法,其特征在于,包括:

8.根据权利要求7所述的用于芯片上电自动校准的方法,其特征在于,所述fuse阵列的第0byte的8bit作为空片检测以及锁定标志位,当所述第0byte的高4bit位写入设定值时,标志所述fuse阵列被锁定,不能被烧录。

9.根据权利要求8所述的用于芯片上电自动校准的方法,其特征在于,当所述fuse阵列的第0byte的低4bit为全0时,标志所述fuse阵列为空片,上电不进行tirm操作;当第0byte的低4bit写入任意非0值,标志所述fuse阵列为非空片,上电时将所述fuse阵列中的值trim至所述被校准寄存器中。

10.根据权利要求8所述的用于芯片上电自动校准的方法,其特征在于,所述fuse逻辑控制器具有第二寄存器;根据所述被校准寄存器的数量和空间,确定fuse阵列的地址区间,并将所述地址的值存储在所述第二寄存器中,从而控制所述fuse逻辑控制器上电trim的区间范围。

技术总结

本发明公开一种用于芯片上电自动校准的装置和方法,所述装置与所述芯片封装在一起,所述装置包括:FUSE逻辑控制器、FUSE阵列、被校准寄存器和外部校准接口;所述FUSE逻辑控制器和所述FUSE阵列电连接;所述FUSE逻辑控制器与所述外部校准接口均连接于所述芯片的内部总线;所述外部校准接口用于将所述FUSE阵列的所有存储单元的烧录值通过所述内部总线传输至所述FUSE逻辑控制器中;执行烧录时,所述FUSE逻辑控制器基于所述烧录值对所述FUSE阵列执行烧录操作;上电trim时,所述FUSE阵列中的值基于所述FUSE逻辑控制器通过所述内部总线trim至所述被校准寄存器中。

技术研发人员:周常瑞,李栋,殷亚东,梁翔

受保护的技术使用者:苏州领慧立芯科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!