一种用于描述器件性能特征的版图结构、制作及测试方法与流程

本发明属于芯片,具体涉及一种提高芯片性能的方法,特别涉及一种用于描述器件性能特征的版图结构、制作及测试方法。

背景技术:

1、器件级布局广泛用于pcm测量或器件模型提取。为了获得更准确的器件性能,一种方法是在晶圆上放置尽可能多的结构。但这种方法是以晶圆面积为代价的,晶圆面积是有限的,特别是对于pcm结构。因此,如何以可实现的高质量和足够的硅数据进行建模来管理晶圆面积成本是一个巨大的挑战。本发明提供了一种解决这一问题的方法。

2、对于mosfet,有一些关键的器件参数,如idsat、idlin、gm、vth和漏电流。这些参数是监控过程和描述产品性能的最重要参数,它们主要用于调试产品故障。它们也是建模工程师构建设备模型的输入。这些参数通过器件级布局结构进行测量。由于放置此类结构的空间有限,尤其是对于pcm结构,因此放置尽可能多的结构非常重要。在结构较多的时候,共用焊盘(pad)就会较为常见。但是当一些焊盘通用共享时,它会引入一些寄生电阻,这将导致固有器件性能提取的不准确性。

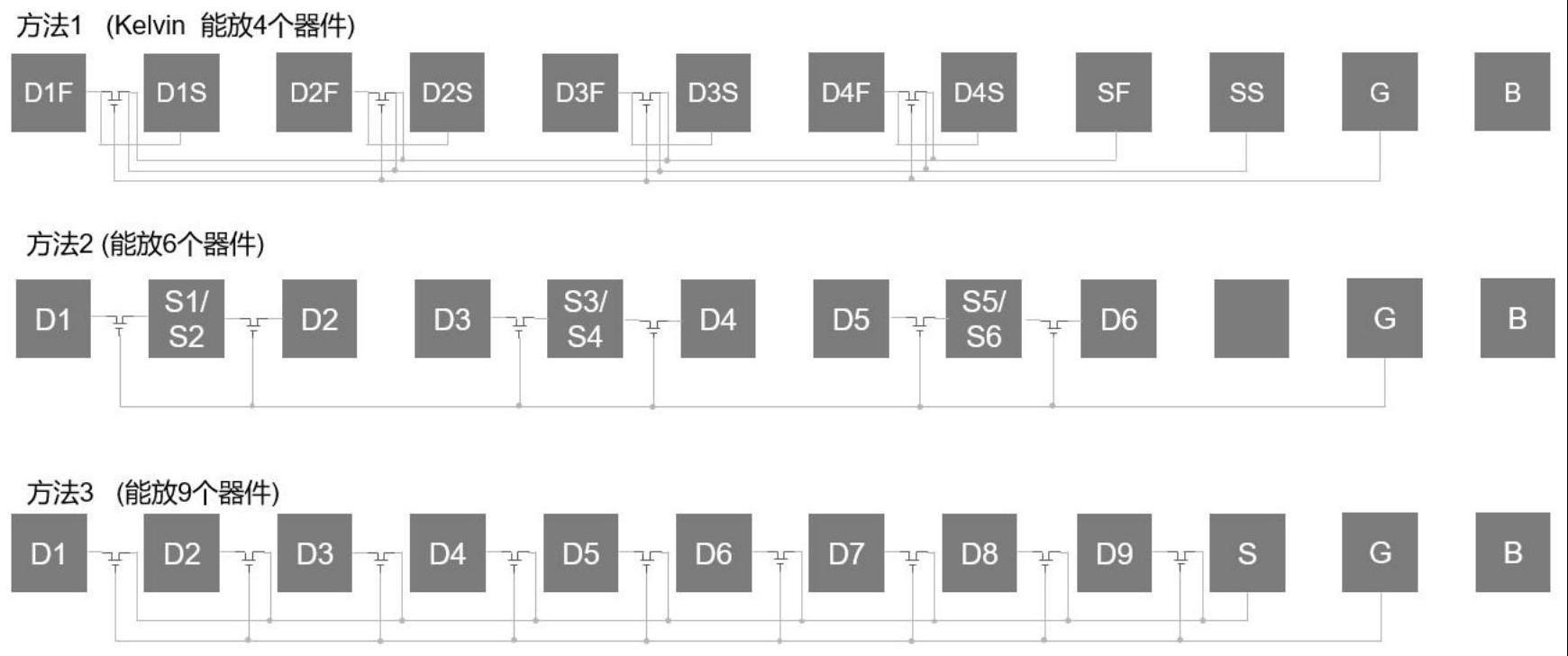

3、目前,有几种方法可以对pcm和模型提取结构进行布局,如图1所示。通常测试器件放在一个拥有12个pad的长方形区域内,以下以此结构为例。

4、方法1是开尔文结构,它可以消除金属布线的影响并获得准确的器件性能(idsat,idlin,gm,vth....)。但是这种方法的缺点是它需要很大的空间。在此布局示例中,12个焊盘只能放得下4个器件。该方法广泛用于模型提取。

5、方法2广泛用于pcm和模型提取结构。这种结构中从器件到源极和漏级pad的走线不会太多。使用公共栅极,由于栅极电流非常小,因此栅极布线的影响也微不足道。但与方法1类似,此方法占用太多空间。

6、方法3在pcm结构中应用广泛,由于它是公共源极和公共栅极,会造成布线影响(源极电阻增加)。但在这种方法中,12个pad里面可以放得下9个器件,这比方法1和方法2可以节省很多空间。但在许多情况下,这9个器件仍然不足以进行pcm监测。

7、通常,上述方法各自具有缺点,方法1测量结果精确但是占用面积,只适合器件建模使用,不能应用在pcm结构中。方法2也占用了过多的面积。方法三能够放下较多的器件,但是会带来较大的源极寄生电阻,影响测试精度。它们不能同时提供高测量精度并节省布局空间。在本发明中,我们提供了一种解决这些缺点的方法。

技术实现思路

1、本发明的目的是针对现有技术的不足,提供一种用于描述器件性能特征的版图结构、制作及测试方法。

2、本发明解决技术问题所采用的技术方案包括:

3、一种用于描述器件性能特征的版图结构,该版图结构的创新点在能够在12个pad中放下14个器件,远远大于传统方法,具体布局结构满足如下条件:

4、①所有设备都使用相同的焊盘badypad(b)。

5、②版图结构中的第一器件nmos1、第三器件nmos3、第五器件nmos5、第七器件nmos7、第九器件nmos9、第十一器件nmos11和第十三器件nmos13共享相同的一个sourcepad(s1)和一个gatepad(g1)。

6、③版图结构中的第二器件nmos2、第四器件nmos4、第六器件nmos6、第八器件nmos8、第十器件nmos10、第十二器件nmos12和第十四器件nmos14共享相同的另一个sourcepad(s2)和另一个gatepad(g2)。

7、④第一器件nmos1和第二器件nmos2共享相同的一个drainpad(d1),同样,第三器件nmos3和第四器件nmos4共享相同的另一个drainpad(d2),依此类推......,第十三器件nmos13和第十四器件nmos14共享相同的另一个drainpad(d7),

8、因此,当测量第一器件nmos1的性能(idsat、idlin、vth...)时,第二器件nmos2处于关闭状态。

9、进一步的在这种方法中,被测器件(dut)的源漏间的泄漏电流可能会受到与其共享源极pad的器件的泄露电流的轻微影响,即使该器件在关闭状态。但是,这种影响很小,并且被测器件的的漏电流可以进一步推导从而被排除掉。

10、一种用于描述器件性能特征的版图结构的制作和测量方法,根据本发明描述的版图结构,虽然能放下14个器件,但是会引入器件source端的寄生电阻,如下图3中加粗线条部分所示。因为加粗线条部分走线过长,在测量中会带来源极的寄生电阻。针对该该部分寄生电阻,本发明提供相应的公式来扣除掉这部分寄生电阻,使得测量值更精确。

11、如图2所示的本发明设计的版图结构,与开尔文结构相比,本发明版图结构中源极的长布线(原理图中的粗线)会在原有的器件电阻之上引入寄生电阻。这种外在寄生电阻将导致测量中的idvd和idvg曲线在很大程度上偏离实际的测量值,因此该版图结构产生的寄生电阻需要额外扣除。为了消除这些电阻,本发明的制作和测量方法具体实现如下:

12、步骤1:计算设计的版图结构中粗布线的寄生电阻。

13、具体寄生电阻的测量方法1:通过手动或脚本来测量版图结构中粗布线路的尺寸w和l;方法2:通过现有软件进行qrc抽取版图结构中粗布线的寄生电阻和电容。

14、进一步的,方法1:寄生电阻r=w*电阻率/l。

15、进一步的,现有的软件包括cadence,calibre。

16、步骤2:基于设计的版图结构,测量每个nmos的idvg和idvd曲线。

17、步骤3:计算步骤2的每个测量点(即nmos)的新idvg和idvd值。

18、步骤4:使用新idvg和idvd值重新绘制idvd和idvg曲线。

19、进一步的,步骤3中每个测量点的新idvg和idvd值,具体计算如下:

20、idvg的计算方法如下:

21、

22、

23、其中,id1是测试数据,通过使用“forcedrain”测试放方法得到,如图4所示。id2是测试数据,通过使用“forcesource”测试放方法得到,如图4所示。vds1是测试条件,通常为0.05v。r是寄生电阻,通过步骤1得到。

24、idvd的计算方法如下:

25、

26、其中,id2是测试数据,通过使用“forcesource”测试放方法得到;rout2是输出电阻:rout2=vds2/id2。vds2是测试条件电压。r是寄生电阻,通过步骤1得到。

27、本发明有益效果如下:

28、1.本发明保护设计的版图结构以及版图制作和测量方法,本发明设计的版图结构能够在12个pad中放下14个器件,相比较现在背景技术中所述的几个方法,在相同面积中可以放下更多的器件结构,数量远远大于这些传统方法。

29、2.本发明测量方法中idvg和idvd的计算公式是本发明根据实际需求,解决寄生电阻设计的公式,且经过本发明测量方法的修正,消除寄生电阻,提高了测试结果精确性。参看图5和图6所示。图5为未修正消除寄生电阻的idvg和idvd曲线,图6为经过本发明方法消除寄生电阻后的idvg和idvd曲线。从图中可以看到,本发明方法能够提高测试结果精确性。

30、3.本发明设计的版图结构相对简单,既解决了方法1测量结果精确但是占用面积,只适合器件建模使用,不能应用在pcm结构中的问题。同时解决了方法2也占用了过多的面积。更解决了方法3能够放下较多的器件,但是会带来较大的源极寄生电阻,影响测试精度。本发明解决了同时提供高测量精度并节省布局空间。

- 还没有人留言评论。精彩留言会获得点赞!