一种高速高压脉冲信号的采集系统的制作方法

本发明涉及一种高速高压脉冲信号的采集方法,特别涉及智能采集控制系统,属于信息采集。

背景技术:

1、脉冲信号是一种不连续的信号,相对于连续信号在整个信号周期内短时间发生,大部分信号周期内没有信号,就像人的脉搏一样。

2、高速高压脉冲信号的不连续性和短时性使得处理高速高压脉冲信号变得挑战性。高速高压脉冲信号的不连续性表现在整个信号周期内并不是持续存在的,而是在某个瞬间发生。高速高压脉冲信号的出现是间断的,不像连续信号那样在整个时间范围内保持存在。

3、高速高压脉冲信号短时性表现在信号持续时间非常短。在信号周期内,只有很小的一部分时间包含有信号,而在大部分信号周期内,高速高压脉冲信号是不存在的。这使得高速高压脉冲信号的能量高度集中在短时间内。

技术实现思路

1、(一)要解决的实际问题

2、本发明目的是提出一种高速高压脉冲信确号的采集系统,该高速高压脉冲信号通过模拟调理电路对输入信号进行调理,再经过adc处理电路后,到主控fpga进行处理,实现数据采集。

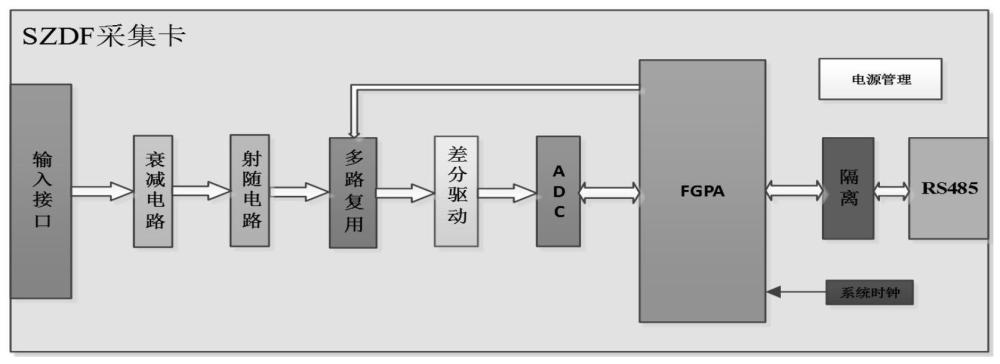

3、由于高速高压脉冲信号的短时性,本发明需要有足够高的采样率来准确捕捉信号的瞬时变化。

4、由于高速高压脉冲信号是瞬时的,本发明系统需要能够迅速响应,以便在信号发生时采取适当的措施。

5、由于高压脉冲信号需要高压处理,本发明需要特殊的电路和设备来处理信号,以防止设备损坏或信号失真。

6、由于高压脉冲信号包含高频成分,本发明采集系统(采集卡)需要具备足够的频率响应能力,以确保捕捉到信号的全部频谱。

7、本发明另一个目的是解决速高压脉冲信号的采集与处理中的系列问题,该系统能够实现高速高压脉冲信号的精确采集及存储。

8、(二)技术方案

9、一种高速高压脉冲信号的采集系统,其特征在于高速高压脉冲信号的采集系统包括fpga单元、衰减电路单元、射随电路单元、多路复用单元、差分驱动单元、adc单元、rs485单元、电源管理单元和系统时钟单元;其中衰减电路单元、射随电路单元、多路复用单元、差分驱动单元、adc单元、fpga单元和rs485单元相互串联连接;

10、所述fpga单元作为模块的核心控制和处理单元,完成输入信号采集、数据处理、模拟开关的控制以及与模块和上位机的通讯功能,采集系统在fgpa单元通过处理系统(ps)和可编程逻辑(pl)之间建立了内部通信通道,这个通道通过内部总线和协议实现;

11、所述衰减电路单元用于将输入的信号调节到adc可接收的范围,确保输入信号不超过adc的输入范围;

12、所述射随电路单元实现较高的输入阻抗,完成射极跟随功能;

13、所述多路复用单元用于将多个通道的输入模拟信号受控依次输出,实现一路adc分时对多通道的输入模拟信号进行采集功能;

14、所述差分驱动单元将多路复用单元输出的模拟信号转换为后级adc采集所需要的差分信号功能;

15、所述adc单元将输入的模拟信号量化转换为数字信号,供后级的fpga进行数字信号处理和测量;

16、所述rs485单元完成上位机与fpga的通讯功能,保证数据的传输和控制;

17、所述电源管理单元提供整个szdf采集卡所需要的全部电源,确保各功能单元正常运行;

18、所述的系统时钟单元提供fpga所需要的时钟信号,保障各功能单元同步工作。

19、所述主控fpga单元作为一个高速互连进行协同工作的核心系统,通过ps部分与pl部分协同实现;

20、所述主控fpga中的ps部分包含处理器系统,包括arm cortex-a9处理器、缓存、片上存储器、外部存储器接口和各种输入/输出外设和接口;所述apu通过高速缓存、片上存储器和外部存储器接口访问数据和指令,能够运行操作系统和应用程序,处理应用层任务。所述外部存储器接口通过连接外部ddr3、ddr3l、ddr2或lpddr2内存,扩展系统存储容量;所述dma控制器通过高效的dma通道实现内存到内存、内存到外设、外设到内存的数据传输管理;所述输入/输出外设和接口提供系统与外部设备的通信接口,包括以太网、usb、can、sd/mmc;

21、所述主控fpga中的pl部分包含可编程逻辑块、dsp块、可编程i/o块、jtag边界扫描、pci express块、串行收发器和两个12位模数转换器;所述clb能够实现特定的逻辑电路,包括查找表、触发器和级联加法器;所述36kb块ram通过配置为双通道18kb块ram,存储中间结果和数据缓存;所述dsp块用于处理音频、图像等数字信号,提供高性能的数字信号处理功能;所述的可编程i/o块支持lvcmos、lvds和sstl等不同电平标准,提供可编程的输入/输出接口;所述pci块支持pci express协议,连接外部设备,实现高速数据传输;所述串行收发器支持高达12.5gb/s的数据传输速率,连接到其他高速设备,获取高速串行通信;所述两个12位模数转换器将模拟信号转换为数字信号,集成在fpga中,获取测量系统环境参数。

22、所述内部总线是一种在芯片内部连接不同功能块的通信系统,这个内部总线用于连接处理系统(ps)和可编程逻辑(pl),允许它们之间传输数据和命令;

23、所述协议是一套规则和约定,用于确保在通信中正确地传递信息,在这里,协议定义了ps和pl之间的通信规则,确保它们能够正确地交换数据和指令;

24、所述内部总线和协议的机制使得处理系统和可编程逻辑能够协同工作,实现数据传输和相互交互通过建立内部总线和采用适当的协议,处理系统(ps)可以向可编程逻辑(pl)发送指令,请求数据,或者将数据传输到pl中进行处理;

25、反过来,pl也可将处理结果传递回ps;该连接机制让系统的各个部分能够共享信息,实现复杂的功能和任务;

26、应用处理单元(application processing unit,apu)通过高速缓存、片上存储器和外部存储器接口来访问数据和指令,从而,内部总线和协议允许apu从不同的存储器位置获取所需的数据和指令,实现ps部分对数据和指令的访问;

27、所述pl部分通过可配置逻辑块(configurable logic blocks,clb)、块ram和dsp块资源,定制特定的逻辑电路,实现各种逻辑功能;从而,内部总线和协议使得pl能够接收来自ps的指令,然后根据这些指令配置逻辑资源,执行相应的逻辑功能;

28、所述输入/输出外设和接口通过内部总线和协议将系统与外部设备连接起来,实现了数据的输入和输出;这包括连接以太网、usb、can外设,通过内部总线传递数据,实现系统与外部设备的通信;

29、pci块和串行收发器通过内部总线和协议实现高速数据传输,连接外部高速设备;pci协议定义了高速数据传输的规范,使得系统能够与支持该协议的外部设备进行可靠的通信;

30、两个12位模数转换器通过内部总线和协议将模拟信号转换为数字信号,用于测量系统环境参数,这表明ps部分可以发送指令给模数转换器,而转换器则通过内部总线将数字化的数据传递回ps进行进一步处理。

31、所述衰减电路单元通过电阻分压网络将信号衰减到±10v的电压范围内,从而得到低压模拟信号,具体包含脉冲信号输入、电阻分压网络、±10v的电压范围、低压模拟信号输出的协同工作;

32、所述衰减电路单元采集模块通过衰减电路单元输入脉冲信号,特点是输入信号具有瞬时性、不连续性,可能在短时间内发生变化;

33、所述脉冲信号通过电阻分压网络,串联连接的电阻实现将输入信号的电压进行分压,将高压信号衰减到一个较低的电压范围;

34、所述衰减后的信号被调整到±10v的电压范围内,确保高速高压脉冲信号的采集系统的其他部分能够有效处理的范围,也避免超过某些组件的工作范围;

35、所述的衰减后的信号将低压模拟信号,用于模拟电路中,为后续处理步骤的输入。

36、所述射随电路单元通过使用高输入阻抗的精密运算放大器opa2810,由晶体管的发射极对输入信号进行放大,输出端提供一个低输出阻抗的跟随信号,将衰减后的模拟信号输出到多路复用单元;

37、所述opa2810运算放大器通过高输入阻抗,电路对外部信号源的影响最小化,确保准确地放大输入信号;确保输入信号不会对电路造成负载,从而减少信号失真;

38、所述opa2810运算放大器针对需要高精度和清晰度的信号,提高输出信号的信噪比;

39、所述opa2810运算放大器通过fet输入结构,提供低输入偏置电流,减少输入信号的误差;

40、所述opa2810运算放大器能够输出接近电源电压的信号,提高了输出信号的线性范围;

41、所述opa2810运算放大器能够减少输出信号的误差,提高信号的精度,具备低失调电压和失调漂移特性;

42、所述opa2810运算放大器能够减少输出信号的失真,提高信号质量;

43、所述opa2810运算放大器中包含高共模抑制比(cmrr),高共模抑制比确保电路对共模噪声的抑制能力强,有助于在电磁干扰环境中提高系统的抗干扰性。

44、所述多路复用单元主要由fpga逻辑控制部分、电荷注入控制部分、电源管理部分和引脚和连接器部分组成,各部分协同工作,通过逻辑控制、模拟开关、电源管理功能,实现对多路输入信号的扫描、选择和输出,从而完成多路复用的功能;fpga通过控制模拟开关的通道,使得其中一个输入信号连接到输出,实现信号的切换和复用;

45、所述fpga逻辑控制部分负责对多路输入信号进行逻辑控制,决定选取哪一个输入信号作为输出,fpga根据内部程序或外部输入的控制信号,生成相应的控制逻辑信号,用于控制模拟开关的通道;

46、所述模拟开关部分(adg1206)作为多路复用单元的关键组成部分,它包含16个独立的模拟开关通道,每个通道都可以与一个模拟信号连接或隔离,这些开关通过逻辑信号(由fpga生成)进行控制,以确定哪个通道处于导通状态,从而选择特定的输入信号进行输出;

47、所述电荷注入控制部分是利用模拟开关的特性,一些电荷注入控制电路,确保在切换过程中不引入显著的电荷,从而确保信号切换的准确性和稳定性;

48、所述电源管理部分负责提供适当的电源给整个多路复用单元,包括fpga和模拟开关;

49、所述多路复用单元的引脚和连接器部分包括与其他系统组件的物理连接,以及与外部环境的接口,这包括adg1206的引脚(28引脚tssop或32引脚5mm×5mm lfcsp)以及fpga的引脚。

50、所述多路复用单元通过fpga进行逻辑控制,对多路输入的信号进行扫描控制输出,实现多路复用功能,具体工作步骤如下:

51、所述多路复用单元可以在不同的时间选择不同的输入信号进行输出,adg1206的低导通电阻和低电荷注入特性有助于减少信号失真,同时其轨至轨操作和逻辑兼容输入;

52、所述多路复用单元由输入信号,逻辑控制,开关动作和输出信号实现;

53、所述输入信号通过多路输入信号连接到adg1206的输入端;

54、所逻辑控制通过fpga产生逻辑控制信号,用于选择要输出的通道;

55、所述开关动作通过逻辑控制信号,使得adg1206中的开关将相应的输入信号连接到输出端;

56、所述输出信号通过被选中的输入信号通过adg1206传递到输出端,实现多路复用功能。

57、所述差分驱动单元使用adi公司的低功耗差分adc驱动器ada4932-1,以及差分驱动单元组成;

58、所述ada4932-1差分放大器,作为差分驱动单元的核心,负责将多路复用单元输出的单端模拟信号转换为后级adc采集所需的差分信号;。

59、所述电源管理部分,提供适当的电源给ada4932-1,确保其正常工作;

60、所述控制接口,用于调整增益、共模电压等参数;

61、所述连接器和引脚,与其他系统组件进行物理连接。

62、所述其他辅助电路,包含滤波器和稳压器,以确保电路的稳定性和性能。

63、所述差分驱动单元实现将多路复用单元输出的模拟信号经差分信号,转换为后级adc采集所需要的信号,由输入信号、增益调整、差分转换、差分信号输出四个步骤执行;其中

64、所述输入信号通过单端模拟信号从差分驱动单元的输入端进入;

65、所述增益调整通过外部可调增益,差分驱动单元可以调整输入信号的增益,以满足后级adc的输入范围要求;

66、所述差分转换差分驱动单元将输入的单端信号转换为差分信号。这可以通过使用两个放大器来实现,一个放大器对输入信号进行反相放大,另一个放大器对输入信号进行同相放大。然后将这两个放大后的信号相减,得到差分信号;

67、所述差分信号输出通过转换后的差分信号从差分驱动单元的输出端输出,供后级adc进行采集。

68、所述adc(模数转换器)单元,通过模拟信号通过差分输入进入adc芯片,在芯片上内置了基准电压源和采样保持电路,用于提供参考电压和在采样期间保持输入信号的值,从而实现将模拟信号转换为数字信号;

69、所述adc(模数转换器)单元需要时钟信号控制采样;所述的时钟占空比稳定器用于确保时钟信号的占空比稳定,以提高采样精度,采样后的模拟信号被转换为数字信号,这个过程通过比较输入信号与基准电压来确定每个采样时刻的数字值;

70、所述adc的分辨率由位数决定,adc能够将输入信号分为214(16384)个不同的等级,14位能够提供更高的精度和动态范围;

71、所述adc的采样率可以在20msps(每秒百万次采样)至80msps之间进行选择,采样率越高,能够捕捉到的高频信号就越准确;

72、所述adc采样过程中,在不同的采样率条件下,功耗也会有所不同,优化电路设计和工作模式实现。例如在80msps时为366mw,在20msps时为90mw;

73、所述adc通过将模拟信号转换为数字信号,提供高精度、高速和低功耗的特点,适用于各种需要模数转换的应用,如信号处理、数据采集和通信系统;

74、所述adc(模数转换器)由输入接口、基准电压源、时钟控制单元、比较器、数字输出接口组成;其中

75、输入接口是通过差分输入/单端输入,允许连接差分信号或单端信号,提供灵活的输入选项;输入接口需要保持电路,在采样期间保持输入信号的值,确保在采样时刻获取稳定的输入值。

76、基准电压源提供稳定的基准电压,是adc进行转换时的参考;

77、时钟控制单元包括时钟信号和占空比稳定器;其所述时钟信号通过控制采样过程的时钟信号,决定采样的时机,其所述占空比稳定器能够确保时钟信号的占空比稳定,以提高采样精度;

78、比较器能够将输入信号与基准电压进行比较,确定每个采样时刻的数字值。

79、数字输出接口能够提供数字信号的输出,通常以并行或串行的形式。

80、所述adc(模数转换器)单元通过采样、量化、编码、转换实现模拟信号转换为数字信号,其中

81、采样通过adc以预定的采样率对输入的模拟信号进行采样。采样过程将连续的模拟信号在时间上离散化,得到一系列的采样点;

82、所述量化通过对采样点的幅度进行量化,将其转换为有限数量的离散数值。量化过程将连续的模拟幅度值映射到一组预定的数字值。通常,adc具有一定的分辨率,例如14位,表示它可以将输入信号量化为214(16384)个不同的数字值;

83、所述编码通过将量化后的数字值编码为特定的数字格式,例如二进制或偏移二进制,编码格式决定了数字信号如何表示和传输;

84、所述转换通过adc将编码后的数字信号转换为数字输出。这个数字输出可以是并行数据(多个位同时输出)或串行数据(一位一位地输出)。

85、本发明有益的技术效果和工作原理如下:

86、第一,采用fpga进行脉冲信号采集。传统操作可能无法有效采集信号,而本发明通过使用脉冲(fgpa)实现了信号的采集。fpga以硬件电路设计为基础,以并行方式工作,具有较快的运行速度,相较于cpu和arm,fpga具备更快的计算速度,尤其在计算强度较高的应用中具有优势。其高灵活性、低成本和快速计算的特点,使其在通讯、视频处理、高性能计算以及控制系统等领域中发挥着关键作用。

87、第二,阻抗匹配。采用衰减电路和射随电路实现高输入阻抗匹配。在高压信号输入之前,通过衰减电路将信号衰减到adc采集单元范围内的电压值,以防止芯片损坏。射随电路作为电压跟随器,通过保持高输入阻抗和低输出阻抗,确保衰减后的信号准确送达后端进行处理。

88、第三,差分驱动减少测量误差。为减小测量误差,采用差分驱动,将单端模拟信号转换为后续adc采集所需的差分信号。差分信号具有强大的抗干扰能力,能有效抑制电磁干扰(emi),并确保时序定位的准确性。

89、第四,eeprom校准参数。引入eeprom用于静态数据存储,如校准数据和上电初始状态保存。通过调整修正参数(y=kx+b,其中k为倍数,b为静态误差),可以在存在较大误差时保障测量精度。

90、第五,触发电平设置避免脉冲误采。为防止脉冲误采,设置了trigh和trighl触发电平。只有当信号超过触发电平时,才记录数据。这样的设置允许根据采集数据的强度来精确捕捉所需的信号,避免记录不必要的信息。

- 还没有人留言评论。精彩留言会获得点赞!