芯片测试装置及芯片的制作方法

本申请涉及半导体,尤其涉及一种芯片测试装置及芯片。

背景技术:

1、目前,在射频芯片量产测试领域,大批量芯片在发货前需要用芯片测试装置来验证其是否符合性能指标。

2、但受到现有的芯片测试装置的结构限制,芯片测试装置的性能不能满足要求。

技术实现思路

1、本申请实施例提供一种芯片测试装置及芯片,通过设置输出电抗补偿结构,且输出电抗补偿结构和第一连接部和/或第二连接部连接,可以降低第一连接部带来的寄生电感引起的变大虚部阻抗,并将芯片输出端至第一连接部之间的连接部分(例如微带线)的影响消除,提前将阻抗牵引至易于匹配位置。

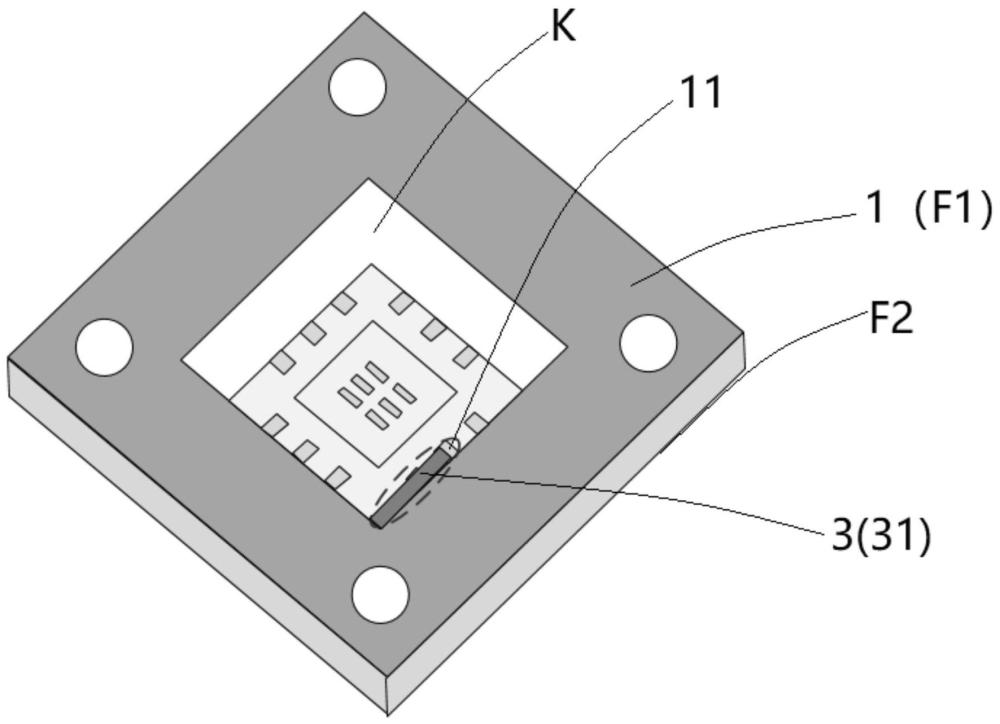

2、一方面,根据本申请实施例提出了一种芯片测试装置,包括:底座结构,所述底座结构包括相对的第一表面和第二表面,在所述第一表面设有用于容纳芯片的槽体,所述槽体内设有用于和所述芯片的输出引脚电连接的第一连接部;电路板,设于所述底座结构的所述第二表面一侧,且所述电路板包括和所述第一连接部连接的第二连接部;输出电抗补偿结构,设于所述底座结构、所述电路板中的至少一者上,且所述输出电抗补偿结构和所述第一连接部和/或所述第二连接部连接。

3、根据本申请实施例的一个方面,所述输出电抗补偿结构包括电容结构,所述电容结构包括第一极板和第二极板,所述第一极板和所述第二极板分别设于所述底座结构、所述电路板中的一者;或,所述第一极板和所述第二极板均设于所述底座结构或所述电路板。

4、根据本申请实施例的一个方面,所述第一表面设有和所述第一连接部电连接的第一微带线,所述第二表面设有和所述第一微带线相对设置的第二微带线,所述输出电抗补偿结构包括所述第一微带线和所述第二微带线。

5、根据本申请实施例的一个方面,所述电路板设有接地过孔,所述接地过孔和所述第二微带线相连。

6、根据本申请实施例的一个方面,所述第一微带线在所述第一表面的正投影覆盖所述第二微带线在所述第一表面的正投影。

7、根据本申请实施例的一个方面,所述第二表面设有第二微带线,所述第二微带线和所述第一连接部电连接;所述电路板包括本体部以及接地底板,所述接地底板设于所述本体部背离所述底座结构一侧,在沿垂直于所述第一表面的方向上,所述接地底板和所述第二微带线至少部分交叠,所述输出电抗补偿结构包括所述第二微带线和所述接地底板。

8、根据本申请实施例的一个方面,所述第二表面设有第二微带线,所述电路板朝向所述第二表面一侧设有第三微带线,所述第二微带线和所述第三微带线相连接;所述电路板包括本体部以及接地底板,所述接地底板设于所述本体部背离所述底座结构一侧,在沿垂直于所述第一表面的方向上,所述接地底板和所述第二微带线、所述第三微带线中至少一者部分交叠,所述输出电抗补偿结构包括所述第二微带线、所述第三微带线和所述接地底板。

9、根据本申请实施例的一个方面,所述电路板朝向所述第二表面一侧设有第三微带线,所述第三微带线和第二连接部电连接;所述电路板包括本体部以及接地底板,所述接地底板设于所述本体部背离所述底座结构一侧,在沿垂直于所述第一表面的方向上,所述接地底板和所述第三微带线至少部分交叠,所述输出电抗补偿结构包括所述第三微带线和所述接地底板。

10、根据本申请实施例的一个方面,所述第三微带线的长度可调节设置。

11、本发明实施例还提供了一种芯片,包括:采用上述任一实施例中的芯片测试装置进行测试。

12、根据本申请实施例的芯片测试装置,本发明实施例所提供的芯片测试装置包括底座结构、电路板以及输出电抗补偿结构,在本实施例中,芯片的输出引脚需要和底座结构的第一连接部连接后,再和电路板的第二连接部连接,以通过电路板对芯片进行控制测试,本实施例通过设置输出电抗补偿结构,且输出电抗补偿结构和第一连接部和/或第二连接部连接,可以降低第一连接部带来的寄生电感引起的变大虚部阻抗,并将芯片输出端至第一连接部之间的连接部分(例如微带线)的影响消除,提前将阻抗牵引至易于匹配位置。

技术特征:

1.一种芯片测试装置,其特征在于,包括:

2.根据权利要求1所述的芯片测试装置,其特征在于,所述输出电抗补偿结构包括电容结构,所述电容结构包括第一极板和第二极板,所述第一极板和所述第二极板分别设于所述底座结构、所述电路板中的一者;或,

3.根据权利要求1所述的芯片测试装置,其特征在于,所述第一表面设有和所述第一连接部电连接的第一微带线,所述第二表面设有和所述第一微带线相对设置的第二微带线,所述输出电抗补偿结构包括所述第一微带线和所述第二微带线。

4.根据权利要求3所述的芯片测试装置,其特征在于,所述电路板设有接地过孔,所述接地过孔和所述第二微带线相连。

5.根据权利要求3所述的芯片测试装置,其特征在于,所述第一微带线在所述第一表面的正投影覆盖所述第二微带线在所述第一表面的正投影。

6.根据权利要求1所述的芯片测试装置,其特征在于,所述第二表面设有第二微带线,所述第二微带线和所述第一连接部电连接;

7.根据权利要求1所述的芯片测试装置,其特征在于,所述第二表面设有第二微带线,所述电路板朝向所述第二表面一侧设有第三微带线,所述第二微带线和所述第三微带线相连接;

8.根据权利要求1所述的芯片测试装置,其特征在于,所述电路板朝向所述第二表面一侧设有第三微带线,所述第三微带线和第二连接部电连接;

9.根据权利要求8所述的芯片测试装置,其特征在于,所述第三微带线的长度可调节设置。

10.一种芯片,其特征在于,包括:采用权利要求1至9任一项所述的芯片测试装置进行测试。

技术总结

本申请涉及一种芯片测试装置及芯片,芯片测试装置包括:底座结构,底座结构包括相对的第一表面和第二表面,在第一表面设有用于容纳芯片的槽体,槽体内设有用于和芯片的输出引脚电连接的第一连接部;电路板,设于底座结构的第二表面一侧,且电路板包括和第一连接部连接的第二连接部;输出电抗补偿结构,设于底座结构、电路板中的至少一者上,且输出电抗补偿结构和第一连接部和/或第二连接部连接。通过设置输出电抗补偿结构,且输出电抗补偿结构和第一连接部和/或第二连接部连接,可以降低第一连接部带来的寄生电感引起的变大虚部阻抗,并将芯片输出端至第一连接部之间的微带线的影响消除,提前将阻抗牵引至易于匹配位置。

技术研发人员:卞成玺,刘昊宇,杨梦苏

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!