基于JC-3155的数字集成电路通用测试适配器的制作方法

本技术属于电子器件测试设备,具体涉及基于jc-3155的数字集成电路通用测试适配器。

背景技术:

1、现有技术存在的问题是:由于设备资源的限制,最多可提供48路数字通道,适用于引线数较少的中小规模集成电路。为满足中小规模电路测试需要,增加了外围元件,由于增加控制电路与开关元件,导致测试量值引入了其他因素的不确定度。

2、一般来说,测试系统上的测试适配器是针对某一种型号的集成电路来设计的,因为每一种集成电路的管脚定义与功能都可能不一样,比如有的集成电路1脚为工作电源供电脚,而有的就可能为接地脚,为此开发人员需要根据集成电路的管脚定义和功能要求在测试平台上去设计一款测试适配器,导致测试适配器的兼用性会相当低,为测试带来了相当多的时间成本与经济成本,为此,设计出一款这样兼容性广泛的测试适配器是很有必要的。

技术实现思路

1、为解决现有技术中存在的上述问题,本实用新型提供了基于jc-3155的数字集成电路通用测试适配器,将所有的基于jc3155的资源集中在一块板上,使用方便,快捷,缩短了测试时间,节约了成本的特点。

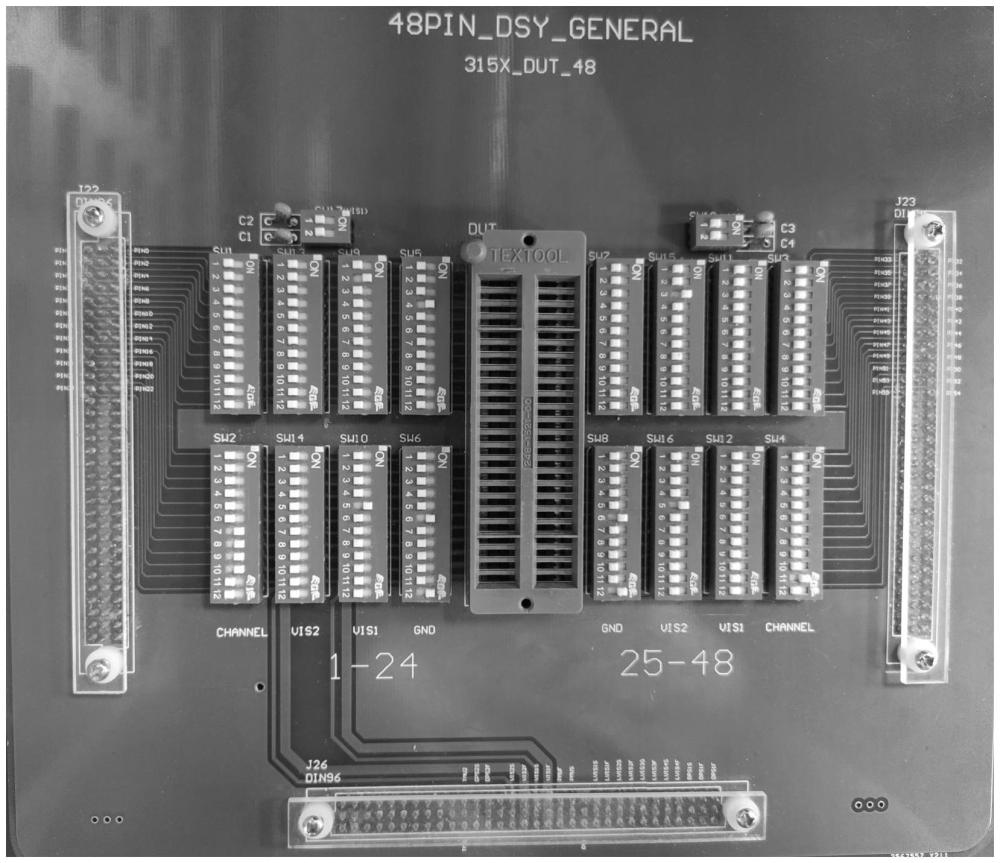

2、为实现上述目的,本实用新型提供如下技术方案:基于jc-3155的数字集成电路通用测试适配器,包括功能电路和拨码开关,拨码开关一端与适配器中央通道相连接,另一端与数字通道的输出管脚相连接,通过拨码开关的连接来控制数字通道的信号与适配器的通道相连接,通过16组拨码开关,可以使适配器中央通道任意的管脚连接到测试机台的48个数字通道、设备gnd或两路vis电压电流源上。

3、作为本实用新型的基于jc-3155的数字集成电路通用测试适配器优选技术方案,设备的供电与控制电路的加电都是由设备的程控电源来控制的,同时将设备的固定资源连接到对应的通道都已封装成子程序。

4、作为本实用新型的基于jc-3155的数字集成电路通用测试适配器优选技术方案,在系统数字通道的正常供电下,通过测试适配器与拨码开关使所需资源施加到器件管脚上,进而控制设备资源与被测器件的连接。

5、作为本实用新型的基于jc-3155的数字集成电路通用测试适配器优选技术方案,数字通用板是通过程控加电来控制资源与管脚的连接。

6、作为本实用新型的基于jc-3155的数字集成电路通用测试适配器优选技术方案,数字通用板上可调用电源类型有精密测量电源pmu,稳压电源vis1、vis2,48路数字信号以及地脚agnd。

7、与现有技术相比,本实用新型的有益效果是:

8、本实用新型将所有的基于jc3155的资源集中在一块板上,大幅度降低了测试适配器成本,也大幅度减少了中小规模集成电路的程序开发时间,与行业中大部分的中小数字集成电路都可兼容,几乎可覆盖中小规模数字集成电路的直流电参数测试及功能测试,使用方便,快捷,缩短了测试时间,节约了成本。

技术特征:

1.基于jc-3155的数字集成电路通用测试适配器,包括功能电路和拨码开关,其特征在于:拨码开关一端与适配器中央通道相连接,另一端与数字通道的输出管脚相连接,通过拨码开关的连接来控制数字通道的信号与适配器的通道相连接,通过16组拨码开关,可以使适配器中央通道任意的管脚连接到测试机台的48个数字通道、设备gnd或两路vis电压电流源上。

2.根据权利要求1所述的基于jc-3155的数字集成电路通用测试适配器,其特征在于:设备的供电与控制电路的加电都是由设备的程控电源来控制的,同时将设备的固定资源连接到对应的通道都已封装成子程序。

3.根据权利要求1所述的基于jc-3155的数字集成电路通用测试适配器,其特征在于:在系统数字通道的正常供电下,通过测试适配器与拨码开关使所需资源施加到器件管脚上,进而控制设备资源与被测器件的连接。

4.根据权利要求1所述的基于jc-3155的数字集成电路通用测试适配器,其特征在于:数字通用板是通过程控加电来控制资源与管脚的连接。

5.根据权利要求1所述的基于jc-3155的数字集成电路通用测试适配器,其特征在于:数字通用板上可调用电源类型有精密测量电源pmu,稳压电源vis1、vis2,48路数字信号以及地脚agnd。

技术总结

本技术属于电子器件测试设备技术领域,尤其为基于JC‑3155的数字集成电路通用测试适配器,包括功能电路和拨码开关,拨码开关一端与适配器中央通道相连接,另一端与数字通道的输出管脚相连接,通过拨码开关的连接来控制数字通道的信号与适配器的通道相连接,通过16组拨码开关,可以使适配器中央通道任意的管脚连接到测试机台的48个数字通道、设备GND或两路VIS电压电流源上,本技术将所有的基于JC3155的资源集中在一块板上,使用方便,快捷,缩短了测试时间,节约了成本。

技术研发人员:王登辉

受保护的技术使用者:西安环宇芯微电子有限公司

技术研发日:20230811

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!