一种基于双多路门控环形振荡器的再量化时间数字转换器

1.本发明属于数模混合电路领域,具体涉及一种基于双多路门控环形振荡器的再量化时间数字转换器。

背景技术:

2.数字锁相环(dpll)在无线频率合成器和有线应用时钟恢复设计中是传统模拟锁相环的一个有吸引力的替代方案,可以缩小所需的芯片尺寸并且可用于数字密集型校准和调制。通常数字锁相环采用部分数字或全数字,使用时间数字转换器(time-to-digital converter,tdc)代替鉴相器,而数字锁相环的带内噪声主要为时间数字转换器引入的量化噪声。因此,时间数字转换器如何降低量化噪声成为了低噪声数字锁相环的关键之一,通常方法有提高时间分辨率以及提高线性度两种。

3.学术界在2007年提出了基于门控环形振荡器(gated-ring-oscillator,gro)的时间数字转换器,这种结构只允许振荡器在给定的测量期间发生振荡,并努力冻结测量之间的环形振荡器状态,测量一个测量间隔内延迟单元转换的次数。出于提高时间分辨率的需要,在2008年提出了基于多路门控环形振荡器(multi-path gro)的时间数字转换器,由于使用了多路输入的反相器,降低了每级的延时,从而可以实现皮秒量级的时间分辨率。然而对于低噪声数字锁相环而言,皮秒级的量化误差仍有待降低。

技术实现要素:

4.本发明的目的在于,针对背景技术存在的缺陷,提出了一种基于双多路门控环形振荡器的再量化时间数字转换器。本发明通过对两个多路门控环形振荡器的量化误差进行再次量化,实现时间分辨率的提高。

5.为实现上述目的,本发明采用的技术方案如下:

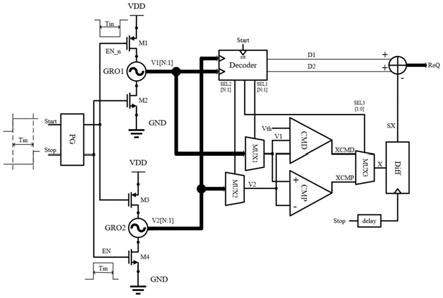

6.一种基于双多路门控环形振荡器的再量化时间数字转换器,包括脉冲产生电路(pg)、第一门控环形振荡器(gro1)、第二门控环形振荡器(gro2)、再量化电路和数据修正电路,其中,所述再量化电路由译码器(decoder)、第一多路复用器(mux1)、第二多路复用器(mux2)、第三多路复用器(mux3)、比较器(cmp)、共模检测电路(cmd)组成,所述数据修正电路由一阶差分电路(diff)、延时电路(delay)、加法器组成;

7.开始信号start和停止信号stop输入脉冲产生电路,脉冲产生电路将开始信号start和停止信号stop上升沿的输入时间差tin转化为脉宽等于tin的高电平脉冲en和脉宽等于tin的低电平脉冲en_n;高电平脉冲en输入第二nmos管m2和第四nmos管m4,低电平脉冲输入第一pmos管m1和第三pmos管m3,第一门控环形振荡器通过第一pmos管m1连接电源信号vdd、通过第二nmos管m2接地,第二门控环形振荡器通过第三pmos管m3连接电源信号vdd、通过第四nmos管m4接地;第一门控环形振荡器在使能信号en为高电平、en_n为低电平时开始振荡,输出n个在高低电平之间不断翻转的第一振荡波形v1[n:1];第二门控环形振荡器在使能信号en为高电平、en_n为低电平时开始振荡,输出n个在高低电平之间不断翻转的第二

振荡波形v2[n:1];第一振荡波形v1[n:1]分别输入译码器(decoder)和第一多路复用器(mux1),第二振荡波形v2[n:1]分别输入译码器(decoder)和第二多路复用器(mux2);译码器的复位端连接开始信号start,在开始信号start上升沿时译码器将所有输出复位为0,并对第一振荡波形v1[n:1]中所有波形的翻转次数进行计数得到输出d1,对第二振荡波形v2[n:1]中所有波形的翻转次数进行计数得到输出d2;当第一门控环形振荡器和第二门控环形振荡器处于暂停状态时,根据第一门控环形振荡器和第二门控环形振荡器未翻转的相邻反相器的状态,输出第一选择信号sel1[n:1]控制第一多路复用器,输出第二选择信号sel2[n:1]控制第二多路复用器,输出第三选择信号sel3[1:0]控制第三多路复用器;第一多路复用器根据第一选择信号sel1[n:1]选择第一振荡波形v1[n:1]中对应地址的信号并输出,记为v1;第二多路复用器根据第二选择信号sel2[n:1]选择第二振荡波形v2[n:1]中对应地址的信号并输出,记为v2;共模检测电路(cmd)检测输入信号v1和v2的共模电压,若共模电压高于预设阈值电压vth则输出信号xcmd为高电平,反之xcmd为低电平;比较器比较输入信号v1和v2的电压,若v1高于v2则输出信号xcmp为高电平,反之xcmp为低电平;第三多路复用器根据第三选择信号sel3[1:0],选择输出xcmd或xcmp或对xcmp取反,记为输出信号x;延时电路(delay)对停止信号stop进行延时后作为时钟信号输入到一阶差分电路(diff);一阶差分电路对输出信号x进行一阶差分得到输出sx;加法器将译码器输出的d1和d2相加后、再减去输出sx,即可得到最终的输出信号req。

[0008]

进一步的,第一门控环形振荡器和第二门控环形振荡器处于暂停状态时,第一门控环形振荡器和第二门控环形振荡器中都存在输出同相电平的相邻两个反相器,该相邻两个反相器的输出电平同为低电平或者同为高电平,对应门控环形振荡器分别记作0状态(同为低电平)或者1状态(同为高电平);第一门控环形振荡器中输出同相电平的相邻两个反相器的电压分别记为v1i和v1

i+1

,第二门控环形振荡器中输出同相电平的相邻两个反相器的电压分别记为v2i和v2

i+1

;当第一门控环形振荡器处于0状态、第二门控环形振荡器处于0状态时,第一多路复用器的输出信号v1为v1i、第二多路复用器的输出信号v2为v2

i+1

、第三多路复用器的输出信号x为xcmp取反;当第一门控环形振荡器处于0状态、第二门控环形振荡器处于1状态时,第一多路复用器的输出信号v1为v1

i+1

、第二多路复用器的输出信号v2为v2i、第三多路复用器的输出信号x为xcmd;当第一门控环形振荡器处于1状态、第二门控环形振荡器处于0状态时,第一多路复用器的输出信号v1为v1i、第二多路复用器的输出信号v2为v2

i+1

、第三多路复用器的输出信号x为xcmd;当第一门控环形振荡器处于1状态、第二门控环形振荡器处于1状态时,第一多路复用器的输出信号v1为v1i、第二多路复用器的输出信号v2为v2

i+1

、第三多路复用器的输出信号x为xcmp。具体如下表所示:

[0009]

gro1、gro2状态mux1、mux2输出v1、v2mux3输出xgro1 0状态,gro2 0状态v1i,v2

i+1

xcmp取反gro1 0状态,gro2 1状态v1

i+1

,v2ixcmdgro1 1状态,gro2 0状态v1i,v2

i+1

xcmdgro1 1状态,gro2 1状态v1i,v2

i+1

xcmp

[0010]

进一步的,所述第一门控环形振荡器和第二门控环形振荡器为电路结构完全相同的多路门控环形振荡器,通过控制内部反相器晶体管的宽长比,使第一门控环形振荡器和第二门控环形振荡器的反相器的延时不同。

[0011]

进一步的,所述第一多路复用器和第二多路复用器为模拟多路复用器,第三多路复用器为数字多路复用器。

[0012]

本发明提供的一种基于双多路门控环形振荡器的再量化时间数字转换器,工作原理为:输入时间差tin经过第一门控环形振荡器和第二门控环形振荡器后分别产生两个蕴含在振荡器输出波形中的量化误差q1、q2,以及通过译码器产生的两个整数d1、d2;每个门控环形振荡器的量化误差信息包含在输出同相电平的相邻两个反相器的输出电压波形vi、v

i+1

中,该两个反相器的输出电平同为低电平或者同为高电平,对应门控环形振荡器分别记作0状态或者1状态,如图2及图3所示,其量化误差可以表示为:(0状态)或(0状态)或(1状态);

[0013]

当输入时间误差为t

in

[n],第一门控环形振荡器的每级反相器延时为第二门控环形振荡器的每级反相器延时为则第一门控环形振荡器在测量时间内发生的电平翻转次数d1[n]等于t

in

[n]除以其每级反相器延时,再减去量化误差q1[n]的一阶整形;第二门控环形振荡器在测量时间内发生的电平翻转次数d2[n]等于t

in

[n]除以其每级反相器延时,再减去量化误差q2[n]的一阶整形:

[0014]

d1[n]=(k-δk)*t

in

[n]-q1[n]+q1[n-1]

[0015]

d2[n]=(k+δk)*t

in

[n]-q2[n]+q2[n-1]

[0016]

两者相加得到的初步数据d[n]为:

[0017]

d[n]=2k*t

in

[n]-(q1[n]+q2[n])+(q1[n-1]+q2[n-1])

[0018]

由于d[n]约为d1[n]和d2[n]的两倍,可以将其近似看作时间分辨率提高一倍;但此时的量化误差也随之提高一倍,有效分辨率并没有改善一倍,需要用再量化电路和数据修正电路消除一半量化误差;

[0019]

在第n次测量时,第一门控环形振荡器和第二门控环形振荡器的量化误差为:

[0020][0021][0022]

再量化电路再次量化得到的整数x[n]为:

[0023][0024]

最后将x[n]经一阶差分后从初步数据d[n]中减去,整体量化误差下降为与q1[n]、q2[n]的方差同为1/12;从而使其最小可分辨时间变为传统基于单个多路门控环形振荡器的时间数字转换器的一半,有效位数增加一位。

[0025]

本发明的有益效果为:

[0026]

本发明通过将两个存在失配的基于多路门控环形振荡器的时间数字转换器输出进行相加,然后对两者量化误差之和再次量化后进行消除,从而使其等价于一个最小可分

辨时间为原来一半的时间数字转换器。相比目前基于单个多路门控环形振荡器的时间数字转换器,其环形振荡器每级延迟时间已接近设计极限;本发明则通过再次量化的方式,可以在不降低环形振荡器每级反相器延迟时间的前提下提升时间分辨率至原来两倍。

附图说明

[0027]

图1为本发明提出的基于双多路门控环形振荡器的再量化时间数字转换器原理图;

[0028]

图2为门控环形振荡器暂停时处在0状态的量化误差示意图;

[0029]

图3为门控环形振荡器暂停时处在1状态的量化误差示意图;

[0030]

图4为本发明实施例1的基于双多路门控环形振荡器的再量化时间数字转换器及相应的测试电路原理图;

[0031]

图5为本发明实施例1的部分内部信号时序图。

具体实施方式

[0032]

为使本发明的目的、技术方案和优点更加清晰,结合以下具体实施例,并参照附图,对本发明做进一步的说明。

[0033]

下述非限制性实施例可以使本领域的普通技术人员更全面的理解本方明,但不以任何方式限制本发明。

[0034]

实施例1

[0035]

本实施例提供了一种基于双多路门控环形振荡器的再量化时间数字转换器。如图1所示,包括脉冲产生电路(pg)、第一门控环形振荡器(gro1)、第二门控环形振荡器(gro2)、译码器(decoder)、第一多路复用器(mux1)、第二多路复用器(mux2)、第三多路复用器(mux3)、比较器(cmp)、共模检测电路(cmd)、一阶差分电路(diff)、延时电路(delay)、加法器;

[0036]

第一门控环形振荡器每级反相器延时为1/0.955ps,第二门控环形振荡器每级反相器延时为1/1.045ps,两者可以看作是在设计时由每级反相器延时为1ps的门控振荡器通过正反方向的微调而产生;

[0037]

译码器(decoder)、第一多路复用器(mux1)、第二多路复用器(mux2)、第三多路复用器(mux3)、比较器(cmp)、共模检测电路(cmd)组成的再量化电路根据第一门控环形振荡器和第二门控环形振荡器暂停时的四种不同状态进行相应处理,得到输出x;

[0038]

最后,一阶差分电路对输出x做一阶差分得到sx;对d1和d2相加后再减去sx,消除整体量化误差为原来的一半,从而使其时间分辨率提高一倍;

[0039]

如图4所示,为本发明实施例1的基于双多路门控环形振荡器的再量化时间数字转换器及相应的测试电路原理图;输入时间误差为233.3ps,gro1增益为0.955t lsb/ps,gro2增益为1.045t lsb/ps,测试电路中的gro3增益为2tlsb/ps。如图5所示,gro1、gro2、gro3产生的测量数据和量化误差分别为d1、d2、dk和q1、q2、qk,再次量化得到的整数为x,经过一阶差分后变为sx,最后从d1+d2中减去sx得到的最终数据req与dk完全相等。

[0040]

因此所述基于双多路门控环形振荡器的再量化时间数字转换器等价于一个最小可分辨时间为0.5ps/lsb的时间数字转换器,相比最小可分辨时间约为1ps/lsb的基于单个

多路门控环形振荡器的时间数字转换器,可见通过再次量化的方式,本发明可以在不降低环形振荡器每级反相器延迟时间的前提下提升时间分辨率至原来两倍。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1